標題

????????ROM(Read-Only Memory,只讀存儲器)是一種在FPGA(Field-Programmable Gate Array,現場可編程門陣列)中常用的存儲器類型。與RAM(Random Access Memory,機存取存儲器)不同,ROM的內容在制造過程中被預先編程,并且無法在運行時修改。

? ? ? ? 1 :ROM通常用于存儲固定的程序代碼、常量數據或查找表等,因為它們具有不可變的特性。它的主要特點包括:

? ? ? ? ?①:只讀性:ROM中的數據在制造過程中被寫入,一旦編程完成,就無法進行修改。這確保了數據的安全性和穩定性;

? ? ? ? ?②:非易失性:ROM中的數據在斷電或重啟后仍然保持不變,不會丟失。這是與RAM的一個重要區別;

? ? ? ? ?③:高密度:ROM具有較高的存儲密度,因為它可以在硬件級別上實現,而不需要像RAM那樣用傳統的邏輯門來實現。

? ? ? ? 2:FPGA中通常會使用不同類型的ROM,包括:

? ? ? ? ?①:M4K(Memory 4K):這是Xilinx FPGA系列中常見的一種ROM資源,可以存儲4K個數據位。M4K ROM具有靈活的讀寫接口和配置選項,可以滿足不同應用的需求;

? ? ? ? ?②:Block RAM:FPGA中的Block RAM也可以用作ROM,通過在初始化時將數據加載到Block RAM中來實現。Block RAM通常具有較大的存儲容量和更高的讀寫速度;

使用ROM的好處是可以提高系統的性能和資源效率,特別是對于一些不需要在運行時修改的數據和代碼。但是,由于ROM的內容無法修改,因此對于需要動態更新的數據,需要使用其他類型的存儲器,如RAM。

簡介

FPGA中的ROM(Read-Only Memory,只讀存儲器)起源于計算機系統中的存儲器技術。在早期的計算機系統中,ROM被用于存儲固定的程序代碼和常量數據,以及用于查找表和數據轉換等應用。隨著FPGA技術的發展,ROM成為了FPGA設計中常用的一種存儲器類型。與傳統的硬件設計相比,FPGA具有可編程性的優勢,可以根據特定的應用需求進行靈活的配置和重新編程。在FPGA中,ROM的設計和實現方式通常是通過在硬件級別上配置邏輯電路來實現。它可以在FPGA芯片制造過程中被預先編程,也可以在設計過程中使用特定的工具和語言來描述和生成ROM的內容。ROM在FPGA設計中具有多種應用,包括存儲固定的程序代碼、常量數據、查找表和數據轉換等。由于ROM具有只讀性和非易失性的特點,它可以提供穩定和安全的存儲,同時具有較高的存儲密度和快速的讀取速度。這使得ROM成為了一種重要的存儲器類型,被廣泛應用于FPGA設計中的不同領域,如數字信號處理、通信系統、圖像處理和嵌入式系統等。

正文

????????引言

-

存儲常量數據:ROM常用于存儲常量數據,如查找表、預先計算的數學函數值、校正數據等。這些數據在設計過程中是固定的,不需要在運行時進行修改;

-

存儲程序代碼:在一些應用中,特定的程序代碼可以被預先存儲在ROM中。這樣可以節省FPGA的邏輯資源,并且可以提高系統的性能和響應時間;

-

替代邏輯電路:FPGA中的ROM可以替代一些邏輯電路的功能,特別是對于復雜的查找表和數據轉換。使用ROM可以簡化設計,并且可以提供更高的性能和資源效率;

-

快速數據存取:由于ROM具有快速的讀取特性,它常用于需要快速存取數據的應用,如數字信號處理、圖像處理和通信系統等;

-

存儲初始化數據:在FPGA設計中,ROM可以用于存儲初始化數據,如啟動配置、初始化寄存器值等。這些數據在設備上電時被加載到相應的寄存器中,用于初始化系統狀態;

-

安全存儲:ROM中的數據是只讀的,無法被修改。這使得ROM成為存儲安全相關數據的理想選擇,如加密密鑰、安全配置等。

總而言之,FPGA中的ROM提供了一種靈活、高性能和資源高效的存儲器選項,可用于存儲常量數據、程序代碼、查找表和初始化數據等。它在各種應用領域中發揮著重要的作用,使得FPGA設計更加靈活和高效。

????????主體

? ? ? ? 使用中科億海微eLinx開發工具進行編程:

? ? ? ? ①:以下是使用Verilog開發一套ROM(軟核)的示例代碼:

module ROM (input wire [N-1:0] address,output wire [M-1:0] data

);reg [M-1:0] rom [0:(2**N)-1];initial beginrom[0] = 8'b00000000;rom[1] = 8'b00000001;// ...rom[(2**N)-1] = 8'b11111111;endassign data = rom[address];endmodule

在這個示例中,我們定義了一個名為ROM的模塊,該模塊具有一個輸入端口address(用于指定ROM中的地址)和一個輸出端口data(用于輸出對應地址的數據)。

在模塊內部,我們使用reg類型的數組rom來表示ROM的存儲單元。數組的大小為2的N次方,其中N是地址位寬。例如,如果地址位寬為8位,則數組大小為256。

在initial塊中,我們可以初始化rom數組中的數據。根據您的需求,將存儲在ROM中的數據寫入到rom數組的相應位置。在示例中,我們使用8位寬的數據,每個地址存儲一個8位的字節。

最后,我們使用assign語句將rom數組中對應地址的數據賦值給輸出端口data。

請注意,這只是一個簡單的示例,用于說明如何使用Verilog開發一套ROM的軟核。實際的ROM設計可能需要更多的功能和控制邏輯,例如讀取使能、寫使能、讀寫時序等。具體的設計取決于您的需求和目標平臺。

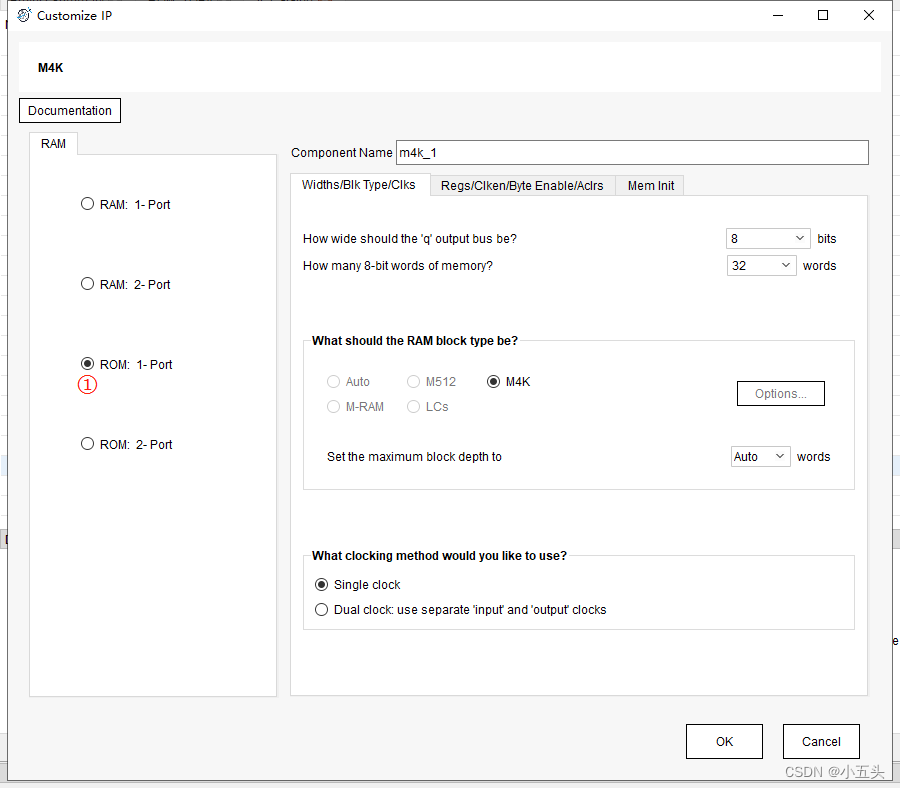

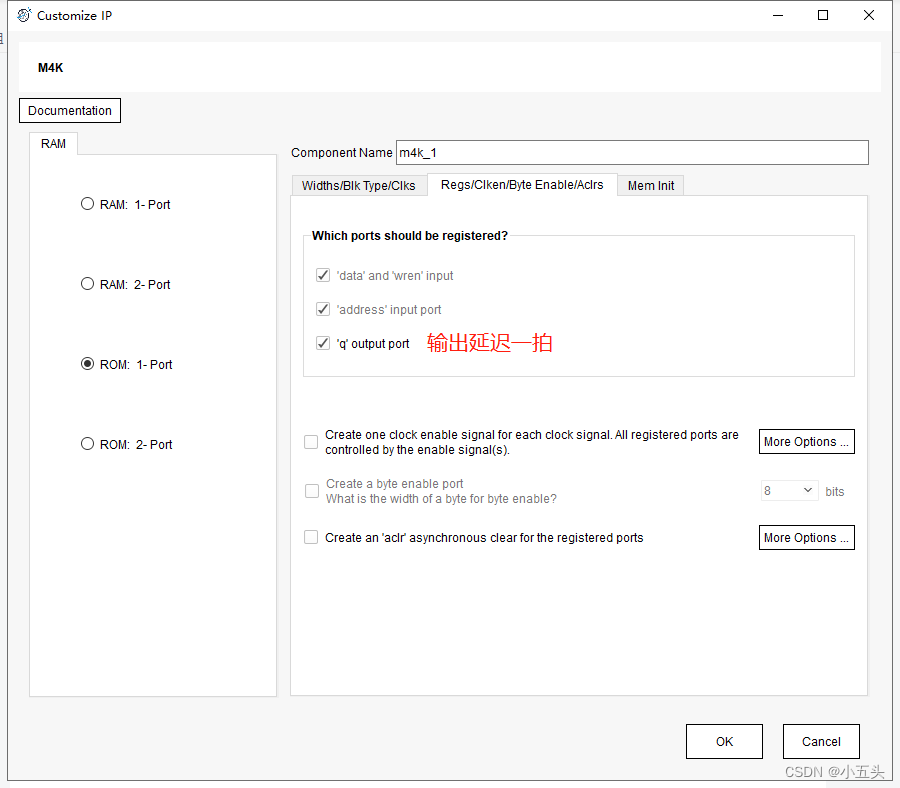

? ? ? ? ②:使用定制好的IP核進行開發:

??

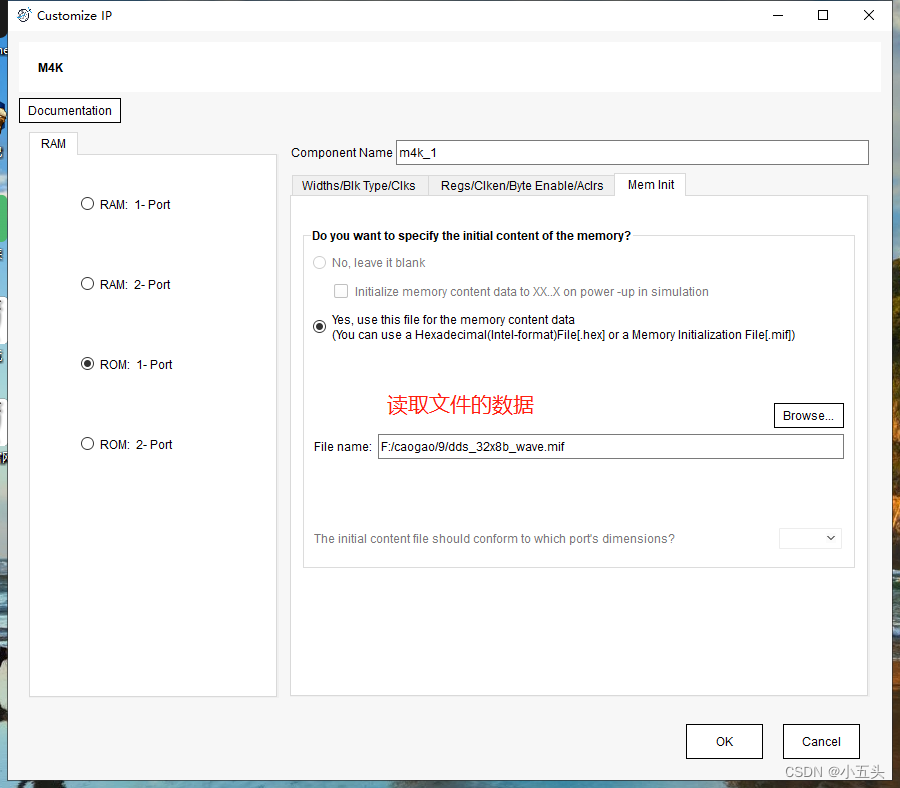

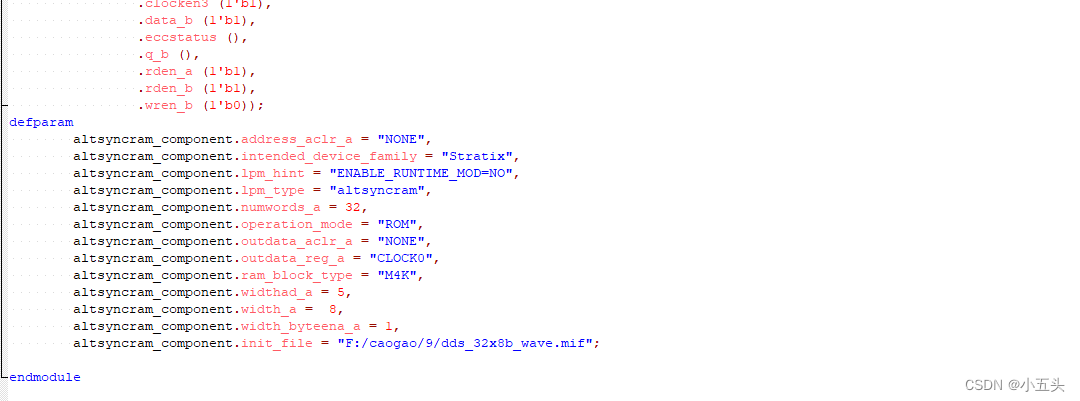

注意:?需要手動修改ROM IP核的底層程序,手動添加MIF文件:

?手動修改我們需要讀取的MIF文件:

?

module ROM_TOP(input wire clk,output [7:0] rom_data);reg [4:0] address;always @ (posedge clk)address <= address + 1'b1;m4k_1 u_m4k_1(.address (address),.clock (clk),.q (rom_data));

?結論

在使用FPGA開發ROM時,有一些要注意的關鍵點:

-

內存容量:確定所需的ROM容量,即地址位寬和數據位寬。根據應用需求和數據量大小,選擇合適的ROM大小。確保ROM的存儲容量足夠存儲所需的數據。

-

內存布局:考慮如何組織ROM的內存布局。根據應用場景和數據存儲需求,確定存儲單元的分配,如按字節、字、行或其他方式進行分配。合理的內存布局可以提高存取效率和資源利用率。

-

數據初始化:在設計過程中,確保在ROM中正確初始化所需的數據。根據應用需求,編寫初始化代碼或使用工具進行數據初始化。確認ROM中存儲的數據與設計要求一致。

-

讀寫時序:了解ROM的讀寫時序要求。根據FPGA芯片和ROM規格,設置正確的時鐘頻率、讀寫使能信號和時序約束。確保讀取操作和寫入操作在正確的時鐘周期內完成,并滿足ROM的時序要求。

-

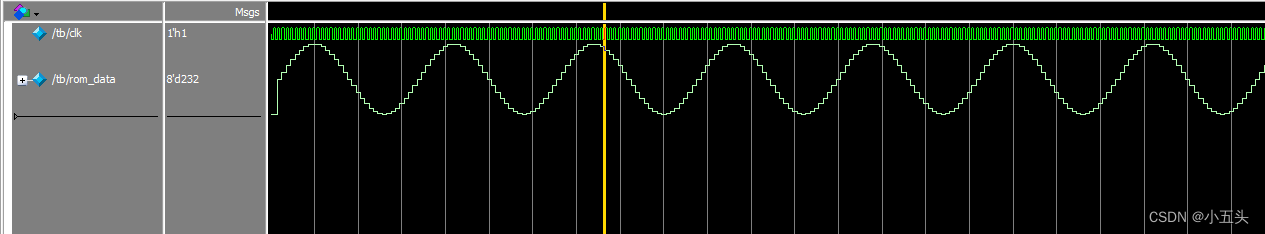

仿真驗證:使用仿真工具對設計進行驗證,確保ROM的功能和數據正確性。通過仿真測試,檢查ROM在各種情況下是否按預期工作,并驗證所需數據的正確性。

-

優化和資源利用:優化ROM的設計,以減少資源使用和功耗。使用合理的編碼方式、壓縮算法和存儲器布局來提高ROM的效率和資源利用率。

-

靈活性和可擴展性:考慮將ROM設計為可靈活擴展和可配置的。根據需求,設計ROM以支持動態數據更新或通過編程重新配置ROM內容的功能。

-

設計驗證和調試:進行系統級驗證和調試,確保ROM與其他模塊和外設的正確集成。驗證ROM與其他電路之間的接口和數據通信是否正常。

通過注意以上關鍵點,能夠更好地開發和使用FPGA中的ROM,確保其功能正確性、性能優化和資源利用率。

,必會題,思維題)

)

安裝python的不同版本例如3.8)

)