這一點先淺顯理解,就好比我要造一個樓

- 我是用現成的材料造節省?

- 還是需要用XX材料,但是XX材料還需要現成材料造呢?

這也不一定,但是基本來說,如果使用現有資源,能夠直接用,那其實是最好不過的了,這也就是Verilog設計的時候,需要注意的,應該調用更少的資源完成更多的事情,不是嗎?

如果不理解,想想用現有的樂高零件,搭建一個樓吧,如果有很大的板子可以直接用,就沒必要再用幾個長條拼接了,不是嗎?

有需求,需要某些器件的時候,應該如何設計?

- 想想有沒有現成的,如果有,是不是有必要用?

- 如果沒有,是不是可以造一個通用器件,有沒有這個必要?

- 如果用的很少,是不是只需要單獨做一下就好了?

舉例:CPU設計在,I型指令需要用到的的符號擴展器,如何做?再設計個模塊還是直接上手?使用頻率高不高,性能影響如何?

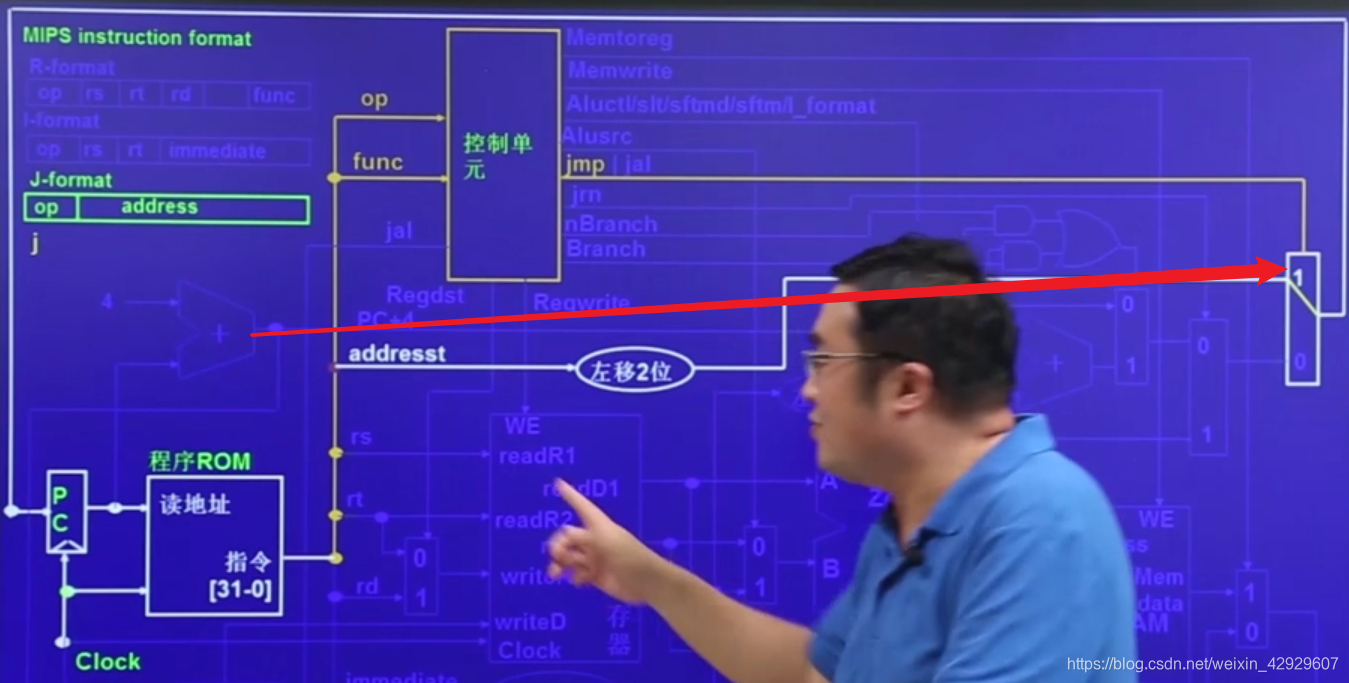

可以看看j型指令,目前來說,這條指令,太長了,如果縮短到ID階段,那將會很好,節省了資源。

(數據通路設計思想))

數據通路構建:取指部件分析)

數據通路構建:第一類R型指令分析(1))

)

并行接口8255A(1):全局觀)

并行接口8255A(2):控制字概述)

(約束條件 || 限界函數))

:算法初探(邏輯抽象 + 示例 + 代碼實現))

數據通路構建:第一類R型指令分析(2))

插敘:綜合與實現)

:電路模型的基本變量)

:電路與電路模型)