本人之前其實也用STM32做過一些小東西,但因為時鐘的初始化一般是直接在SystemInit時鐘系統初始化函數里直接配置為72MHz,所以對于STM32的時鐘框圖并沒有怎么理會,今天剛好有空就重新看了一下并寫一篇博客記錄一下吧,以免以后又忘了。

?

STM32 有5個時鐘源:HSI、HSE、LSI、LSE、PLL。 ??

①、HSI(High Speed Internal Clock signal)是高速內部時鐘,RC振蕩器,頻率為8MHz,精度不高,受溫度影響。

②、HSE(High Speed External Clock signal)是高速外部時鐘,為外接晶振提供的時鐘,晶振頻率范圍為4MHz~16MHz,常用8MHz的外部晶振。

③、LSI(Low Speed Internal Clock signal)是低速內部時鐘,RC振蕩器,頻率為40kHz,可配置為RTC的時鐘來源,但RTC時鐘對時鐘精度要求較高,故較少用于RTC,常用于獨立看門狗時鐘。

④、LSE是低速外部時鐘,接頻率為32.768kHz的外部晶振,用于RTC時鐘。

⑤、PLL為鎖相環倍頻輸出,其時鐘輸入源可選擇為HSI/2、HSE或者HSE/2。 ?倍頻可選擇為2~16倍,但是其輸出頻率最大不得超過72MHz。我們常用8M的外部晶振的9倍頻,即72MHz作為系統時鐘(SYSCLK)。

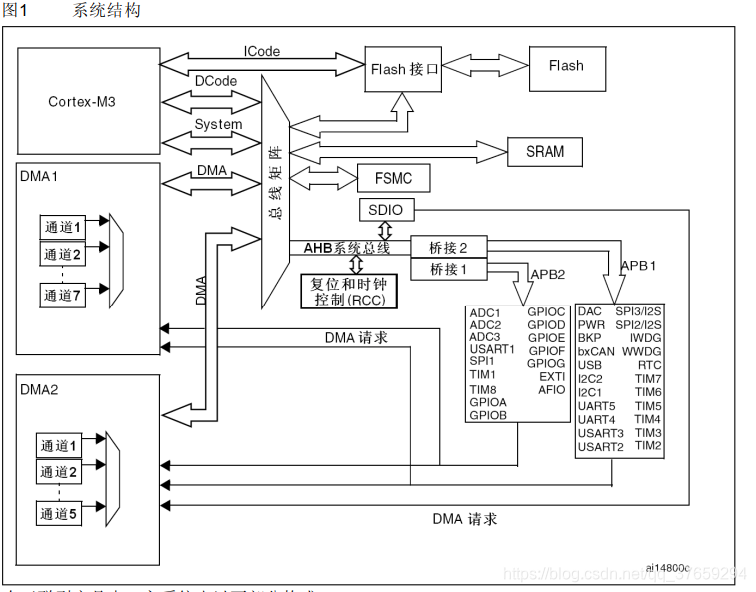

如圖,

如圖,

紅框1中的OSC_OUT和OSC_IN接外部8M晶振(范圍為4到16MHz)作為HSE(外部高速時鐘),通過PLLXTPRE位可控制選擇器②是輸出HSE還是HSE/2,選擇器①通過PLLSRC位控制,用來選擇是HSI/2還是選擇器②的輸出作為倍頻鎖相環(PLLMUL控制倍頻的倍數)的輸入,我們一般都是(系統默認)配置為8Mhz的HSE作為倍頻器的輸入并選擇9倍頻產生72MHz的時鐘PLLCLK作為系統時鐘(SYSCLK),系統時鐘經AHB預分頻器(默認分頻系數為1)得到HCLK,可作為部分外設的時鐘,如SDIO,FSMC等,再經APB1,APB2預分頻器可得到PCLK1、PCLK2。

PCLK1:APB1低速總線時鐘,最高為36M。為APB1總線時鐘的外設提供時鐘。但又經過2倍頻作為定時器2~7的時鐘,所以定時器2~7即使是在APB1下,也為72M的時鐘。

PCLK2:APB2高速總線時鐘,最高為72M。為APB2總線時鐘的外設(包含定時器1和8)提供時鐘。

PCLK2經ADC預分頻器(/2,4,6,8)作為ADCCLK(最大為14M),我們常選擇6分頻(72/6=12M)

(上圖看看到掛載在APB1,2下的外設)

紅框2表示RTC的時鐘來源為:①HSE/128;②LSE;③LSI。我們通常選擇LSE(頻率為32.768KHz的外部晶振),而LSI精度較低,并不太適合RTC時鐘,而常作為獨立看門狗的時鐘。

?

紅框3表示STM32可以選擇一個時鐘信號輸出到MCO腳(PA8)上,可以選擇為PLL 輸出的2分頻、HSI、HSE、或者系統時鐘。

上面還漏了一點,關于CSS,CSS為時鐘安全系統,在STM32參考手冊6.2.7小節有提到,開發者可以通過CSS中斷設置HSE故障后的系統時鐘,比如HSI/2(4MHz)的16倍頻,如果開發者未開啟CSS中斷或者在中斷中沒有進行相應

配置,則硬件默認使用HSI(8MHz)作為系統時鐘。

另外關于如何配置以上所講的時鐘,可以看STM32參考手冊6.3小節RCC寄存器描述。

導致編譯無法通過的解決心得)

)