? ? S3C2440在默認情況下,整個系統全靠一個12MHz的外部晶振提供頻率來工作運行的,也就是說CPU、內存、UART、ADC等所有需要用到時鐘頻率的硬件都工作在12MHz下,但是通過查閱芯片手冊我們知道CPU時鐘最高可為400MHZ,那么怎么設置時鐘讓芯片工作在更高的時鐘頻率下呢?首先我們來看一下S3C2440的時鐘框架。

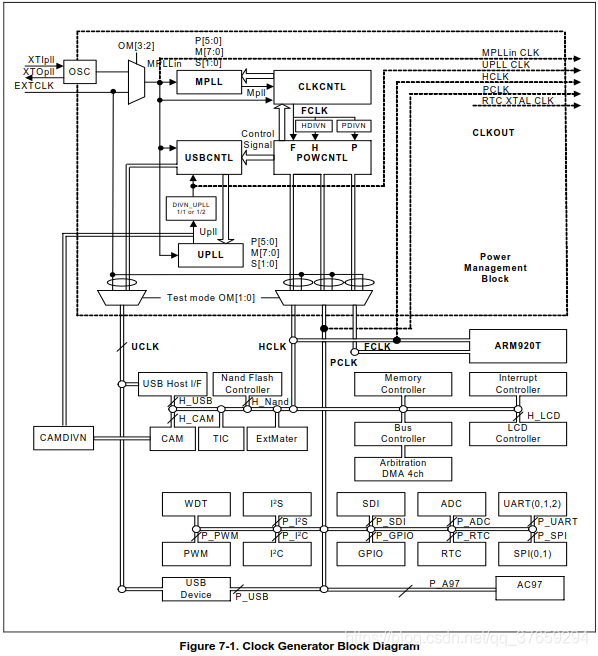

? ? ? ? ? ? ? ? ? ? ? ? ? ? ??

? ? ? ?由圖可知S3C2440可以通過XTIpll、XTOpll引腳外接晶振(通常為12MHZ),也可以通過EXTCLK外接時鐘,我們一般選擇外接晶振。我們接入的時鐘才12M,而CPU時鐘卻可以高達400M,鎖相環(PLL)就是用來倍頻時鐘的,2440有MPLL和UPLL這兩個時鐘鎖相環,MPLL倍頻后的時鐘主要用于CPU和各種外設,而UPLL倍頻后的時鐘主要用于USB。我們可以通過OM[3:2]來控制這兩個鎖相環的時鐘源,因為通常我們是外接晶振,所以把OM3和OM2這兩個引腳接到GND。

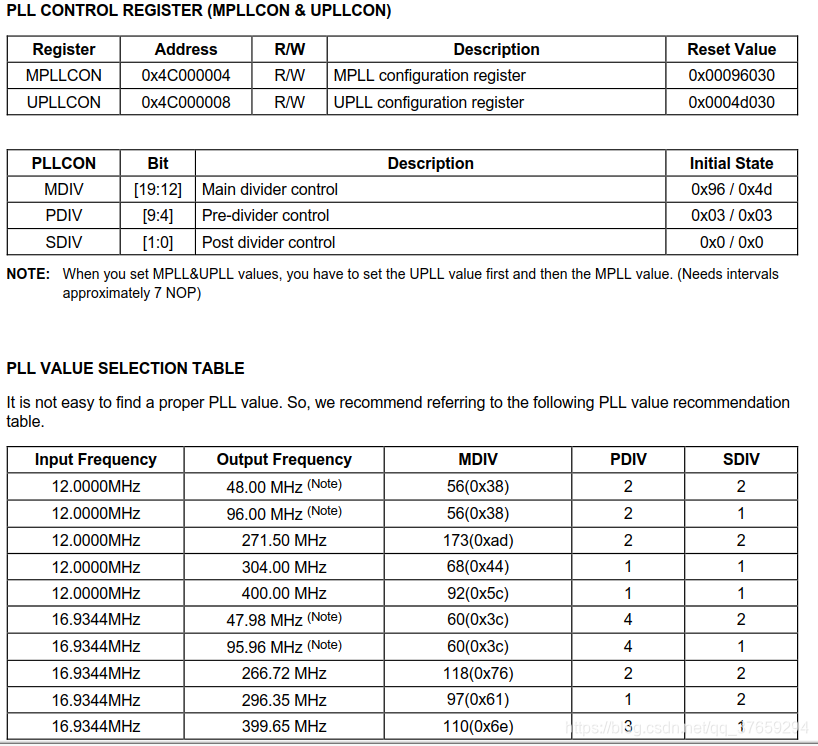

? ? ?MPLL倍頻后的時鐘為FCLK,而FCLK經過分頻又得到HCLK(掛載一些高速外設)和PCLK(掛載低速外設),我們可以把MDIV、PDIV、SDIV分別配置為92(0X5C),1,1,也就是把(92<<12)|(1<<4)|(1<<0)寫到0X4C000004地址得到400M的FCLK。

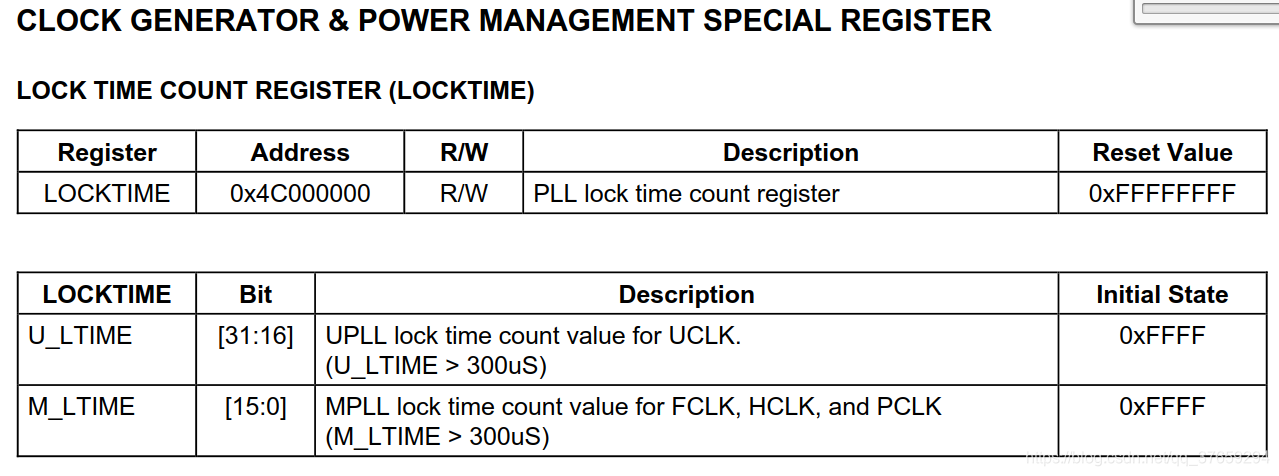

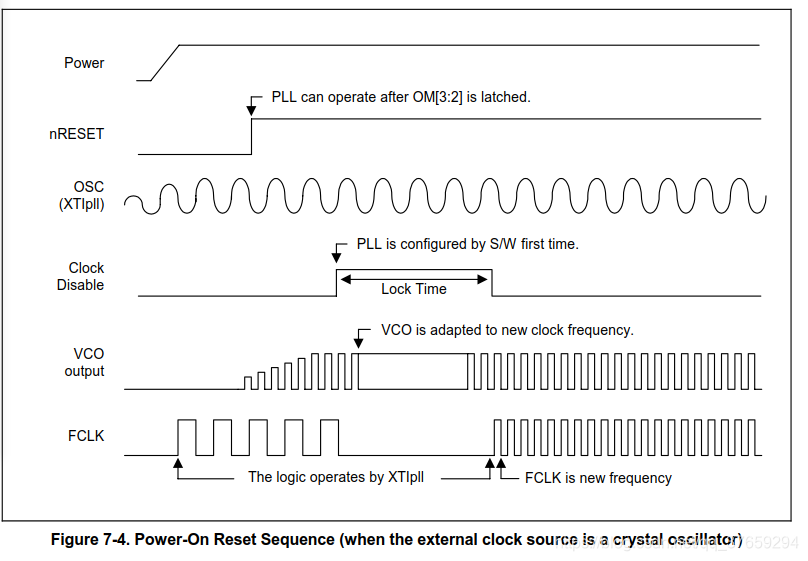

?補充關于下圖的知識,一般我們系統上電后電壓不穩定,我們可通過外圍電路實現把nRESET拉低一段時間后再拉高,此時系統開始工作,FCLK還只是外接的晶振的頻率,OM[3:2]引腳電平鎖存后,PLL開始工作,經過一段鎖存時間后,FCLK變為穩定的倍頻時鐘用于系統工作,鎖存時間可通過設置LOCKTIME來改變,默認是設置為0XFFFFFFFF,一般我們不對其進行修改。

?

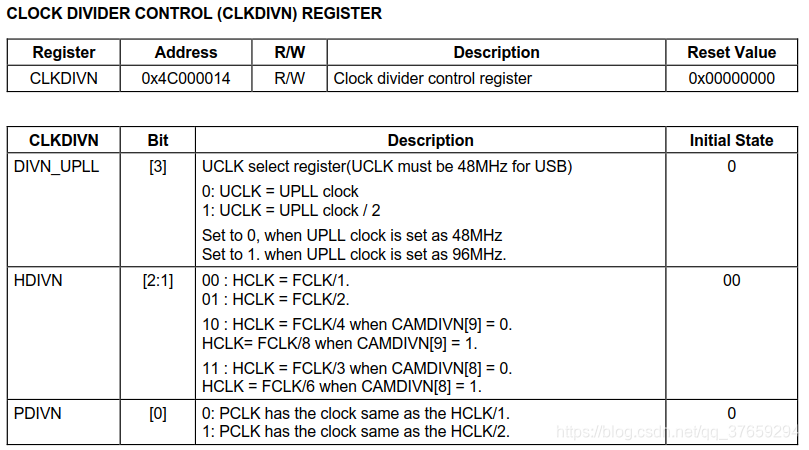

? ? 假如我們想通過400M的FCLK得到100M的HCLK和50M的PCLK,查閱下表我們知道可以往0X4C000014寫入0x5。

? ? ? ?但是這里我們需要注意一點:如果HDIV設置為非0,CPU的總線模式要進行改變,默認情況下FCLK = HCLK,CPU工作在fast bus mode快速總線模式下,HDIV設置為非0后, FCLK與HCLK不再相等,要將CPU改為asynchronous bus mod異步總線模式,可以通過下面的嵌入匯編代碼實現:

mrc p15,0,r0,c1,c0,0orr r0,r0,#0xc0000000 //R1_nF:OR:R1_iAmcr p15,0,r0,c1,c0,0?

導致編譯無法通過的解決心得)

)