本篇文章為本人學習Xilinx的Vivado HLS教程記錄的學習筆記,僅供學習參考。

Vivado HLS官方視頻教程:

優酷視頻?v.youku.com目錄:

- Vivado HLS課程簡介

- FPGA與CPU、GPU、DSP的區別

- FPGA的優勢

- Xilinx FPGA架構:邏輯單元、算術邏輯單元、存儲單元

- 使用C/C++ 來開發FPGA時需要關注的方面

1.Orientation and Overview of this Course(課程簡介):

設計流程、代碼風格、for循環和數組的優化方法、輸入輸出端口的實現方式

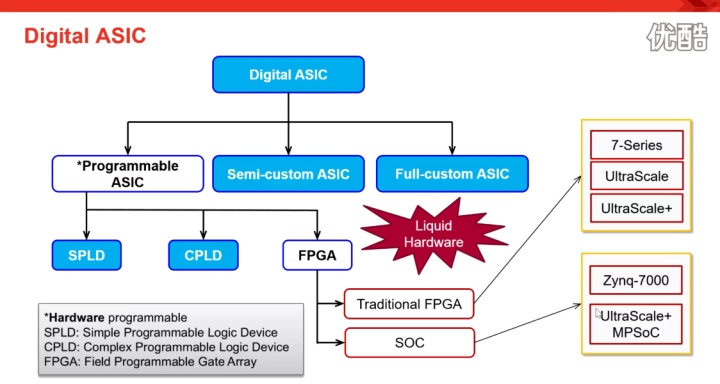

2.FPGA架構(軟件工程師的角度):

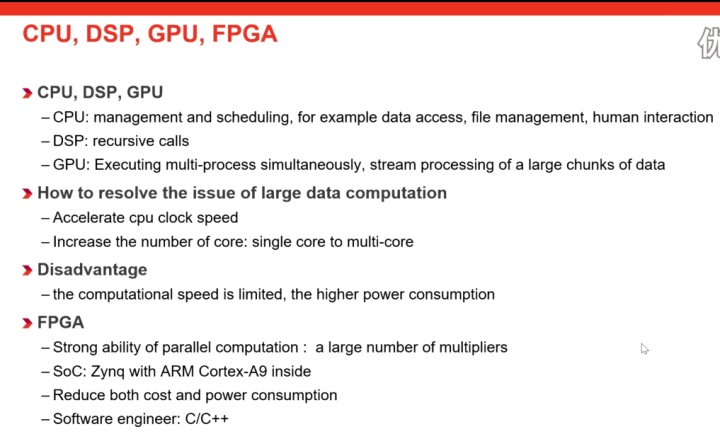

2.1 FPGA與CPU、GPU、DSP的區別

- FPGA是硬件可編程,其他芯片為軟件可編程。

- FPGA具有豐富的硬件計算單元(大量乘法器)以及分布式并行內存,其他芯片只有非常有限的計算資源,比如CPU只有幾個高性能ALU,另外其他芯片一般使用一個共享內存,在任何是有只能進行一次的讀或者寫操作。

- FPGA靈活的硬件資源導致所使用的HDL語言抽象級別非常低,為RTL級,而其他芯片的編程語言都是在算法級或者系統級。

- CPU適用于調度和管理的場景,比如文件管理,人機交互。

- DSP適合數據處理,尤其是遞歸調用

- GPU適合大容量數據流處理

來自 <https://blog.csdn.net/wangwenqing2018/article/details/77824785>

2.2 FPGA的優勢

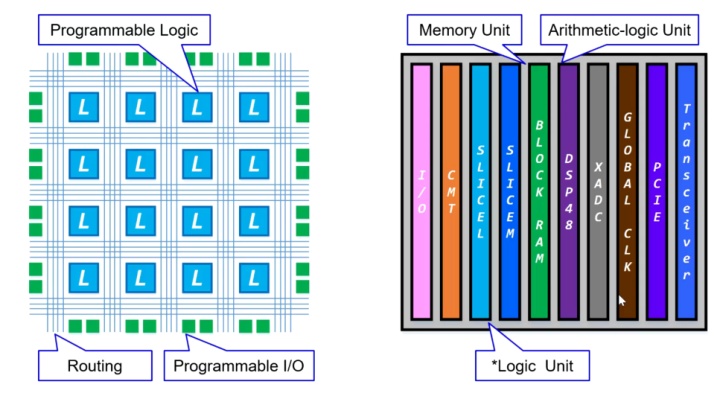

2.3 Xilinx FPGA架構(軟件工程師角度)

邏輯單元、存儲單元、算術邏輯單元

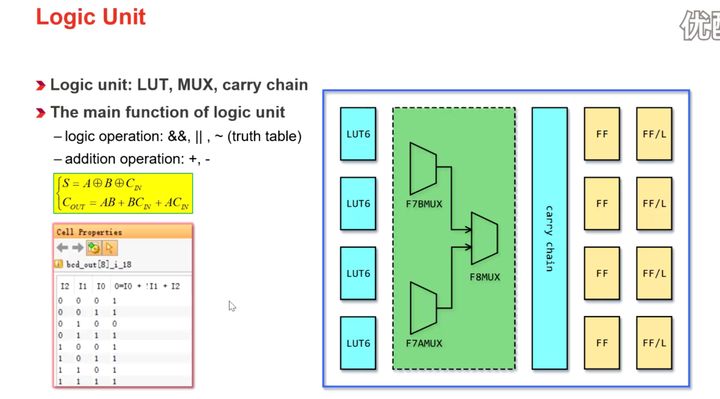

(1)邏輯單元:LUT查找表、MUX數據選擇器、carry chain進位鏈

- LUT實現邏輯函數發生器:通過真值表的方式實現

- 加法運算也屬于邏輯運算(異或、與等):可用LUT或DSP48實現

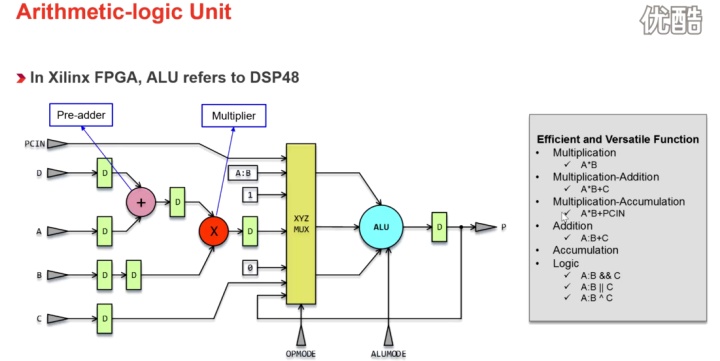

(2)ALU算術邏輯單元:DSP48

可實現加法、乘法、累加等,可應用于數字濾波、FFT等

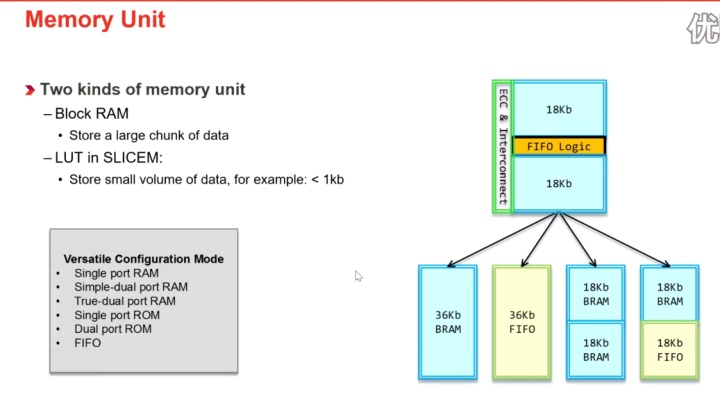

(3)存儲單元:

- Block RAM(塊隨機存儲器、2個18Kb的內存組成)

- 分布式RAM(LUT in SLICEM)

- 可多功能配置模式:單端/雙端、ROM/RAM、FIFO

- C/C+數組會映射到RAM

軟件工程師關注:功能、操作與單元的對應關系、算法模型的資源利用率(綜合報告有)、優化方法

3.使用C/C++ 來開發FPGA時需要關注的方面:

- 算法的不同部分的功能

- FPGA底層單元的操作

- 算法不同部分同FPGA底層單元的映射關系

- 算法的FGPA資源使用率

![[LeetCode]Maximum Depth of Binary Tree](http://pic.xiahunao.cn/[LeetCode]Maximum Depth of Binary Tree)

![BZOJ2435 [Noi2011]道路修建](http://pic.xiahunao.cn/BZOJ2435 [Noi2011]道路修建)

傳遞)