????????電源規劃是給整個芯片的供電設計出一個均勻的網絡,它是芯片物理設計中非常關鍵的一部分。電源規劃在芯片布圖規劃后或在布圖規劃過程中交叉完成,它貫穿于整個設計中,需要在芯片設計的不同階段對電源的供電網絡進行分析并根據要求進行修改。,主要分三部分內容進行分析:電源網絡設置、數字與模擬混合供電、單電源與多電源供電電源網絡設置。其中電源環線(power ring)和電源條線(power stripe)的設置為主要工作。

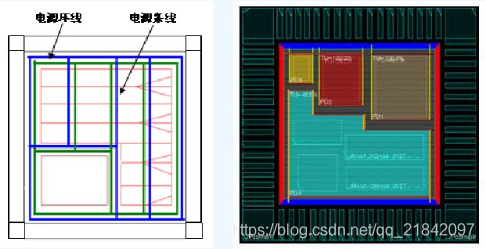

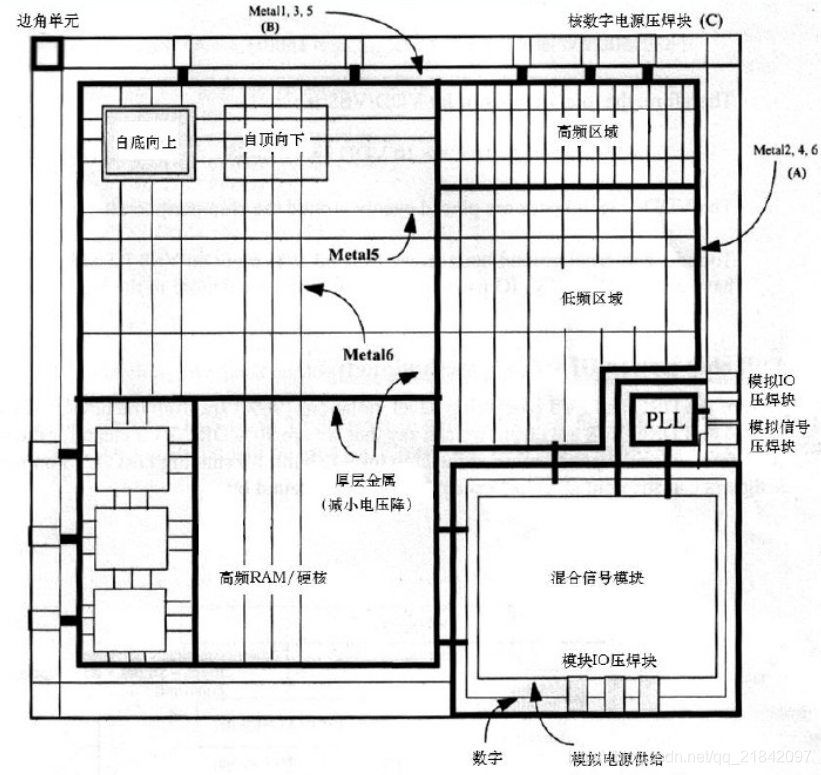

? ? ? ? 如上圖所示,左圖中左下角為硬核部分,硬核部分的上方和右側的電源線稱為模塊電源環。右圖是多電源多電壓中應用的電源環分布示意圖。

????????芯片供電是通過I /O 單元來實現的,在做電源規劃和電源網絡設計時,首先要做電源預算(power budgeting),商用產品慣例認為總的誤差應當控制在5%之內。它包括從電源網絡和PCB板級到封裝bonding之間的波動(約為1%),再到電源I /O 單元和電源環之間的波動(約為1%)和最終直至標準單元之間的電壓降(約為3% ) 。更準確的預算則通過功耗分析的手段來做定量計算。

一、電源網絡的設計

????????這里闡述的電源網絡設計是針對于普通的I /O 單元四方分布的數字芯片設計,對于復雜的數模混合設計以及多電源設計將在后面的分別闡述。供電網絡設計主要內容有以下幾部分組成:

- 電源連接關系的定義,又稱為global net connect。

- 芯片核內(core)部分的電源環設計,又稱為power ring。

- 芯片內所包含的硬核(如RAM、ROM以及IP、COT模塊等)的電源環設計。

- 芯片核內縱橫交錯的電源網格的設計,又稱為power stripe。

- 芯片的供電單元與電源環的連接,又稱為I /O 單元power。

- 芯片內部電源網格和硬核電源環連接部分的設計,又稱為ring pins。

- 將標準單元的供電網絡與核內電源網格總連接設計,又稱為followpins。

- I /O供電單元電源環的設計,又稱為I /O單元power ring。

????????最后我們還需要對電源網格進行檢查,檢查是否存在短路和開路以及供電不足等問題。對于Flip Chip的設計,供電網絡的設計還包括電源凸點bump的設計以及布線。下面分別介紹各部分的內容。

1、全局電源

????????在電源網格設計中,首先要對電源進行定義,主要包括:全局電源的定義以及連接關系的定義。全局電源網絡連接(global net connect)是指把相應的端口和網絡連接到合適的電源和接地網絡上去,從而使得我們針對整個設計可以正確無誤地順利完成供電網絡設計、電源布線、詳細布線和功耗分析等步驟。這些終端和網絡的連接信息一部分包含在Verilog網表中,另一部分則包含在相應的LEF文件當中。

????????通過Verilog網表中的定義,我們可以把以下幾種類型的網絡連接到相應的全局電源和接地網絡上去。

- ?電源和接地網絡

????????它是將網表中每個標準單元和模塊等的電源和接地網絡連接到合適的全局電源和接地網絡上去。這些標準單元和模塊等的電源和接地網絡互連關系,在Verilog網表中主要通過關鍵字“wire”進行定義。

- 接高電壓和接低電壓網絡

????????它是將接高電壓和接低電壓網絡連接到合適的全局電源和接地網絡上去。它們之間的互連關系,在Verilog網表中主要通過關鍵字“ 1'b0”、“ 1'b1”、“supply 0”,以及“supply 1”進行定義。

- 電源和接地端口

????????它是將供電端口和接地端口連接到合適的全局電源和接地網絡上去。諸如“VDD、vdd、vdd!”和“VSS、vss、gnd!”等就是這些電源和接地端口和網絡在LEF文件中定義的名稱。

- 填充單元網絡

????????它是將供電端口連接到合適的全局電源和接地網絡上去。在添加填充單元前后,均可通過手工指定相應的連接關系。

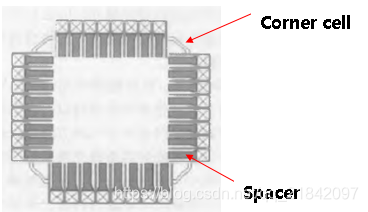

I / O 的拐角單元(corner cell)和I / O 填充單元(filler,spacer)。 因為I / O 在芯片周圍通常需要擺放成類似戒指(ring)一樣的環形,因此通過這兩個單元可以填充I /O單元之間的空隙以使它們形成電源和地的環狀網。

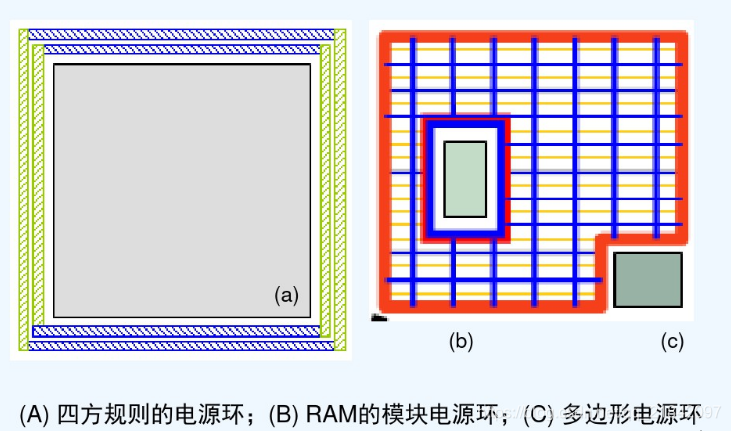

2、電源環線

????????電源環線(power ring)是指為了均勻供電,包圍在標準單元周圍的環形供電金屬,它也是連接供電I /O 單元和標準單元的橋梁,供電I /O 單元通過金屬連接到電源環,標準單元通followpins連接到電源環,從而構成了供電I /O 單元給標準單元以及硬核供電。電源網格是為了平均分布電流,縮短電流回路,在有效減小電壓降的同時,避免由于電流分布不均時造成的熱點(hot spot)現象以及電遷移(EM,electromigration)問題。

????????電源環的設計主要有3個參數:電源環的寬度、電源環的間距d 以及電源環的對數n。電源環的參數也是根據功耗計算得來。

- ?電源環的寬度

????????根據整個芯片的供電峰值電流以及廠家所給的設計規則中所允許的電流密度以及電源環的對數n所決定。

?????????????????

????????式中,是芯片的峰值電流?

? ? ? ? ? ? ? ? ?是廠家工藝庫給出的電流密度上限

?????????????????是電源環的數目

? ? ? ? ? ? ? ??是調整因子,根據芯片的供電I /O單元分布而定

- 電源環的間距

????????電源環的間距根據廠家所給的設計規則中的最小間距決定,一般情況下為最小間距的2倍左右,但是也有工程師提出盡量減小電源環之間的間距,從而增大電源環的耦合電容,從而起到過濾電源噪聲的作用。

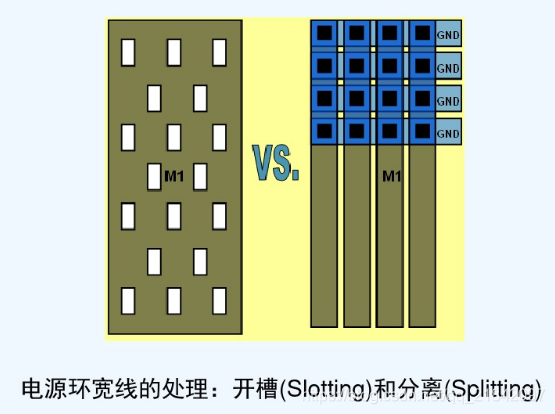

? ? ? ? 除以上兩個參數外,在芯片的制造過程中,一般寬線需要打孔散熱,所以廠家會制定寬線的規則。一般情況下,希望單個電源環的寬度不要超過廠家規定的寬線規則,從而避免打孔,打孔在芯片設計中又稱為slotting,更好的辦法是用splitting。電源環的對數n 由芯片的面積、廠家的設計規則、金屬的層數等多種因素決定。當金屬的層數較多時,可以選用多層金屬布置電源環,從而有效減小電源環的寬度和減小電源環所占據的芯片的面積。

????????在有些設計中,還需要對硬核及RAM設計電源環,RAM以及硬核電源環寬度的設定也是根據硬核的供電電流決定,其設計的方法與核內的電源環相同,只需要指定電源環的所有參數便能自動生成。很多廠家提供的硬核在設計時已經產生了電源環,當應用到芯片頂層時只需要將電源網格連接到硬核內部自身的電源環即可,從而減小不必要的面積浪費。?

3、電源條線

????????芯片內部縱橫交錯的電源網格(power grid)或“電源條線"(power stripes)設計有專門的理論和算法。電源網格通常為均勻分布,電源條線通常是不規則或不均勻分布,電源網格可以看成是電源條線的特例。簡單說明電源條線相關內容。

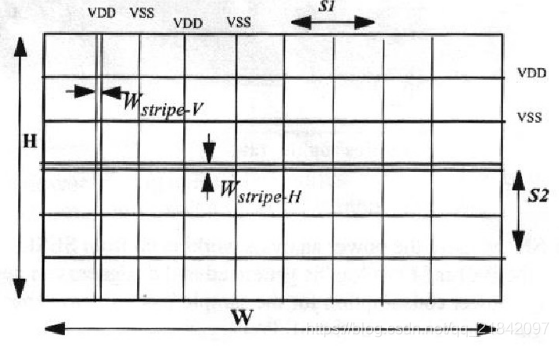

???????從上圖中我們看出,電源網格中重要的4 個參數分別是:縱向電源條線的寬度,橫向電源條線的寬度

;橫向電源條線的間距

;縱向電源條線的間距

。其中縱向電源條線的寬度

與橫向電源條線的間距

成正比關系,也就是說寬度較大,間距就可以較大,電源條線的分布可以稀疏一點;橫向電源條線寬度值較小,間距也應該小一點,電源條線的分布需要密集一點。與縱向電源條線相比較,橫向電源條線的寬度

與其間距

的正比關系也存在,但是由于在橫向有很多標準單元的followpins的存在,需要的橫向電源條線比縱向電源條線要少很多。??

????????對于和

的設定,有以下幾個經驗規則:

的分布間隔一般取垂直布線間距(pitch)的整數倍,其目的是充分利用布線通道其值不能太大,一般情況下不要超過最小二輸入與非門寬度的4倍。每一層金屬的pitch在物理庫中都有相應的定義。?

- ?

的最大值取標準單元庫中最小與非門寬度的4倍。當芯片的利用率較高,布線擁塞程度較大時,一般選擇細密的電源網格。如果芯片的利用率非常低,那么將電源網格設計得越寬,其線上的電阻越小,電壓降越小。

- ?

的取值一般是標準單元高度的整數倍,通常選擇1倍或者2 倍。

?????????電源條線所選用的電源層也根據LEF中的規定所選,縱向必須用偶數層走線,橫向必須用奇數層走線。由于高層金屬具有較小的寄生電阻,用高層金屬走線可以有效地減少電壓降。

二、數模混合供電

????????即使是純數字電路芯片設計,通常也要用到一個模擬模塊PLL作為時鐘信號發生器。今天的SoC設計中,數模混合電路則更加普遍,A/D、D/A及PLL等模擬模塊的集成到處可見。在數模混合供電設計中,需要特別注意電源信號之間的干擾和隔離,因而需要建立不同電源區域(power domain)。在布局前一般需作如下幾點考慮和處理:

- 模擬模塊的工作區域一般放置于芯片的某個角落。當設計中有多個模擬單元時,將多個模擬單元的位置應相對集中在芯片的某個角落,其中間不應該混合放置數字模塊。

- 模擬區域需要單獨供電,給模擬信號供電的I /O 單元應放在模擬模塊邊上,盡量縮短供電線路的長度。

- 在模擬模塊的周圍布置保護隔離環(guarding ring),從而實現數字信號和模擬信號電源之間的隔離。

? ? ? ? 如上圖所示,電源規劃中的一些細節問題如下? ? ? ?

- 數模信號模塊的放置。模擬PLL和模擬信號模塊處于芯片的右下角,右下角的I /O 單元均為模擬信號用的信號端口,在PLL和模擬信號模塊的周圍放置的都是低頻信號模塊,以避免數字信號跳變對模擬信號的影響。

- 數模信號模塊的供電。模擬PLL和模擬信號模塊均分別具有數字供電和模擬供電兩部分組成,其中模擬供電在內部,數字供電在外部,兩個模塊之間的模擬供電環是相通的,在外圍的數字供電部分與芯片的數字供電部分相聯合,在其底下加上保護環(guarding ring)用以隔離。在有些設計中,在條件允許的情況下或者嚴格要求下,既具有模擬供電也具有數字供電的模擬單元,數字供電部分也需要單獨供電,并與核內的其他數字供電部分保持隔離。

- 數模信號模塊中的電源環。電源環設計可以采用多層金屬完成,從而節約電源環的寬度,降低電源環所占據的芯片面積。數模信號模塊中的電源環分別處理,相互獨立。

- 數模信號模塊中的電源網格。數模信號模塊中的電源網格設計采用高層金屬完成布線,在高頻區域,電源網格較為密集,而在低頻區域電源網格較為稀疏。

- 數模信號模塊中的電源設計方案。在整個芯片中,模塊的電源設計部分采用了自上而下和自下而上的兩種設計過程,這是模塊電源的典型設計方法。?

三、多電源供電

????????在數字芯片設計中,多電源供電(MSV,muki-Siipply voltage)早就被用來處理數模混合電路的供電。在數模混合電路的供電方案中,MSV專指多組電源同樣電壓(如均為1.2 V)供給不同電路(數字、模擬)。隨著低功耗設計技術的更多應用,同一芯片中則更多地采用多組電源多組電壓供電(MSMV,multi-supply multi-voltage)的方案。除了保留傳統的MSV的方法外,其中,關鍵模塊采用高電壓供電,頻率較低的模塊采用低電壓供電是有效降低功耗的一種方法。

1、電源規劃

????????每一個電壓域當中都必須有完整的電源和地線電源環。在創建電源環時,可以采用傳統的方法,即根據布圖規劃的情況指導工具完成設計,也可以通過自動供電網絡設計工具(APP,automatic power planner)為每一個電壓域指定一個合適的模板來進行設計,其步驟如下:

- 創建芯片核心電源環,其方法與單電源環設計一致,單電源環只有一對供電,而多電源環有多對電源供電,故而會占用較大的面積。

- 為每一個電壓域和硬宏單元模塊創建一個模塊電源環。在多電壓設計中,首先需要定義電壓域的內容,即每個電壓域的工作電壓和所包含的模塊,如果為相應電源環所指定的電源和地線網絡同電壓域定義的電源和地網絡不匹配,工具則會產生相應的警告提示。

- 為宏單元(硬核)模塊創建模塊電源環。

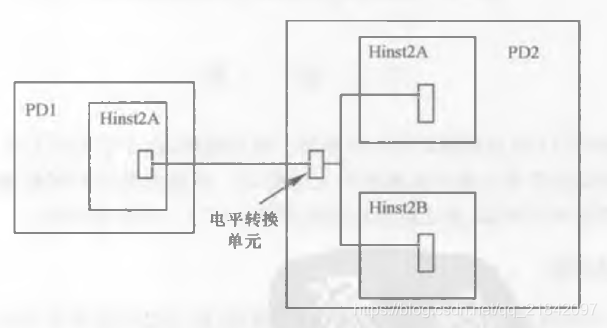

2、電平轉換單元的插入

????????在多個電源供電時,不同的工作電壓區之間需要插人電平轉換單元(VLS,voltage level shifter),其步驟如下:

- 讀入相應的電平轉換單元表。

- 在內部電壓域網絡上插入電平轉換單元。

3、隔離單元的插入

????????當設計中存在被關閉的電壓域,為了不使關閉區域與非關閉區域相互影響,必須在所有的接口處添加隔離單元(isolation cell),并要:①檢查出所有需要添加隔離網絡的信號端口 ;②在相應的接口信號處添加隔離單元。?

四、總結

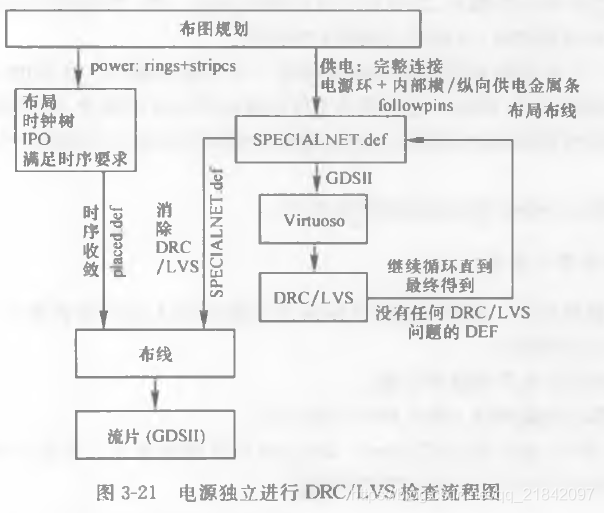

????????布圖規劃與布局之間的電源規劃工作越來越復雜,其重要性也越來越大。設計中發現,不少DRC/LVS問題與電源規劃或電源設計有關。大多數的模塊級或芯片級DRC和LVS錯誤都是由供電問題引起的。由于DRC/LVS工具對于電源的抽取是通過一定的規則來提取,因此對于結構相同的電源部分,工具并不能很好地識別,從而會造成LVS的錯誤。因此在用sign-off的工具進行LVS檢查時,設計者可以“剔除”掉除電源和接地網絡外的所有其他單元和模塊,單獨運行僅僅針對供電網絡的DRC/LVS檢查和僅對內部網絡的檢查,其流程如圖:

?

?

:Regullar Expressions的使用)

)

)