一、低功耗設計方案綜述

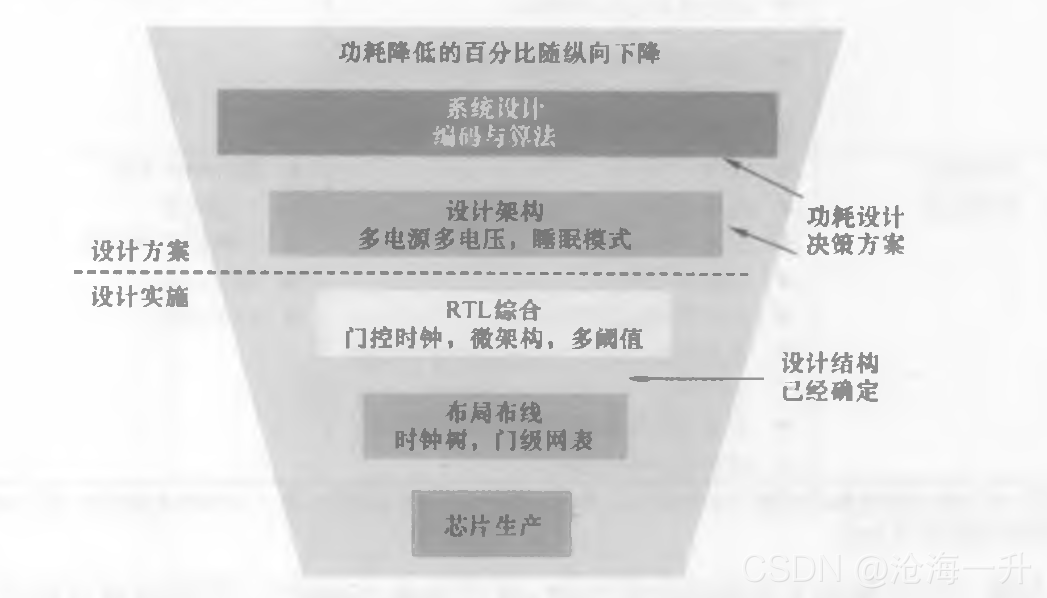

????????為了實現集成電路的低功耗設計目標,我們需要在系統設計階段就采用低功耗設計方案,因為隨著設計流程的逐步推進,到了芯片設計實現階段,降低芯片功耗的方法將越來越少,可節省功耗的百分比將不斷下降,這時,設計的主要目標將會側重于如何將設計方案變成物理實現。??

1、方案的選擇

????????集成電路設計流程中設計數據是有統一的格式的,系統設計到邏輯綜合由RT L網表傳遞,邏輯綜合到物理實現則由門級網表傳遞,布局布線后,邏輯驗證和形式驗證由門級網表傳遞。顯然,對于低功耗設計我們也需要一種統一的功耗約束文件,即通用功耗格式CPF(common power format)文件,在整個流程中傳遞低功耗指標和參數。

| 設計階段 | 解決方案 | 設計工具或方法 |

| 系統級 算法級 | 系統分割 內存組織管理 電源管理 電壓與頻率降低 算法評估 算法轉換 | C systemC systemVerilog |

| 仿真驗證 可測試性 | 形式驗證 邏輯驗證 DFT | systemVerilog Verilog VHDL CPF文檔 |

| RTL編碼 邏輯綜合 | 狀態編碼 數據與地址線編碼 信號隔離 DFT 面積優化 門控時鐘 多閾值CMOS 多電源多電壓(MSMV) 電源關斷與電源保持時鐘門控 動態電壓與頻率調節技術(DVFS) | Verilog VHDL CPF文檔 設計約束文檔 門級網表 多電壓庫 多閾值CMOS庫 |

| 布局布線 物理實施 | DFT? 多閾值CMOS? | CPF文檔 設計約束文檔 門級網表 多電壓庫 多閾值CMOS庫 |

????????CMOS工藝的電路功耗可分為動態功耗和靜態功耗兩大部分。

????????其中,動態功耗包括器件本征電容和線負載電容充放電產生的功耗(也稱為開關功耗)和由于輸人信號跳變導致NMOS、PMOS同時導通從而形成電源到地的通路所產生的功耗(也稱為短路功耗)。對于動態功耗而言,它除了與供電電壓值有關外,還與負載電容、電路頻率和跳變因子有關。隨著器件尺寸的縮小,器件電容也在不斷減小,與此相反,電路工作頻率和信號跳變頻率卻在不斷地提高,因此要減小動態功耗還需在電路工作頻率和信號跳變頻率上尋求解決方案。由于電路頻率的降低意味著電路工作性能的下降,從而在保證性能的前提下,減小不必要的信號跳變頻率就成了減小動態功耗的切入點。這種要求產生了動態電壓與頻率調節(DVFS)技術。

????????當邏輯門處于靜態時,由PN結反偏電流、亞閾值電流、柵泄漏電流等效應引起的功耗稱為泄漏功耗。雖然單個邏輯門的泄漏功耗相當小,但對于千萬個邏輯門來說,泄漏功耗變得不能忽略,到90nm工藝節點后泄漏功耗已逐漸趕上并超越動態功耗成為功耗的主要部分。這種要求產生了多閾值電壓(MTCMOS,MT為multi-threshold)的方法。

????????功耗與電壓有著密切的關系,因此降低功耗最有效的方法是降低電路的供電電壓,這種要求產生了電源關斷(PSO)和多電源多電壓(MSMV)?的方法。

2、基本方法

????????低功耗設計的基本方法包括:①面積優化,它也是最經典的一種方法;②納米技術中開始引入使用的多閾值電壓技術;③時鐘門控電路。

1)面積優化

????????RTL邏輯綜合的主要目標包括優化時序、功耗和面積。在物理實施階段,同樣需要優化芯片的總面積和芯核面積,這樣可以進一步減小功耗。在時鐘樹綜合時,一方面通過約束文件,加速時鐘信號的傳輸,減小時鐘樹的總功耗,另一方面,優先選用反向器,而非緩沖器,減小時鐘樹上邏輯門的面積。但是,芯片的面積往往受到封裝的約束,和其他低功耗方法相比,通過減小面積降低功耗的效果比較有限。

2)多閾值電壓技術

????????在低功耗設計中通過減小泄漏功耗,例如采用多閾值器件MTCMOS(muhi-threshold CMOS)技術,也是個較好的低功耗設計辦法。

????????多閾值器件技術減小泄漏功耗的思想是,在電路中的關鍵路徑使用低閾值電壓的邏輯器件,非關鍵路徑使用高閾值電壓的邏輯器件。閾值電壓 較高的邏輯單元漏電流較小,但速度也較低,適合用于非關鍵時序路徑收斂。閾值電壓較低的單元漏電流較大,但工作頻率較高,速度快,用于關鍵時序路徑。通過綜合工具獲得最優化的高閾值電壓 和低閾值電壓 單元的組合,由此產生的網表能夠在滿足設計目標的同時盡可能地降低漏電流。這一技術的實現需要有多閾值電壓單元庫的支持,即能提供具有不同閾值電壓的邏輯單元,在綜合時,設定泄漏功耗的目標值,綜合工具能夠根據時序路徑自動選擇或替換合適閾值的邏輯單元。

3)門控時鐘

????????時鐘信號貫穿于整個芯片,芯片工作時,時鐘信號在存儲單元的時鐘輸入端周期性跳變,所驅動負載電容非常大,產生較大的動態功耗,所以借助門控時鐘插入技術可以減小由于不必要的時鐘跳變而產生的功耗。

????????門控時鐘技術是目前應用較為廣泛和成熟的低功耗設計技術。門控時鐘的邏輯綜合非常容易實現,首先打開門控時鐘綜合這個選項,再指定門控單元所選擇的類型,以及門控單元的扇出,最后指定動態功耗的目標,EDA工具便可以自動地綜合生成。現在很多庫廠家都提供了集成的門控時鐘。門控時鐘的插入需要考慮測試的問題,在時鐘樹綜合階段也需要特殊地處理。

? ? ? ? 為了進一步的達到低功耗的目的,可以采用低功耗的時鐘樹綜合技術(LP-CTS),這種技術利用最優化的時鐘門布局及克隆與反克隆等方法在確保了時鐘功率優化的同時可以滿足時序和物理目標的雙重需求,達到了更好的負載分配并將時鐘信號傳輸時間降到最小。

二、低功耗設計先進方法與物理實施

????????在低功耗設計的基本方法中,采用面積優化以降低功耗的方法已經成熟,多閾值電壓方法和門控時鐘方法節省功耗的效果比較有限。目前,節點效果更加顯著的、先進的低功耗設計方法包括:

- 多電源多電壓技術;

- 電源關斷與狀態保持電源門控技術;

- 動態電扭與頻率調節技術

????????從系統架構設計、功能驗證到物理實施過程,用傳統的分段設計方案會比較復雜,但如果運用CPF,整個設計流程將變得非常順暢并容易實現。

1、多電源多電壓技術

????????多電源多電壓(MSMV)是一種可以有效降低動態功耗的技術,不少文獻簡稱這種方法為多電壓。所謂多電源,是指不同的邏輯模塊處于不同的電源域中,由不同供電電源供電,包括邏輯和物理多電源供電和多電壓情況。

????????物理布圖階段,在核心區創建相應的電壓域,每個電壓域中只包含屬于該電壓域的模塊或單元。此外,不同的電壓域中的邏輯要與相應的時序庫對應,在時序分析、功耗分析和優化過程中正確選擇相應電壓域的單元庫。如下圖所示:

????????MSMV的布線與單一電壓布線不同,由于存在多個電壓域,應當保證同一電壓域內單元之間的互連線保持在當前的同一電壓域內,并保證不同電壓域之間的互連線不要跨越第三方電壓域,避免不同電壓域之間的影響。如下圖所示

????????多電壓技術的采用使得電路中的某些模塊工作于較低電壓,它們更容易受到電壓降的影響,從而引起時序違例。?對于靜態電壓降效應的解決方法是改進優化電源網絡。對于動態電壓降效應的解決方法是在電源和地線之間插入去耦電容(decoupling capacitance)。當某一瞬態電路中局

部地區大量單元同時發生信號翻轉,極短的時間內引起充放電流增大,導致電源軌道電壓下降,這時去耦電容將為附近的單元提供額外的電流,以減小電源軌道上的電壓降,從而減輕動態電壓降效應對時序的影響。

????????MSMV 設計方法和電源關斷PSO 的物理實現需要使用兩種特別邏輯單元,它們分別是電平轉換單元(level shifter)和隔離單元(isolation cell)?。

????????電平轉換單元不具有邏輯功能,它用于不同電壓值的電壓域PD(power domain)之間信號電平的轉換,通常有兩個供電電壓端口分別連接兩個不同電壓域的供電電壓。

????????隔離單元起不同電壓域之間的電位鉗制與隔離作用。

2、電源關斷(PSO)技術

????????電源關斷技術是降低泄漏功耗的最有效方法,其思想就是通過關斷芯片中暫時不需要的某個區域或者某個子模塊的供電電壓,從而達到減小功耗的目的,它的實現同樣需要引入電壓域的概念。

????????電源關斷思想聽起來較簡單,但實現起來并不那么容易,設計者必須考慮在何處加入門控電壓單元以及如何加入開關來實現關斷。實現對電路的開啟和關斷需要仔細規劃轉換周期電路,以防止電流過沖,避免電路損壞。要統一模擬電路在關斷電路時功耗節省,以及開啟電路時消耗的開關功耗。

????????首先讓我們來考慮可關斷電壓域與常開電壓域。當可關斷電壓域關斷后,應當在其輸出端口插入隔離單元(isolation cell)。隔離單元與電平轉換單元一樣一般都放置在電壓域的邊界處。

????????有些電路設計會同時采用PSO與MSMV技術,這時兩個不同電壓值的電壓域之間不僅需要電平轉換單元而且需要隔離單元,因此有些標準單元庫會提供將這兩種功能組合在一起的單元。?由于不同電路模塊工作在多個電壓域中,在綜合時,MSMV技術的實現需要有相應庫單元的支持,它們通常都可以由標準單元庫供應商提供。進行邏輯綜合時,首先用CPF文檔定義不同電壓域的模塊所使用的工藝庫名稱,在綜合時,分別添加隔離單元和電平轉換,EDA工具會自動選擇定義的單元庫中的標準單元來實現邏輯綜合產生門級網表。

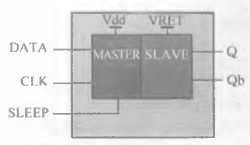

????????保持邏輯模塊處于實現快速喚醒的狀態非常重要,它是指在關斷電源的周期中,將模塊的重要信息保存在存儲器中或使用狀態保持電源門控單元將寄存器數值予以保留。狀態保持電源門控是在原有主從寄存器的基礎上分別使所有主寄存器和從寄存器工作在不同電壓下來實現的。因此PSO的實現需要除了用隔離單元以防止電源關斷后輸出信號的不確定性影響正常工作的電路模塊,還需要有狀態保持電源門控單元。

3、狀態保持電源門控SRPG技術

????????時鐘門控技術和電源關斷技術都是建立在門控制或電壓門的基本原理上。通常有兩種結構的電壓門,一種稱為精細(fine-grain)結構,另一種稱為粗制(coarse-grain)結構。

????????精細結構的思想是在每個標準單元的電源/地和構成邏輯的晶體管間插入多余的晶體管,以切斷電路的泄漏電流。當然更多情況是每個標準單元中由一個晶體管構成電壓門。此外,為了使之能夠承受很大的電流沖擊需要調整門控晶體管的體積,如果門控晶體管設計得太大,不但會增大面積,緊縮布線資源,還加大了延遲,影響電路性能;如果太小,則會影響系統的抗噪聲性能,降低系統可靠性,甚至會導致電路根本無法工作。

????????狀態保持電源門控是一種特殊的寄存器,它屬于精細結構的一種衍生結構,它在傳統的主從寄存器基礎上做了一些改進。通常主觸發器(master FF)的供電電壓由精細結構的電壓門控制,連接正常的電壓值。從觸發器(slave FF)連接一常通的低供電電壓。當電壓關斷后數據被從觸發器保存起來,待重新上電正常工作后再恢復保存值。

????????粗制結構門也稱為全局電壓門,它利用“開關單元”控制整行標準單元電路與電源/地線軌道的連接,從而減小了每個單元的面積和多余的單元端口,但由于“開關單元”控制著整行單元電源地線的連接,所以其晶體管尺寸的選擇比較關鍵,通常開關單元晶體管的寬/長比較大,而且每行單元會采用緩沖鏈依次將其關閉和幵啟,以避免過沖電流燒毀芯片。

4、動態電壓與頻率調節技術

????????隨著近年來輕便型或微型電子設備功能和性能的不斷增強和提高,例如,手提電腦、個人數字助理和手機等對音頻、視頻和圖像的高品質處理能力,電池功耗能力依舊是一項局限,這就使得電源管理功耗技術得到更快的發展。動態電壓與頻率調節(DVFS,dynamic voltage frequency scaling)技術已經在微處理器低功耗設計方面,如在實時處理系統中得到更多的關注。DVFS方法也可以看成是MSV方法的一種擴展。

????????一個典型的DVFS系統的工作流程包括:對系統信號負載采樣,通過相應的算法進行性能計算預測,根據預測結果對電路工作狀態進行DVFS調整,再由電源管理系統實現狀態調節維護。DVFS的調整包括動態電壓調整和時鐘頻率調整,當預測工作頻率將由高到低變化時,先降低頻率,再降低電壓;當預測工作頻率升高時,先升高電壓,再升高頻率。

? ? ? ? 基于硬件的DVFS系統要求每個任務必須在規定的時限內完成,否則視為無效操作。硬件實現一方面增強了負載計算的準確性,另一方面減輕了CPU用于負載跟蹤與性能預測的負擔,但硬件的弊端是缺乏對預測算法選擇的靈活性,電路主要的活動信號與空閑信號被采集后,送到硬件模塊進行性能預測,得到的結果與預先設置的門限進行比較,如果預測的性能需求高于上限,則請求調高頻率;如果預測性能低于下限,則請求降低頻率。這種請求作為一種中斷信號發給控制模塊設置相應的頻率和電壓。

????????DVFS技術在保持系統正常工作的前提下允許動態地調節電路工作電壓和頻率,不僅能夠減小電路的功耗而且延長了電路的使用壽命,目前它是低功耗技術中效益較高又尚未得到完全實施的一項先進技術。DVFS設計方法實現起來比較復雜,它需要在系統級通過架構算法,結合軟件和硬件技術達到要求。

5、襯底偏置技術

????????進入納米設計,泄漏電流對功耗的影響會更加顯著。在MTCMOS技術中,我們討論了通過選擇不同的閾值電壓的方案去降低靜態功耗。由于工藝參數(包括溝道長、溝道寬、絕緣層的厚度)帶來的誤差,使得MTCMOS技術在晶體管的“缺陷”測試分析變得復雜困難。相比之下,在CMOS中采用正向有源區(襯底)偏置(FBB,forward body bias)不僅可以降低泄漏電流,同時對工藝參數的誤差分析也較為簡單。

????????這種改變P區和n 區襯底偏置電壓的方案也稱作襯底偏置(substrate biasing)技術。

????????襯底偏置通過版圖實現有兩種方案:

- 一種為有源阱區(well-tap, body bias)偏置方式,它通常只需要布放在每一排標準單元的兩端或按照一定的間隔布放,它適用于不含well-tap的標準單元庫。其優點是節省面積,但易受閂鎖(latch up)的破壞。

- 另一種為標準單元內置(in-cell tap)偏置方式,每一個標準單元內部均帶有連接偏置電源的端口,它的優點是不會產生閂鎖效應,其缺點是單元面積大,布線比較困難。

- 中斷處理)