DDR SDRAM全稱為Double Data Rate SDRAM,中文名為“雙倍數據流SDRAM”。DDR SDRAM在原有的SDRAM的基礎上改進而來。也正因為如此,DDR能夠憑借著轉產成本優勢來打敗昔日的對手RDRAM,成為當今的主流。本文只著重講講DDR的原理和DDR SDRAM相對于傳統SDRAM(又稱SDR SDRAM)的不同。

?

DDR的核心頻率、時鐘頻率和數據傳輸頻率:

核心頻率就是內存的工作頻率;DDR1內存的核心頻率是和時鐘頻率相同的,到了DDR2和DDR3時才有了時鐘頻率的概念,就是將核心頻率通過倍頻技術得到的一個頻率。數據傳輸頻率就是傳輸數據的頻率。DDR1預讀取是2位,DDR2預讀取是4位,DDR3預讀取是8位。

DDR1在傳輸數據的時候在時鐘脈沖的上升沿和下降沿都傳輸一次,所以數據傳輸頻率就是核心頻率的2倍。DDR2內存將核心頻率倍頻2倍所以時鐘頻率就是核心頻率的2倍了,同樣還是上升邊和下降邊各傳輸一次數據,所以數據傳輸頻率就是核心頻率的4倍。

DDR3內存的時鐘頻率是核心頻率的4倍,所以數據傳輸頻率就是核心頻率的8倍了。

?

一、DDR的基本原理

有很多文章都在探討DDR的原理,但似乎也不得要領,甚至還帶出一些錯誤的觀點。首先我們看看一張DDR正規的時序圖。

從中可以發現它多了兩個信號: CLK#與DQS,CLK#與正常CLK時鐘相位相反,形成差分時鐘信號。而數據的傳輸在CLK與CLK#的交叉點進行,可見在CLK的上升與下降沿(此時正好是CLK#的上升沿)都有數據被觸發,從而實現DDR。在此,我們可以說通過差分信號達到了DDR的目的,甚至講CLK#幫助了第二個數據的觸發,但這只是對表面現象的簡單描述,從嚴格的定義上講并不能這么說。之所以能實現DDR,還要從其內部的改進說起。

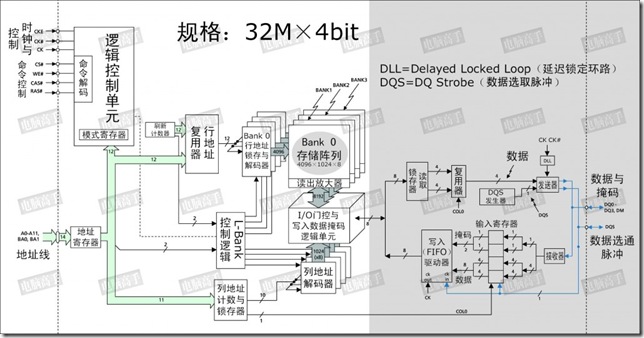

DDR內存芯片的內部結構圖

這是一顆128Mbit的內存芯片,從圖中可以看出來,白色區域內與SDRAM的結構基本相同,但請注意灰色區域,這是與SDRAM的不同之處。首先就是內部的L-Bank規格。SDRAM中L-Bank 存儲單元的容量與芯片位寬相同,但在DDR SDRAM中并不是這樣,存儲單元的容量是芯片位寬的一倍,所以在此不能再套用講解SDRAM時 “芯片位寬=存儲單元容量” 的公式了。也因此,真正的行、列地址數量也與同規格SDRAM不一樣了。

以本芯片為例,在讀取時,L-Bank在內部時鐘信號的觸發下一次傳送8bit的數據給讀取鎖存器,再分成兩路4bit數據傳給復用器,由后者將它們合并為一路4bit數據流,然后由發送器在DQS的控制下在外部時鐘上升與下降沿分兩次傳輸4bit的數據給北橋。這樣,如果時鐘頻率為100MHz,那么在I/O端口處,由于是上下沿觸發,那么就是傳輸頻率就是200MHz。

現在大家基本明白DDR SDRAM的工作原理了吧,這種內部存儲單元容量(也可以稱為芯片內部總線位寬)=2×芯片位寬(也可稱為芯片I/O總線位寬)的設計,就是所謂的兩位預取(2-bit Prefetch),有的公司則貼切的稱之為2-n Prefetch(n代表芯片位寬)。

二、DDR SDRAM與SDRAM的不同

DDR SDRAM與SDRAM的不同主要體現在以下幾個方面。

DDR SDRAM與SDRAM的主要不同對比表

?

DDR SDRAM與SDRAM一樣,在開機時也要進行MRS,不過由于操作功能的增多,DDR SDRAM在MRS之前還多了一EMRS階段(Extended Mode Register Set,擴展模式寄存器設置),這個擴展模式寄存器控制著DLL的有效/禁止、輸出驅動強度、QFC 有效/無效等。

由于EMRS與MRS的操作方法與SDRAM的MRS大同小異,在此就不再列出具體的模式表了,有興趣的話可查看相關的DDR內存資料。下面我們就著重說說DDR SDRAM的新設計與新功能。

1、 差分時鐘

差分時鐘(參見上文“DDR SDRAM讀操作時序圖”)是DDR的一個必要設計,但CK#的作用,并不能理解為第二個觸發時鐘(你可以在講述DDR原理時簡單地這么比喻),而是起到觸發時鐘校準的作用。由于數據是在CK的上下沿觸發,造成傳輸周期縮短了一半,因此必須要保證傳輸周期的穩定以確保數據的正確傳輸,這就要求CK的上下沿間距要有精確的控制。但因為溫度、電阻性能的改變等原因,CK上下沿間距可能發生變化,此時與其反相的CK#就起到糾正的作用(CK上升快下降慢,CK# 則是上升慢下降快)。而由于上下沿觸發的原因,也使CL=1.5和2.5成為可能,并容易實現。與CK反相的CK#保證了觸發時機的準確性。

2、 數據選取脈沖(DQS)

總結DQS:它是雙向信號;讀內存時,由內存產生,DQS的沿和數據的沿對齊;寫入內存時,由外部產生,DQS的中間對應數據的沿,即此時DQS的沿對應數據最穩定的中間時刻。

DQS是DDR SDRAM中的重要功能,它的功能主要用來在一個時鐘周期內準確的區分出每個傳輸周期,并便于接收方準確接收數據。每一顆芯片都有一個DQS信號線,它是雙向的,在寫入時它用來傳送由北橋發來的DQS信號,讀取時,則由芯片生成DQS向北橋發送。完全可以說,它就是數據的同步信號。

在讀取時,DQS與數據信號同時生成(也是在CK與 CK#的交叉點)。而DDR內存中的CL也就是從CAS發出到DQS生成的間隔,數據真正出現在數據I/O總線上相對于DQS觸發的時間間隔被稱為 tAC。注意,這與SDRAM中的tAC的不同。實際上,DQS生成時,芯片內部的預取已經完畢了,tAC是指上文結構圖中灰色部分的數據輸出時間,由于預取的原因,實際的數據傳出可能會提前于DQS發生(數據提前于DQS傳出)。由于是并行傳輸,DDR內存對tAC也有一定的要求,對于 DDR266,tAC的允許范圍是±0.75ns,對于DDR333,則是±0.7ns,有關它們的時序圖示見前文,其中CL里包含了一段DQS的導入期。

前文已經說了DQS是為了保證接收方的選擇數據, DQS在讀取時與數據同步傳輸,那么接收時也是以DQS的上下沿為準嗎?不,如果以DQS的上下沿區分數據周期的危險很大。由于芯片有預取的操作,所以輸出時的同步很難控制,只能限制在一定的時間范圍內,數據在各I/O端口的出現時間可能有快有慢,會與DQS有一定的間隔,這也就是為什么要有一個tAC規定的原因。而在接收方,一切必須保證同步接收,不能有tAC之類的偏差。這樣在寫入時,芯片不再自己生成DQS,而以發送方傳來的DQS為基準,并相應延后一定的時間,在DQS的中部為數據周期的選取分割點(在讀取時分割點就是上下沿),從這里分隔開兩個傳輸周期。這樣做的好處是,由于各數據信號都會有一個邏輯電平保持周期,即使發送時不同步,在DQS上下沿時都處于保持周期中,此時數據接收觸發的準確性無疑是最高的。在寫入時,以DQS的高/低電平期中部為數據周期分割點,而不是上/下沿,但數據的接收觸發仍為DQS的上/下沿。

3、 寫入延遲

在上面的DQS寫入時序圖中,可以發現寫入延遲已經不是0了,在發出寫入命令后,DQS與寫入數據要等一段時間才會送達。這個周期被稱為DQS相對于寫入命令的延遲時間(tDQSS, WRITE Command to the first corresponding rising edge of DQS),對于這個時間大家應該很好理解了。

為什么要有這樣的延遲設計呢?原因也在于同步,畢竟一個時鐘周期兩次傳送,需要很高的控制精度,它必須要等接收方做好充分的準備才行。tDQSS是DDR內存寫入操作的一個重要參數,太短的話恐怕接受有誤,太長則會造成總線空閑。tDQSS最短不能小于0.75個時鐘周期,最長不能超過1.25個時鐘周期。有人可能會說,如果這樣,DQS不就與芯片內的時鐘不同步了嗎?對,正常情況下,tDQSS是一個時鐘周期,但寫入時接受方的時鐘只用來控制命令信號的同步,而數據的接受則完全依靠DQS進行同步,所以 DQS與時鐘不同步也無所謂。不過,tDQSS產生了一個不利影響——讀后寫操作延遲的增加,如果CL=2.5,還要在tDQSS基礎上加入半個時鐘周期,因為命令都要在CK的上升沿發出。

當CL=2.5時,讀后寫的延遲將為tDQSS+0.5個時鐘周期(圖中BL=2)

另外,DDR內存的數據真正寫入由于要經過更多步驟的處理,所以寫回時間(tWR)也明顯延長,一般在3個時鐘周期左右,而在DDR-Ⅱ規范中更是將tWR列為模式寄存器的一項,可見它的重要性。

4、 突發長度與寫入掩碼

在DDR SDRAM中,突發長度只有2、4、8三種選擇,沒有了隨機存取的操作(突發長度為1)和全頁式突發。這是為什么呢?因為L-Bank一次就存取兩倍于芯片位寬的數據,所以芯片至少也要進行兩次傳輸才可以,否則內部多出來的數據怎么處理?而全頁式突發事實證明在PC內存中是很難用得上的,所以被取消也不希奇。

但是,突發長度的定義也與SDRAM的不一樣了(見本章節最前那幅DDR簡示圖),它不再指所連續尋址的存儲單元數量,而是指連續的傳輸周期數,每次是一個芯片位寬的數據。對于突發寫入,如果其中有不想存入的數據,仍可以運用DM信號進行屏蔽。DM信號和數據信號同時發出,接收方在DQS的上升與下降沿來判斷DM的狀態,如果DM為高電平,那么之前從DQS 中部選取的數據就被屏蔽了。有人可能會覺得,DM是輸入信號,意味著芯片不能發出DM信號給北橋作為屏蔽讀取數據的參考。其實,該讀哪個數據也是由北橋芯片決定的,所以芯片也無需參與北橋的工作,哪個數據是有用的就留給北橋自己去選吧。

5、 延遲鎖定回路(DLL)

DDR SDRAM對時鐘的精確性有著很高的要求,而DDR SDRAM有兩個時鐘,一個是外部的總線時鐘,一個是內部的工作時鐘,在理論上DDR SDRAM這兩個時鐘應該是同步的,但由于種種原因,如溫度、電壓波動而產生延遲使兩者很難同步,更何況時鐘頻率本身也有不穩定的情況(SDRAM也內部時鐘,不過因為它的工作/傳輸頻率較低,所以內外同步問題并不突出)。DDR SDRAM的tAC就是因為內部時鐘與外部時鐘有偏差而引起的,它很可能造成因數據不同步而產生錯誤的惡果。實際上,不同步就是一種正/負延遲,如果延遲不可避免,那么若是設定一個延遲值,如一個時鐘周期,那么內外時鐘的上升與下降沿還是同步的。鑒于外部時鐘周期也不會絕對統一,所以需要根據外部時鐘動態修正內部時鐘的延遲來實現與外部時鐘的同步,這就是DLL的任務。

DLL不同于主板上的PLL,它不涉及頻率與電壓轉換,而是生成一個延遲量給內部時鐘。目前DLL有兩種實現方法,一個是時鐘頻率測量法(CFM,Clock Frequency Measurement),一個是時鐘比較法(CC,Clock Comparator)。

CFM是測量外部時鐘的頻率周期,然后以此周期為延遲值控制內部時鐘,這樣內外時鐘正好就相差了一個時鐘周期,從而實現同步。DLL就這樣反復測量反復控制延遲值,使內部時鐘與外部時鐘保持同步。

CFM式DLL工作示意圖

CC的方法則是比較內外部時鐘的長短,如果內部時鐘周期短了,就將所少的延遲加到下一個內部時鐘周期里,然后再與外部時鐘做比較,若是內部時鐘周期長了,就將多出的延遲從下一個內部時鐘中刨除,如此往復,最終使內外時鐘同步。

CC式DLL工作示意圖

CFM與CC各有優缺點,CFM的校正速度快,僅用兩個時鐘周期,但容易受到噪音干擾,并且如果測量失誤,則內部的延遲就永遠錯下去了。CC的優點則是更穩定可靠,如果比較失敗,延遲受影響的只是一個數據(而且不會太嚴重),不會涉及到后面的延遲修正,但它的修正時間要比CFM長。DLL功能在DDR SDRAM中可以被禁止,但僅限于除錯與評估操作,正常工作狀態是自動有效的。

轉自一些論壇:

?

| 1.并行匹配主要是考慮到負載過重,屬于信號完整性的問題;如果接口下就1~2片DDR可以考慮串阻匹配的 2.由于DDR2的電平HSTL電平的,也就是時鐘是偽差分的方式,沒必要按3W做,等長是必要的,最好做VTT |

?

理論上3W,指兩線中心間距=3*線到地平面距離

一般的3W原則,采用的是,兩線中心間距=3*線寬

根據JEDEC[1]建議DDR2的最高工作電壓是1.9V,并且建議對于要求內存穩定使用的環境絕不能超過此值(例如服務器或其他任務關鍵設備)。此外,JEDEC規定內存模塊必須在受到永久損害前承受2.3V的電壓。

歡迎加入硬件QQ群:101 808 3751,一起討論硬件問題,分享調試心得,共同成長。

?

接口,設置TCP的接收與發送超時,Invalid argument錯誤問題)

![[BZOJ1419] Red is good(期望DP)](http://pic.xiahunao.cn/[BZOJ1419] Red is good(期望DP))

)