1. 概述

SPI = Serial Peripheral Interface,是串行外圍設備接口,是一種高速,全雙工,同步的通信總線。常規只占用四根線,節約了芯片管腳,PCB的布局省空間。現在越來越多的芯片集成了這種通信協議,常見的有EEPROM、FLASH、AD轉換器等。

- 優點:

支持全雙工,push-pull的驅動性能相比open-drain信號完整性更好;

支持高速(100MHz以上);

協議支持字長不限于8bits,可根據應用特點靈活選擇消息字長;

硬件連接簡單;

- 缺點:

相比IIC多兩根線;

沒有尋址機制,只能靠片選選擇不同設備;

沒有從設備接受ACK,主設備對于發送成功與否不得而知;

典型應用只支持單主控;

相比RS232 RS485和CAN總線,SPI傳輸距離短;

2. 硬件結構

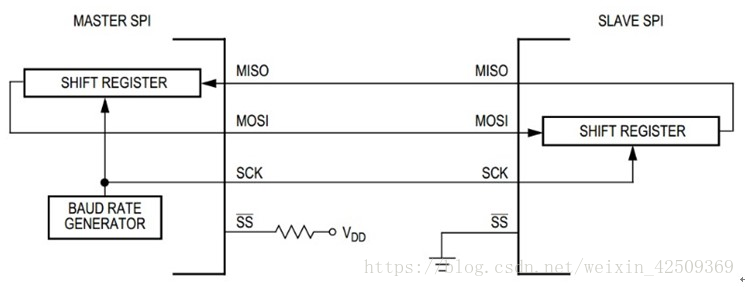

SPI總線定義兩個及以上設備間的數據通信,提供時鐘的設備為主設備Master,接收時鐘的設備為從設備Slave;

- 信號定義如下:

SCK : Serial Clock 串行時鐘

MOSI : Master Output, Slave Input 主發從收信號

MISO : Master Input, Slave Output 主收從發信號

SS/CS : Slave Select 片選信號

- 電路連接如下:

單個主設備和單個從設備:

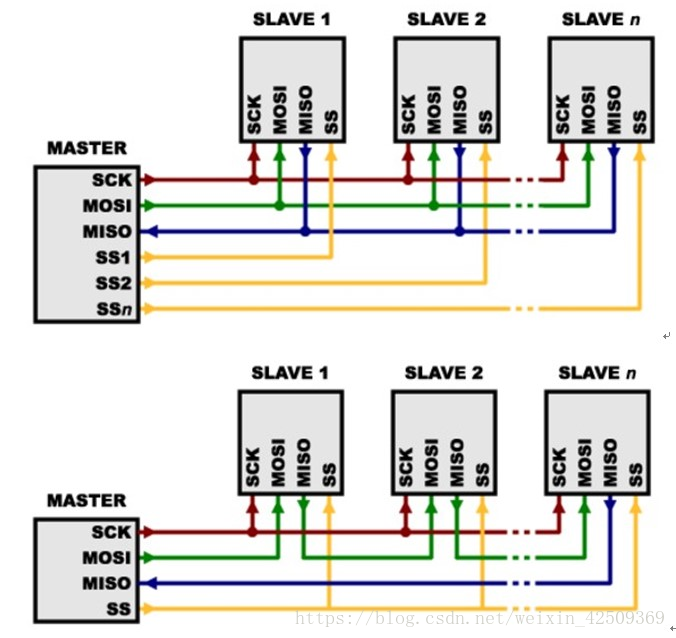

單個主設備和多個從設備,通過多個片選信號或者菊花鏈方式實現:

3. 寄存器類型

Motorola定義的SPI寄存器包括:

SPI Control Register 1 (SPICR1)??? 控制寄存器1

SPI Control Register 2 (SPICR2)??? 控制寄存器2

SPI Baud Rate Register (SPIBR)??? 波特率寄存器

SPI Status Register (SPISR)??????????? 狀態寄存器 ?(只讀?? 其余均可讀可寫)

SPI Data Register (SPIDR)???????????? ?數據寄存器

通過往寄存器中寫入不同的值,設置SPI模塊的不同屬性。

4. SPI傳輸模式

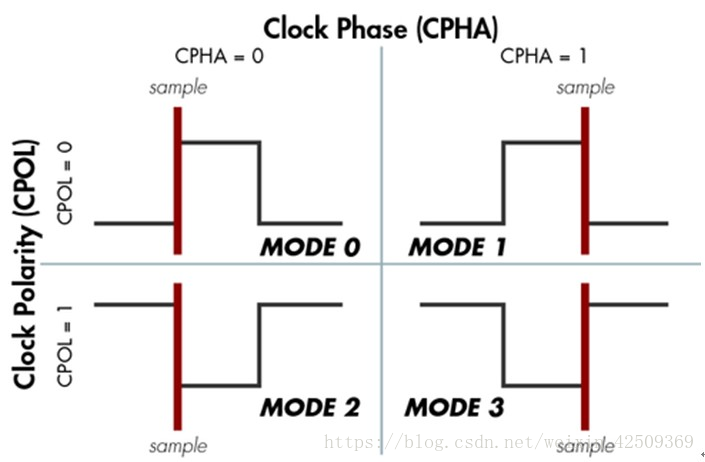

通過設置控制寄存器SPICR1中的CPOL和CPHA位,將SPI可以分成四種傳輸模式。

CPOL,即Clock Polarity,決定時鐘空閑時的電平為高或低。對于SPI數據傳輸格式沒有顯著影響。

1 = 時鐘低電平時有效,空閑時為高

0 = 時鐘高電平時有效,空閑時為低

CPHA,即Clock Phase,定義SPI數據傳輸的兩種基本模式。

1 = 數據采樣發生在時鐘(SCK)偶數(2,4,6,...,16)邊沿(包括上下邊沿)

0 = 數據采樣發生在時鐘(SCK)奇數(1,3,5,...,15)邊沿(包括上下邊沿)

四種模式如下圖所示:

先看第一列兩張圖(CPHA = 0),采樣發生在第一個時鐘跳變沿,即數據采樣發生在SCK奇數邊沿;再看第二列(CPHA =1),采樣發生在第二個時鐘跳變沿,即數據采樣發生在SCK偶數邊沿。

第一行兩張圖,第二行兩張圖(CPOL = 1),SCK空閑狀態為高電平。

主從設備進行SPI通訊時,要確保它們的傳輸模式設置相同。

其中mode0和mode3最為常見,SPI接口的flash中均會有標注。

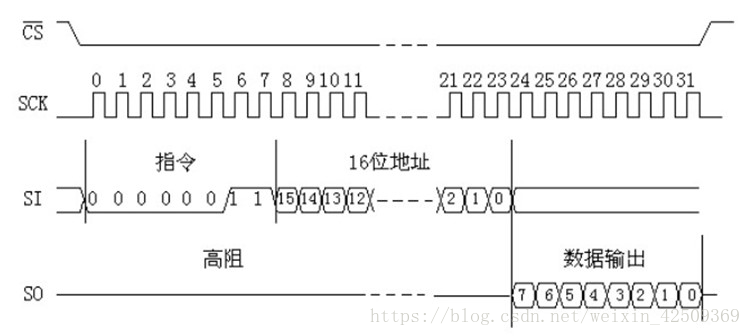

5. 讀寫操作

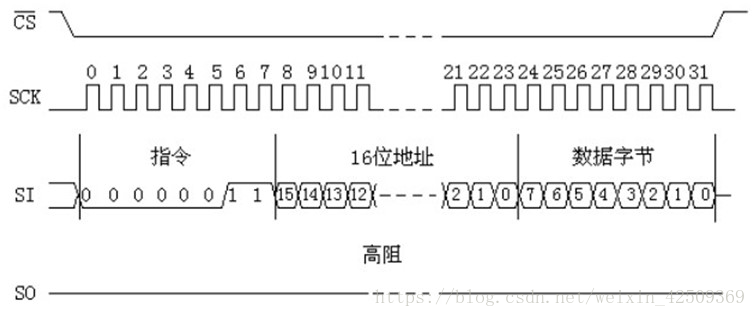

- 標準SPI讀寫為例

片選---讀指令---地址---數據讀出

片選---寫指令---地址---數據寫入

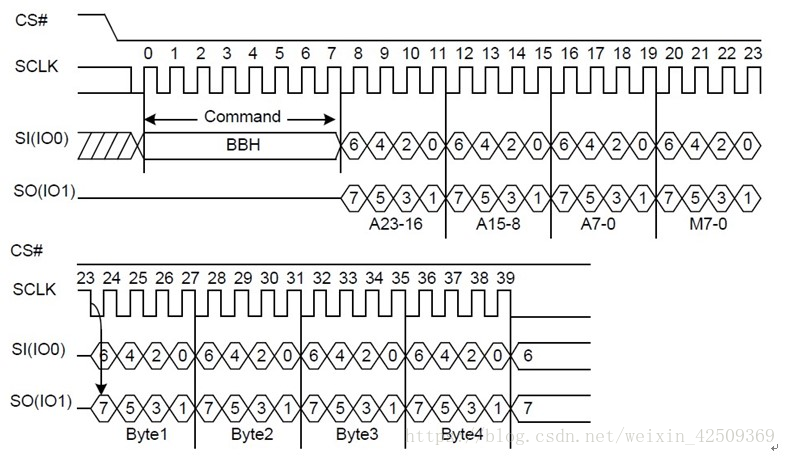

- Dual I/O Fast Read Sequence Diagram? 雙路IO

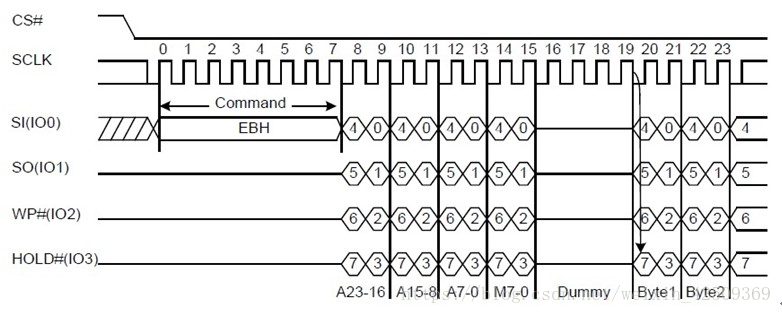

- Quad I/O Fast Read Sequence Diagram? 四路IO

與IIC一樣,是一種最常見的板內芯片間的串行接口。

歡迎加入硬件QQ群:1018083751,一起討論硬件問題,分享調試心得,共同成長。

...)

(dp))

簡介)