文章目錄

- 一、問題描述

- 二、verilog源碼

- 三、仿真結果

一、問題描述

前面介紹4位行波進位全加器(串行加法器)的原理及verilog實現,但是它是一種串行加法器,當位數多時,比如32位的二進制數相加,由于進位逐位從低位向高位傳遞,這會造成相當大的延遲。對于需要快速加法運算的信號處理電路來說,我們需要對其進行改進,一個常見的想法就是將進位提前計算出來,這樣我們可以實現一種稱為超前進位加法器的加法電路。

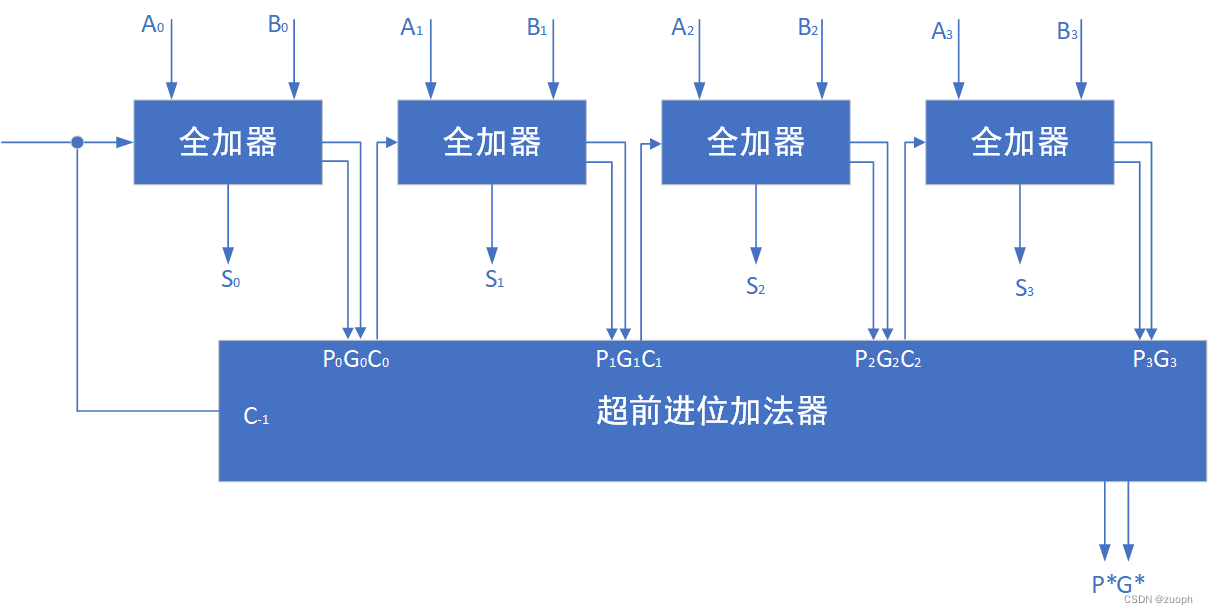

4位超前進位加法器的結構如下圖所示:

其中

Pi=Ai or Bi 稱為進位傳遞函數

Gi=Ai and Bi 稱為進位產生函數

Si=Pi xor Ci

Ci=(Pi and Ci-1) or Gi

根據上述邏輯等式算出各進位的邏輯值:

C0 = cin

C1=G0 + P0·C0

C2=G1 + P1·C1 = G1 + P1·G0 + P1·P0 ?C0

C3=G2 + P2·C2 = G2 + P2·G1 + P2·P1·G0 + P2·P1·P0·C0

C4=G3 + P3·C3 = G3 + P3·G2 + P3·P2·G1 + P3·P2·P1·G0 + P3·P2·P1·P0·C0

cout=C4

二、verilog源碼

module cla_adder4b(input[3:0] a,input[3:0] b,input cin,output[3:

)

![[強網擬態決賽 2023] Crypto](http://pic.xiahunao.cn/[強網擬態決賽 2023] Crypto)

)

)