51單片機的時鐘電路與時序以及 復位電路和電源模式

本文主要涉及51單片機的時鐘電路以及相關時序的知識,也講解了了51單片機的復位電路以及電源模式。

文章目錄

- 51單片機的時鐘電路與時序以及 復位電路和電源模式

- 一、時鐘電路與時序

- 1、 時鐘電路設計

- 1.1 內部時鐘方式

- 1.2 外部時鐘方式

- 1.3 時鐘信號的輸出

- 2、機器周期、指令周期與指令時序

- 二、 復位電路和電源模式

- 1、 復位操作和復位電路

- 1.1 復位操作

- 1.2 復位電路設計

- 2、低功耗節電模式

- 2.1 空閑模式

- 2.2 掉電運行模式

- 2.3 掉電和空閑模式下的WDT

一、時鐘電路與時序

時鐘電路產生AT89S51工作時所必需的控制信號,在時鐘信號的控制下,嚴格按時序執行指令。

執行指令時,CPU首先到程序存儲器中取出需要執行的指令操作碼,然后譯碼,并由時序電路產生一系列控制信號完成指令所規定的操作。

CPU發的時序信號兩類,一類用對片內各個功能部件控制,用戶無須了解;另一類用于對片外存儲器或I/O端口的控制,這部分時序對于分析、設計硬件接口電路至關重要。

1、 時鐘電路設計

時鐘頻率直接影響單片機的速度,時鐘電路的質量也直接影響單片機系統的穩定性。常用的時鐘電路有兩種方式,一種是內部時鐘方式,另一種是外部時鐘方式。

1.1 內部時鐘方式

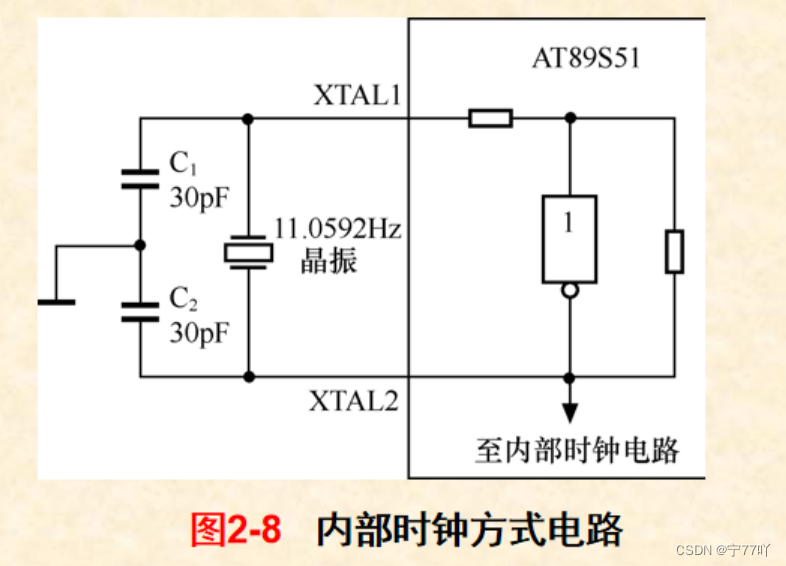

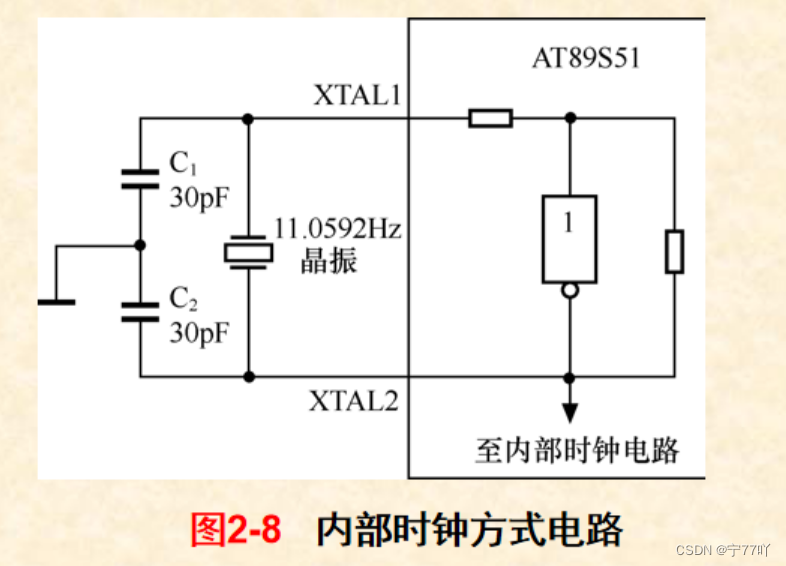

AT89S51內部有一個用于構成振蕩器的高增益反相放大器,輸入端為芯片引腳XTAL1,輸出端為引腳XTAL2。這兩個引腳跨接石英晶體振蕩器和微調電容,構成一個穩定的自激振蕩器,圖2-8是AT89S51內部時鐘方式的電路。

電路中的電容 C1和 C2 的典型值通常選擇為 30pF。晶體振蕩頻率的范圍通常是在1.2~12MHz。

AT89S51單片機常選擇振蕩頻率6MHz或12MHz的石英晶體。

1.2 外部時鐘方式

用現成的外部振蕩器產生脈沖信號,常用于多片AT89S51同時工作,以便于多片AT89S51單片機之間的同步。

外部時鐘源直接接到XTAL1端,XTAL2端懸空,見圖2-9。

1.3 時鐘信號的輸出

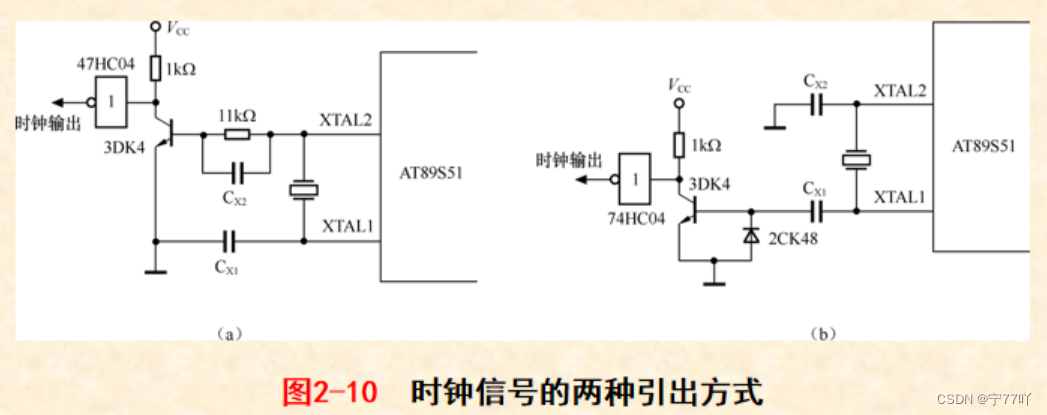

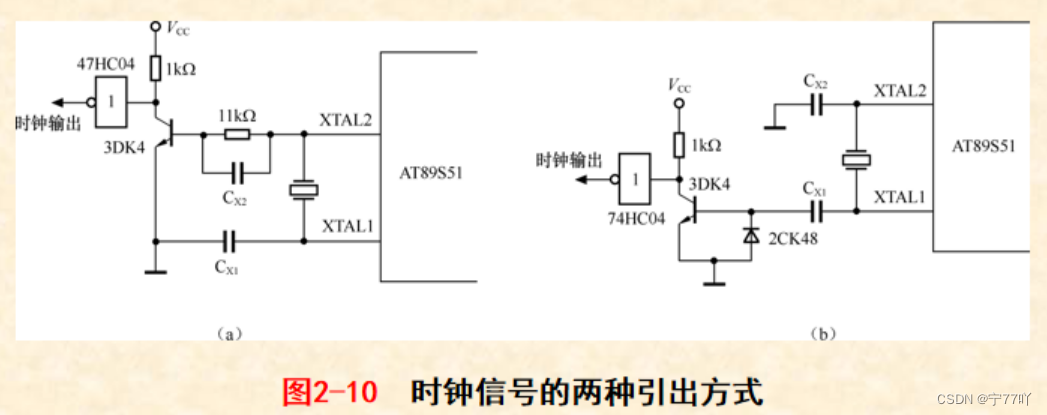

當使用片內振蕩器,XTAL1、XTAL2引腳還能為應用系統中的其他芯片提供時鐘,但需增加驅動能力。其引出的方式有兩種,如圖2-10。

2、機器周期、指令周期與指令時序

各種指令時序與時鐘周期相關。

1.時鐘周期

時鐘控制信號的基本時間單位。若晶振頻率為fosc,則時鐘周期Tosc=1/fosc。

如fosc=6MHz,Tosc=166.7ns。

2.機器周期

CPU完成一個基本操作所需時間為機器周期。執行一條指令分為幾個機器周期。每個機器周期完成一個基本操作,如取指令、讀或寫數據等。每12個時鐘周期為1個機器周期

1個機器周期包括12個時鐘周期,分6個狀態:S1~S6。每個狀態又分兩拍:P1和P2。

因此,一個機器周期中的12個時鐘周期表示為S1P1、S1P2、S2P1、S2P2、…、S6P2,如圖2-11。

3.指令周期

執行一條指令所需的時間。簡單的單字節指令,取出指令立即執行,只需一個機器周期的時間。而有些復雜的指令,如轉移、乘、除指令則需兩個或多個機器周期。

從指令執行時間看:

- 單字節和雙字節指令一般為

單機器周期和雙機器周期; 三字節指令都是雙機器周期;乘、除指令占用4個機器周期。

二、 復位電路和電源模式

1、 復位操作和復位電路

單片機的初始化操作,給復位腳RST加上大于2個機器周期(即24個時鐘振蕩周期)的高電平就使AT89S51復位。

1.1 復位操作

復位時,PC初始化為0000H,程序從0000H單元開始執行。

除系統的正常初始化外,當程序出錯(如程序跑飛)或操作錯誤使系統處于死鎖狀態時,需按復位鍵使RST腳為高電平,使AT89S51擺脫“跑飛”或“死鎖”狀態而重新啟動程序。

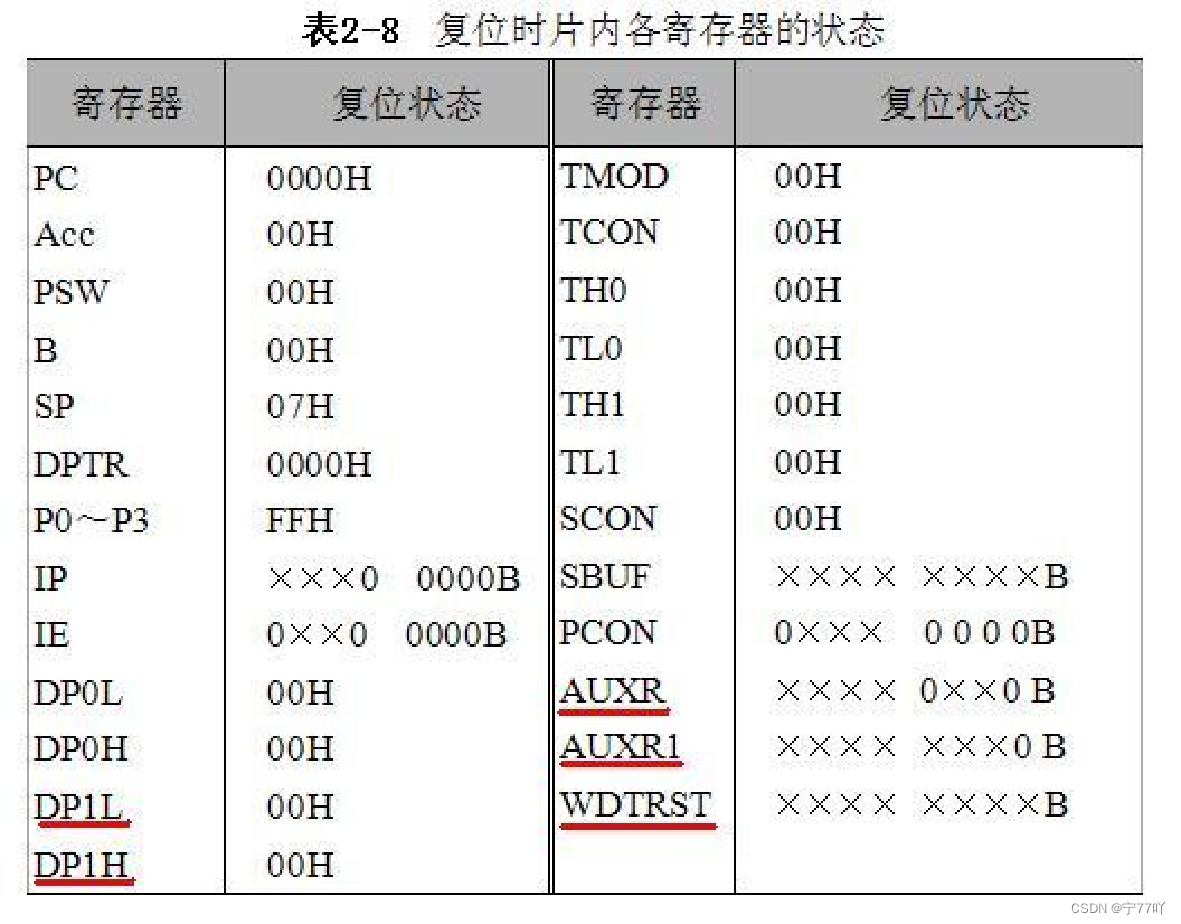

復位操作還對其他一些寄存器有影響,這些寄存器復位時的狀態如表2-8。

1.2 復位電路設計

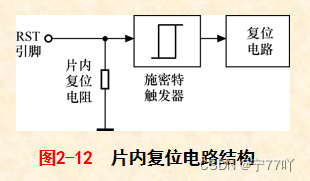

由復位電路實現。AT89S51片內復位電路結構見圖2-12。

復位引腳RST通過一個施密特觸發器與復位電路相連,施密特觸發器用來抑制噪聲,在每個機器周期的S5P2,施密特觸發器的輸出電平由復位電路采樣一次,然后才能得到內部復位操作所需要的信號。

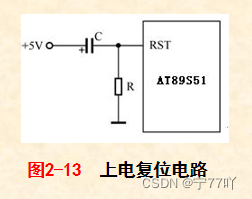

復位電路采用上電自動復位和按鈕復位兩種方式。最簡單的上電自動復位電路如圖2-13所示。

上電自動復位是給電容C充電加給RST引腳一個短的高電平信號,此信號隨著VCC對電容C的充電過程而逐漸回落,即RST引腳上的高電平持續時間取決于電容C充電時間。為保證系統可靠復位,RST引腳上的高電平必須維持足夠長的時間。

除了上電復位外,有時還需要按鍵手動復位。按鍵手動復位有電平和脈沖兩種方式。

2、低功耗節電模式

兩種低功耗節電工作模式:空閑模式(idle mode)和掉電保持模式(power down mode)。

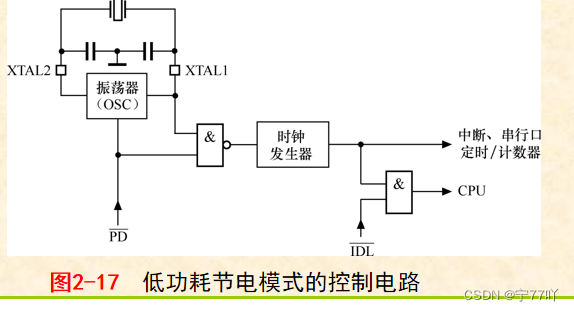

掉電保持模式下,Vcc可由后備電源供電。圖2-17為兩種節電模式的內部控制電路。

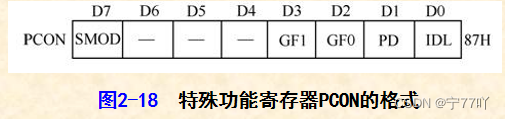

兩種節電模式可通過PCON的位IDL和位PD的設置來實現。

格式如圖2-18。

PCON寄存器各位定義:

SMOD:串行通信波特率選擇。

━ :保留位。

GF1、GF0:通用標志位,兩個標志位用戶使用。

PD: 掉電保持模式控制位,PD=1,則進入掉電保持模式。

IDL:空閑模式控制位,若IDL=1,則進入空閑運行模式。

2.1 空閑模式

-

空閑模式進入

如把PCON中的IDL位置“1”,通往CPU的時鐘信號關斷,便進入空閑模式。雖然振蕩器運行,但是CPU進入空閑狀態。所有外圍電路(中斷系統、串行口和定時器)仍繼續工作,SP、PC、PSW、A、P0–P3端口等所有其他寄存器、內部RAM和SFR中內容均保持進入空閑模式前狀態。 -

空閑模式退出

兩種方法退出,響應中斷方式,硬件復位方式。

空閑模式下,若任一個允許的中斷請求被響應時,IDL位被片內硬件自動清“0”,從而退出空閑模式。當執行完中斷服務程序返回時,將從設置空閑模式指令的下一條指令(斷點處)繼續執行程序。

當使用硬件復位退出空閑模式時,在復位邏輯電路發揮控制作用前,有長達兩個機器周期時間,單片機要從斷點處(IDL位置“1”指令的下一條指令處)繼續執行程序。在這期間,片內硬件阻止CPU對片內RAM的訪問,但不阻止對外部端口(或外部RAM)的訪問。為了避免在硬件復位退出空閑模式時出現對端口(或外部RAM)的不希望的寫入,在進入空閑模式時,緊隨IDL位置1指令后的不應是寫端口(或外部RAM)的指令。

2.2 掉電運行模式

-

掉電模式的進入

用指令把PCON寄存器的PD位置1,便進入掉電模式。在掉電模式下,進入時鐘振蕩器的信號被封鎖,振蕩器停止工作。

由于沒有時鐘信號,內部的所有功能部件均停止工作,但片內RAM和SFR的原來的內容都被保留,有關端口的輸出狀態值都保存在對應的特殊功能寄存器中。 -

掉電模式的退出

兩種方法:硬件復位和外部中斷。

硬件復位時要重新初始化SFR,但不改變片內RAM的內容。只有當Vcc恢復到正常工作水平時,只要硬件復位信號維持10ms,便可使單片機退出掉電運行模式。

2.3 掉電和空閑模式下的WDT

掉電模式下振蕩器停止,意味著WDT也就停止計數。用戶在掉電模式下不需操作WDT。

當用硬件復位退出掉電模式時,對WDT的操作與正常情況一樣。

在系統進入掉電模式前先對寄存器WDTRST復位。在中斷服務程序中復位寄存器WDTRST。

在進入空閑模式前,應先設置AUXR中的WDIDLE位,以確認WDT是否繼續計數。

當WDIDLE=0,空閑模式下的WDT保持繼續計數。為防止復位單片機,用戶可設計一定時器。該定時器使器件定時退出空閑模式,然后復位WDTRST,再重新進入空閑模式。

當WDIDLE=1,WDT在空閑模式下暫停計數,退出空閑模式后,方可恢復計數。

malloc,calloc,realloc函數的介紹使用及柔性數組的介紹)

)

———HTTPS:保護網絡通信安全的關鍵)