SPI通信協議

??SPI協議是由摩托羅拉公司提出的通訊協議(Serial Peripheral Interface),即串行外圍設備接口, 是一種高速全雙工的通信總線。它被廣泛地使用在ADC、LCD等設備與MCU間,要求通訊速率較高的場合。

??學習本章時,可與I2C章節對比閱讀,體會兩種通訊總線的差異以及EEPROM存儲器與FLASH存儲器的區別。下面我們分別對SPI協議的物理層及協議層進行講解。

SPI物理層

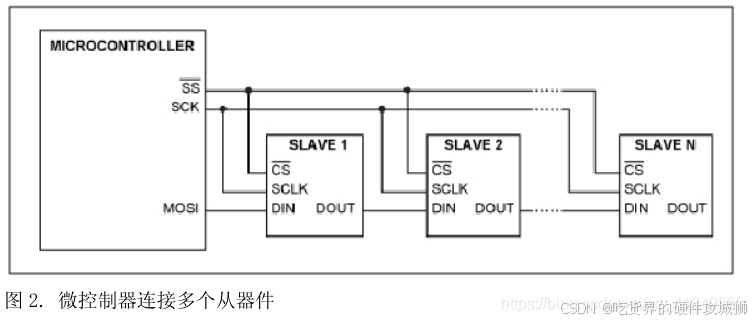

SPI通訊設備之間的常用連接方式見圖

??SPI通訊使用3條總線及片選線,3條總線分別為SCK、MOSI、MISO,片選線為SS,它們的作用介紹如下:

(1) SS ( Slave Select):從設備選擇信號線,常稱為片選信號線,也稱為NSS、CS,以下用NSS表示。當有多個SPI從設備與SPI主機相連時, 設備的其它信號線SCK、MOSI及MISO同時并聯到相同的SPI總線上,即無論有多少個從設備,都共同只使用這3條總線; 而每個從設備都有獨立的這一條NSS信號線,本信號線獨占主機的一個引腳,即有多少個從設備,就有多少條片選信號線。 I2C協議中通過設備地址來尋址、選中總線上的某個設備并與其進行通訊;而SPI協議中沒有設備地址,它使用NSS信號線來尋址, 當主機要選擇從設備時,把該從設備的NSS信號線設置為低電平,該從設備即被選中,即片選有效, 接著主機開始與被選中的從設備進行SPI通訊。所以SPI通訊以NSS線置低電平為開始信號,以NSS線被拉高作為結束信號。

(2) SCK (Serial Clock):時鐘信號線,用于通訊數據同步。它由通訊主機產生,決定了通訊的速率,不同的設備支持的最高時鐘頻率不一樣, 如STM32的SPI時鐘頻率最大為fpclk/2,兩個設備之間通訊時,通訊速率受限于低速設備。

(3) MOSI (Master Output, Slave Input):主設備輸出/從設備輸入引腳。主機的數據從這條信號線輸出, 從機由這條信號線讀入主機發送的數據,即這條線上數據的方向為主機到從機。

(4) MISO (Master Input,,Slave Output):主設備輸入/從設備輸出引腳。主機從這條信號線讀入數據, 從機的數據由這條信號線輸出到主機,即在這條線上數據的方向為從機到主機。

SPI協議層

與I2C的類似,SPI協議定義了通訊的起始和停止信號、數據有效性、時鐘同步等環節。

SPI基本通訊過程

先看看SPI通訊的通訊時序,

??這是一個主機的通訊時序。NSS、SCK、MOSI信號都由主機控制產生,而MISO的信號由從機產生,主機通過該信號線讀取從機的數據。 MOSI與MISO的信號只在NSS為低電平的時候才有效,在SCK的每個時鐘周期MOSI和MISO傳輸一位數據。

以上通訊流程中包含的各個信號分解如下:

1.通訊的起始和停止信號

??在圖 SPI通訊時序 中的標號處,NSS信號線由高變低,是SPI通訊的起始信號。NSS是每個從機各自獨占的信號線, 當從機在自己的NSS線檢測到起始信號后,就知道自己被主機選中了,開始準備與主機通訊。在圖中的標號處,NSS信號由低變高, 是SPI通訊的停止信號,表示本次通訊結束,從機的選中狀態被取消。

2.數據有效性

MSB高位先行,LSB低位先行

??SPI使用MOSI及MISO信號線來傳輸數據,使用SCK信號線進行數據同步。MOSI及MISO數據線在SCK的每個時鐘周期傳輸一位數據, 且數據輸入輸出是同時進行的。數據傳輸時,MSB先行或LSB先行并沒有作硬性規定,但要保證兩個SPI通訊設備之間使用同樣的協定, 一般都會采用圖 SPI通訊時序 中的MSB先行模式。

??觀察圖中的標號處,MOSI及MISO的數據在SCK的上升沿期間變化輸出,在SCK的下降沿時被采樣。即在SCK的下降沿時刻, MOSI及MISO的數據有效,高電平時表示數據“1”,為低電平時表示數據“0”。在其它時刻,數據無效,MOSI及MISO為下一次表示數據做準備。

??SPI每次數據傳輸可以8位或16位為單位,每次傳輸的單位數不受限制。

3.CPOL/CPHA及通訊模式

??上面講述的圖 SPI通訊時序 中的時序只是SPI中的其中一種通訊模式,SPI一共有四種通訊模式, 它們的主要區別是總線空閑時SCK的時鐘狀態以及數據采樣時刻。為方便說明,在此引入“時鐘極性CPOL”和“時鐘相位CPHA”的概念。

??時鐘極性CPOL是指SPI通訊設備處于空閑狀態時,SCK信號線的電平信號(即SPI通訊開始前、 NSS線為高電平時SCK的狀態)。CPOL=0時, SCK在空閑狀態時為低電平,CPOL=1時,則相反。

??時鐘相位CPHA是指數據的采樣的時刻,當CPHA=0時,MOSI或MISO數據線上的信號將會在SCK時鐘線的“奇數邊沿”被采樣。當CPHA=1時, 數據線在SCK的“偶數邊沿”采樣。見圖 CPHA = 0時的SPI通訊模式 及圖 CPHA = 1時的SPI通訊模式 。

??我們來分析這個CPHA=0的時序圖。首先,根據SCK在空閑狀態時的電平,分為兩種情況。 SCK信號線在空閑狀態為低電平時,CPOL=0;空閑狀態為高電平時,CPOL=1。

??無論CPOL=0還是=1,因為我們配置的時鐘相位CPHA=0,在圖中可以看到,采樣時刻都是在SCK的奇數邊沿。 注意當CPOL=0的時候,時鐘的奇數邊沿是上升沿,而CPOL=1的時候,時鐘的奇數邊沿是下降沿。所以SPI的采樣時刻不是由上升/下降沿決定的。 MOSI和MISO數據線的有效信號在SCK的奇數邊沿保持不變,數據信號將在SCK奇數邊沿時被采樣,在非采樣時刻,MOSI和MISO的有效信號才發生切換。

??類似地,當CPHA=1時,不受CPOL的影響,數據信號在SCK的偶數邊沿被采樣,見圖 CPHA=1時的SPI通訊模式_ 。

??由CPOL及CPHA的不同狀態,SPI分成了四種模式,見表 SPI的四種模式 , 主機與從機需要工作在相同的模式下才可以正常通訊,實際中采用較多的是“模式0”與“模式3”。

STM32的SPI特性及架構

與I2C外設一樣,STM32芯片也集成了專門用于SPI協議通訊的外設。

1.STM32的SPI外設簡介

??STM32的SPI外設可用作通訊的主機及從機, 支持最高的SCK時鐘頻率為fpclk/2 (STM32F103型號的芯片默認fpclk1為36MHz, fpclk2為72MHz),完全支持SPI協議的4種模式,數據幀長度可設置為8位或16位, 可設置數據MSB先行或LSB先行。它還支持雙線全雙工(前面小節說明的都是這種模式)、雙線單向以及單線模式。 其中雙線單向模式可以同時使用MOSI及MISO數據線向一個方向傳輸數據,可以加快一倍的傳輸速度。而單線模式則可以減少硬件接線, 當然這樣速率會受到影響。我們只講解雙線全雙工模式。

2. STM32的SPI架構剖析

1.通訊引腳

??SPI的所有硬件架構都從圖 SPI架構圖 中左側MOSI、MISO、SCK及NSS線展開的。STM32芯片有多個SPI外設, 它們的SPI通訊信號引出到不同的GPIO引腳上,使用時必須配置到這些指定的引腳,見表 STM32F10x的SPI引腳 。 關于GPIO引腳的復用功能,可查閱《STM32F10x規格書》,以它為準。

??其中SPI1是APB2上的設備,最高通信速率達36Mbtis/s,SPI2、SPI3是APB1上的設備,最高通信速率為18Mbits/s。除了通訊速率, 在其它功能上沒有差異。其中SPI3用到了下載接口的引腳,這幾個引腳默認功能是下載,第二功能才是IO口,如果想使用SPI3接口, 則程序上必須先禁用掉這幾個IO口的下載功能。一般在資源不是十分緊張的情況下,這幾個IO口是專門用于下載和調試程序,不會復用為SPI3。

2. 時鐘控制邏輯

??SCK線的時鐘信號,由波特率發生器根據“控制寄存器CR1”中的BR[0:2]位控制,該位是對fpclk時鐘的分頻因子, 對fpclk的分頻結果就是SCK引腳的輸出時鐘頻率,計算方法見表 BR位對fpclk的分頻 。

其中的fpclk頻率是指SPI所在的APB總線頻率, APB1為fpclk1,APB2為fpckl2。

通過配置“控制寄存器CR”的“CPOL位”及“CPHA”位可以把SPI設置成前面分析的4種SPI模式。

3. 數據控制邏輯

??SPI的MOSI及MISO都連接到數據移位寄存器上,數據移位寄存器的數據來源及目標接收、發送緩沖區以及MISO、MOSI線。 當向外發送數據的時候,數據移位寄存器以“發送緩沖區”為數據源,把數據一位一位地通過數據線發送出去;當從外部接收數據的時候, 數據移位寄存器把數據線采樣到的數據一位一位地存儲到“接收緩沖區”中。通過寫SPI的“數據寄存器DR”把數據填充到發送緩沖區中, 通訊讀“數據寄存器DR”,可以獲取接收緩沖區中的內容。其中數據幀長度可以通過“控制寄存器CR1”的“DFF位”配置成8位及16位模式; 配置“LSBFIRST位”可選擇MSB先行還是LSB先行。

4. 整體控制邏輯

??整體控制邏輯負責協調整個SPI外設,控制邏輯的工作模式根據我們配置的“控制寄存器(CR1/CR2)”的參數而改變, 基本的控制參數包括前面提到的SPI模式、波特率、LSB先行、主從模式、單雙向模式等等。在外設工作時, 控制邏輯會根據外設的工作狀態修改“狀態寄存器(SR)”,我們只要讀取狀態寄存器相關的寄存器位, 就可以了解SPI的工作狀態了。除此之外,控制邏輯還根據要求,負責控制產生SPI中斷信號、DMA請求及控制NSS信號線。

??實際應用中,我們一般不使用STM32 SPI外設的標準NSS信號線,而是更簡單地使用普通的GPIO,軟件控制它的電平輸出,從而產生通訊起始和停止信號。

3.通訊過程

??STM32使用SPI外設通訊時,在通訊的不同階段它會對“狀態寄存器SR”的不同數據位寫入參數,我們通過讀取這些寄存器標志來了解通訊狀態。

??圖 主發送器通訊過程 中的是“主模式”流程,即STM32作為SPI通訊的主機端時的數據收發過程。

主模式收發流程及事件說明如下:

(1) 控制NSS信號線, 產生起始信號(圖中沒有畫出);

(2) 把要發送的數據寫入到“數據寄存器DR”中, 該數據會被存儲到發送緩沖區;

(3) 通訊開始,SCK時鐘開始運行。MOSI把發送緩沖區中的數據一位一位地傳輸出去; MISO則把數據一位一位地存儲進接收緩沖區中;

(4) 當發送完一幀數據的時候,“狀態寄存器SR”中的“TXE標志位”會被置1,表示傳輸完一幀,發送緩沖區已空;類似地, 當接收完一幀數據的時候,“RXNE標志位”會被置1,表示傳輸完一幀,接收緩沖區非空;

(5) 等待到“TXE標志位”為1時,若還要繼續發送數據,則再次往“數據寄存器DR”寫入數據即可;等待到“RXNE標志位”為1時, 通過讀取“數據寄存器DR”可以獲取接收緩沖區中的內容。

??假如我們使能了TXE或RXNE中斷,TXE或RXNE置1時會產生SPI中斷信號,進入同一個中斷服務函數,到SPI中斷服務程序后, 可通過檢查寄存器位來了解是哪一個事件,再分別進行處理。也可以使用DMA方式來收發“數據寄存器DR”中的數據。

4.實戰——讀寫串行FLASH

1.硬件連接

注意:

如果SPI通訊中的三個從機都是推挽輸出(Push-Pull Output),那么在沒有適當管理的情況下,當多個從設備同時驅動MISO線時,就會發生線路沖突,這可能導致數據錯誤和通信故障。為了解決這個問題,【從機】一般采用下面的處理方式:

片選(Chip Select):每個從設備都有一個獨立的片選線,用于啟用或禁用該設備的輸出。當主設備想要與某個從設備通信時,它會通過激活相應的片選線來選擇該從設備。未被選中的從設備會將其MISO輸出設置為高阻態(High-Impedance),從而不會對MISO線產生影響。

2.軟件設計

編程要點:

- 初始化通訊使用的目標引腳及端口時鐘;

- 使能SPI外設的時鐘;

- 配置SPI外設的模式、地址、速率等參數并使能SPI外設;

- 編寫基本SPI按字節收發的函數;

- 編寫對FLASH擦除及讀寫操作的的函數;

- 編寫測試程序,對讀寫數據進行校驗。

擴展1:SPI物理層第二種連接方式:菊花鏈

在數字通信世界中,在設備信號(總線信號或中斷信號)以串行的方式從一 個設備依次傳到下一個設備,不斷循環直到數據到達目標設備的方式被稱為菊花鏈。

菊花鏈的最大缺點是因為是信號串行傳輸,所以一旦數據鏈路中的某設備發生故障的時候,它下面優先級較低的設備就不可能得到服務了;

另一方面,距離主機越遠的從機,獲得服務的優先級越低,所以需要安排好從機的優先級,并且設置總線檢測器,如果某個從機超時,則對該從機進行短路,防止單個從機損壞造成整個鏈路崩潰的情況;

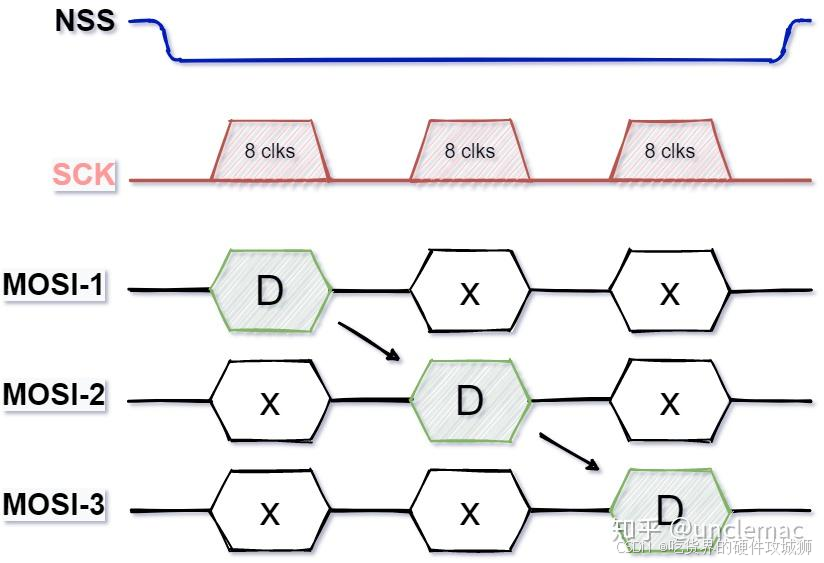

具體的連接如下圖所示:

采用一個/SS (或者/CS) 信號控制所有從器件的/CS 輸入; 所有從器件接收同一個時鐘信號。只有鏈上的第一個從器件(SLAVE 1) 從微控制器直接接收命令。 其他所有從器件都從鏈上前一個器件的 DOUT 輸出獲得其 DIN 數據。要保證菊鏈正常工作, 每一個從器件就必須能在給定的命令周期內(定義為每一個命令所需的時鐘數) 從 DIN 引腳讀入命令, 而在下一個命令周期從 DOUT 引腳輸出同樣的命令。 顯然,從 DIN 到 DOUT 會有一個命令周期的延遲。 另外, 各個從器件只能在/CS 的上升沿執行寫入的命令。 這意味著只要/CS 保持低電平, 從器件將不會執行命令, 并且會在下一個命令周期將命令通過 DOUT 引腳輸出。 如果在給定命令周期之后/CS 變高, 所有從器件將立即執行寫入 DIN 引腳的命令。 如果/CS 變高, 數據將不會從 DOUT 輸出, 這就使得鏈上每個從器件可以執行不同的命令。只要菊鏈的這些要求能夠滿足, 微控制器只需三個信號(/SS、SCK 和 MOSI)就能控制網絡上的所有從器件。

所以最終的數據流向圖可以表示為:

SCK為時鐘信號,8clks表示8個邊沿信號;

其中D為數據,X為無效數據

所以不難發現,菊花鏈模式充分使用了SPI其移位寄存器的功能,整個鏈充當通信移位寄存器,每個從機在下一個時鐘周期將輸入數據復制到輸出。

詳細原理請看:SPI菊花鏈原理和配置

擴展2:關于stm32硬件spi的MISO口配置

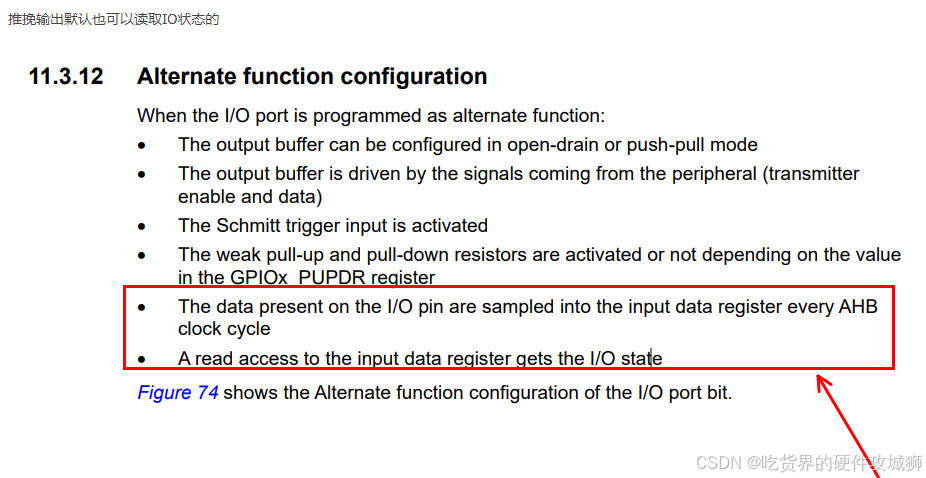

在我們剛使用spi時,對于spi的io口配置可能會有一些疑惑吧,miso明明是一個輸入口卻配置成了復用推挽輸出,是不是會有一點疑惑呢?

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_4 | GPIO_Pin_5 | GPIO_Pin_6 | GPIO_Pin_7;GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP; // 復用的推挽輸出

MISO不是應該設置成為輸入端口(GPIO_Mode_IN_FLOATING)才行的嗎?其實可以設置成為輸入模式,也可以設置成為復用的推挽輸出。其工作都是正常的,不過建議大家還是設置成為輸入端口的好,容易理解。

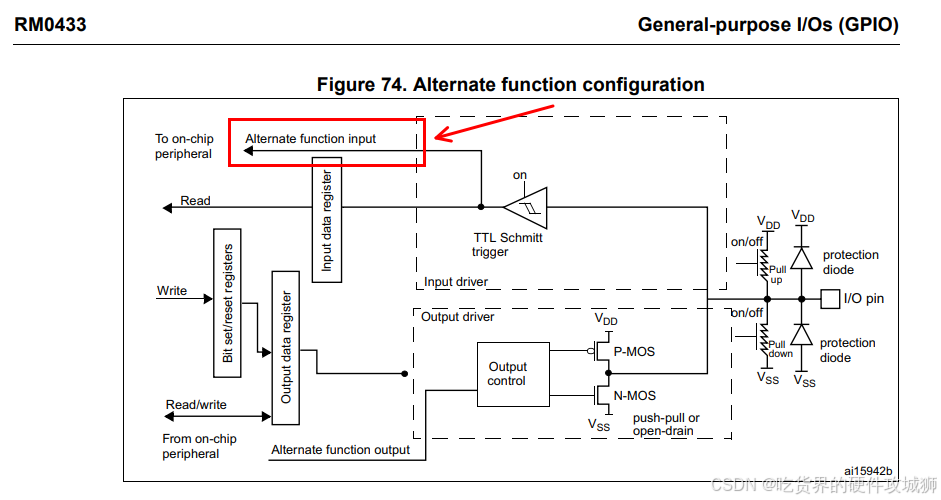

具體產生這一問題的原因是:從功能上來說,MISO應該配置為輸入模式才對,但為什么也可以配置為GPIO_Mode_AF_PP?請看下面的GPIO復用功能配置框圖。當一個GPIO端口配置為GPIO_Mode_AF_PP是,這個端口的內部結構框圖如下:圖中可以看到,片上外設的復用功能輸出信號會連接到輸出控制電路,然后在端口上產生輸出信號。但是在芯片內部,MISO是SPI模塊的輸入引腳,而不是輸出引腳,也就是說圖中的"復用功能輸出信號"根本不存在,因此"輸出控制電路"不能對外產生輸出信號。而另一方面看,即使在GPIO_Mode_AF_PP模式下,復用功能輸入信號卻與外部引腳之間相互連接,既MISO得到了外部信號的電平,實現了輸入的功能。

SPI協議詳解(圖文并茂+超詳細)

關于stm32硬件spi的miso口配置

![[實戰]調頻(FM)和調幅(AM)信號生成(完整C語言實現)](http://pic.xiahunao.cn/[實戰]調頻(FM)和調幅(AM)信號生成(完整C語言實現))

迭代法)

)

)