目錄

1. 簡介

1.1 EVB 介紹

1.2 Si5338 Block Diagram

2. EVB 詳解

2.1 實物圖

2.2 基本配置

2.2.1 Universal Pin

2.2.2 IIC I/F

2.2.3 Input Clocks

2.2.4 Output Frequencies

2.2.5 Output Driver

2.2.6 Freq and Phase Offset

2.2.7 Spread Spectrum

2.2.8 快速參考手冊

2.3 可編程電壓

2.3.1 GUI 配置

2.3.2 原理解析

2.3.3?AD5263

2.3.4?MAX8869

2.4?供電

2.4.1 VDD

2.4.2?VDDOn

3. Si5338

3.1 Input Stage

3.1.1 Diagram

3.1.2 時鐘輸入

3.1.3 自由晶振

3.1.4 單端至差分

3.2?Output Stage

3.2.1 Diagram

3.2.2?Output CLK Info

3.2.3?Output Volt Info

3.3 LVDS

3.4?ECL

3.4.1 ECL 系列

3.4.2 輸入輸出級

3.4.3 DC 耦合

3.4.4 AC 耦合

3.5 CML

3.6?HCSL

3.7 SSTL

3.8 HSTL

4. 總結

1. 簡介

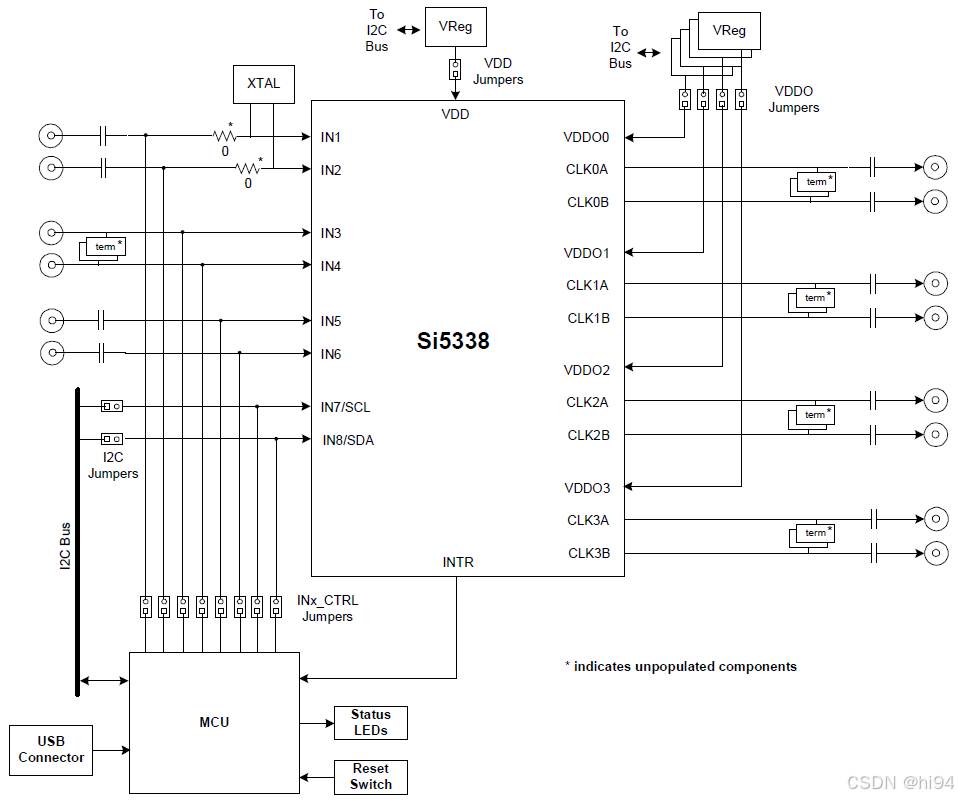

1.1 EVB 介紹

- EVB 包含一個 MCU,用于實現 USB 至 I2C 的信號轉換,兼具電壓調節器控制、中斷引腳監測和四路狀態 LED 控制功能。

- 當配置 INx_CTRL 跳線時,還可對八路輸入引腳進行控制。板上設五組可編程電壓調節器(含VDD、VDDO0-3),為 Si5338 芯片供電。

- VDD 和 VDDO 跳線可切換至外接電源供電模式,亦提供便捷的電流測量接入點。

- IIC 跳線可斷開 EVB 與 Si5338 器件的總線連接,供其他 IIC 主控設備實施外部控制。

- EVB 板載 25MHz 晶振,支持獨立異步工作模式。

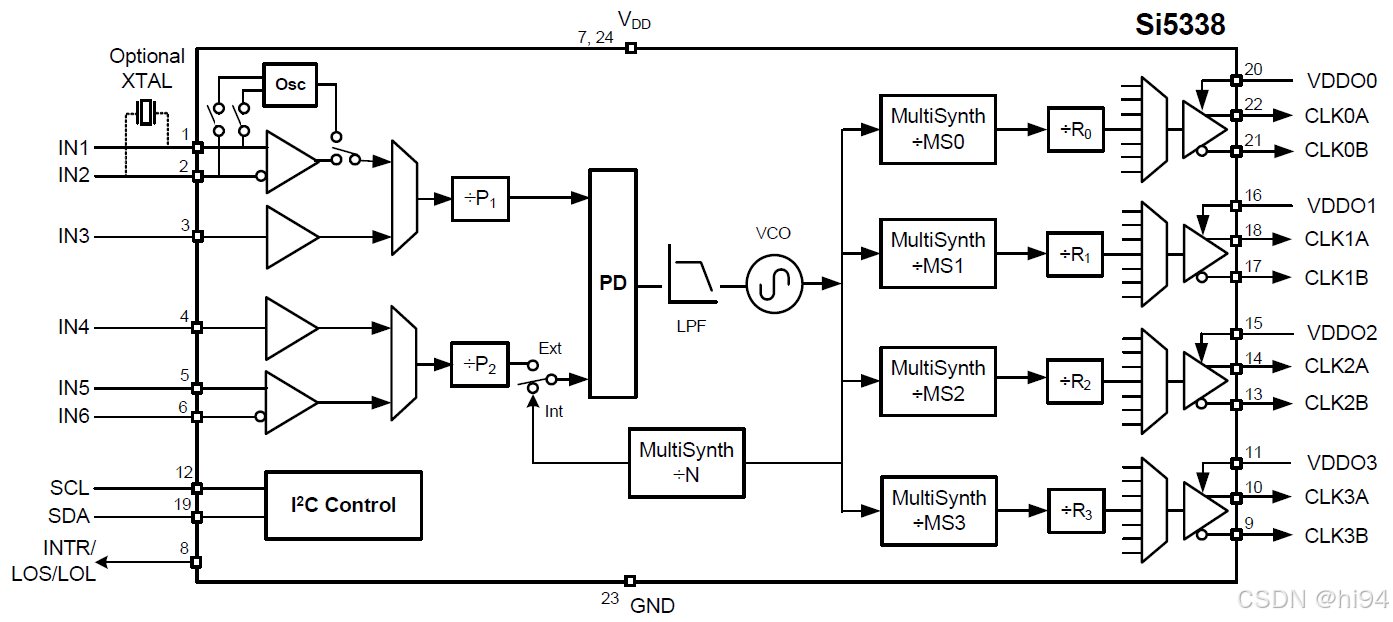

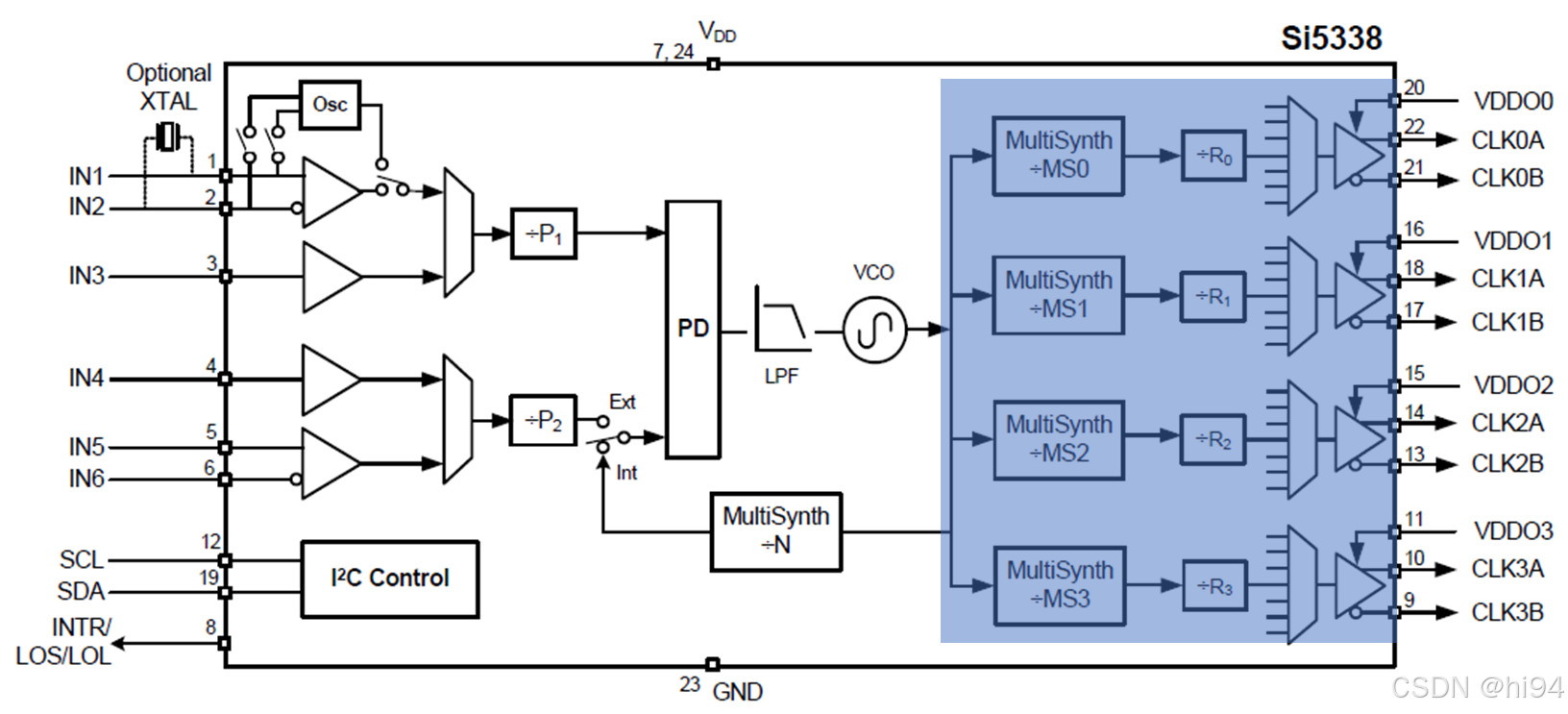

1.2 Si5338 Block Diagram

2. EVB 詳解

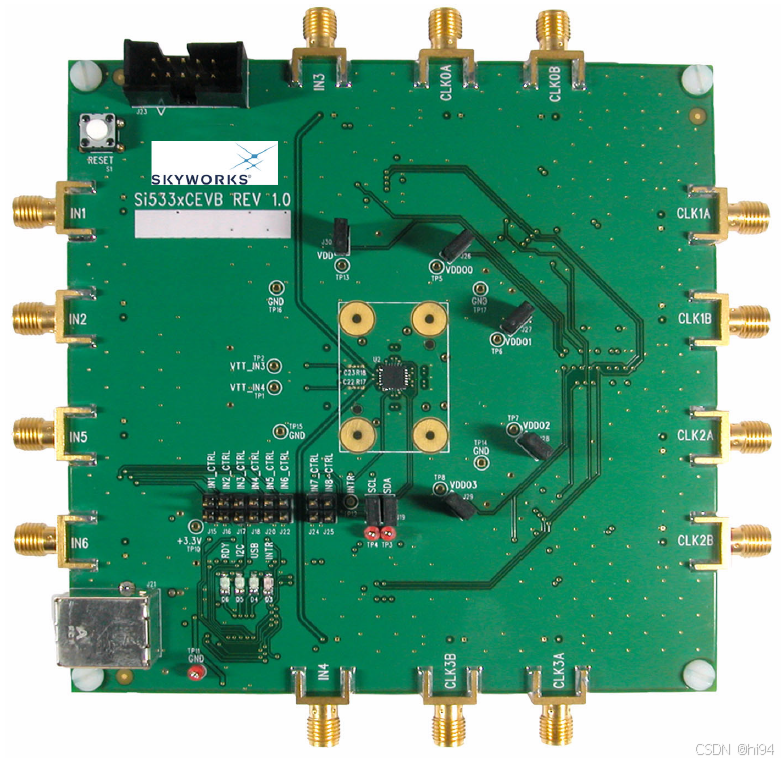

2.1 實物圖

2.2 基本配置

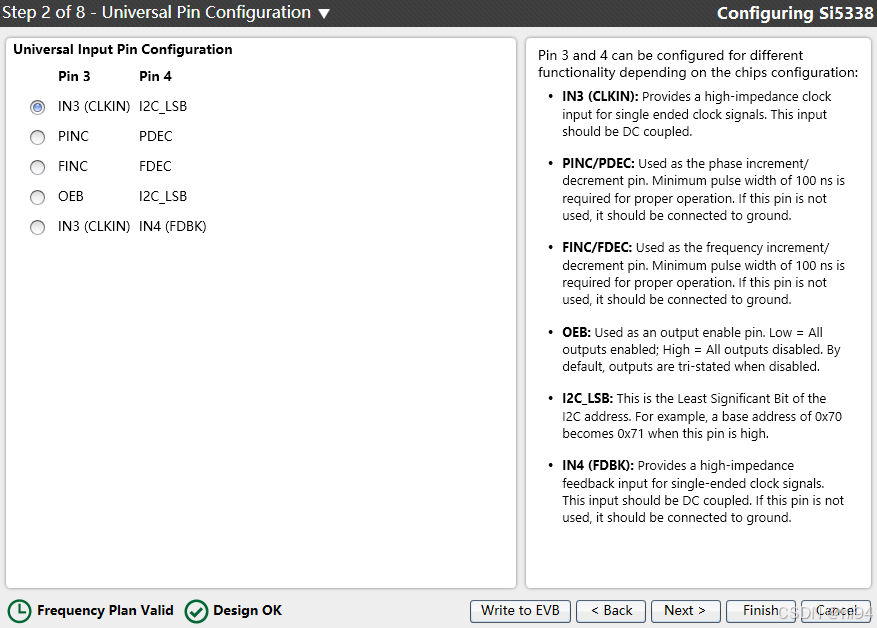

2.2.1 Universal Pin

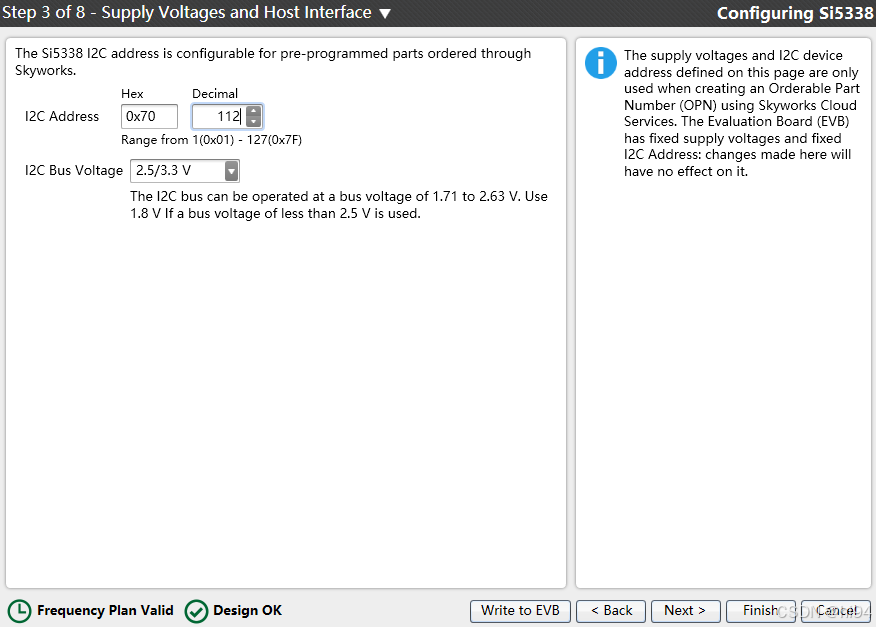

2.2.2 IIC I/F

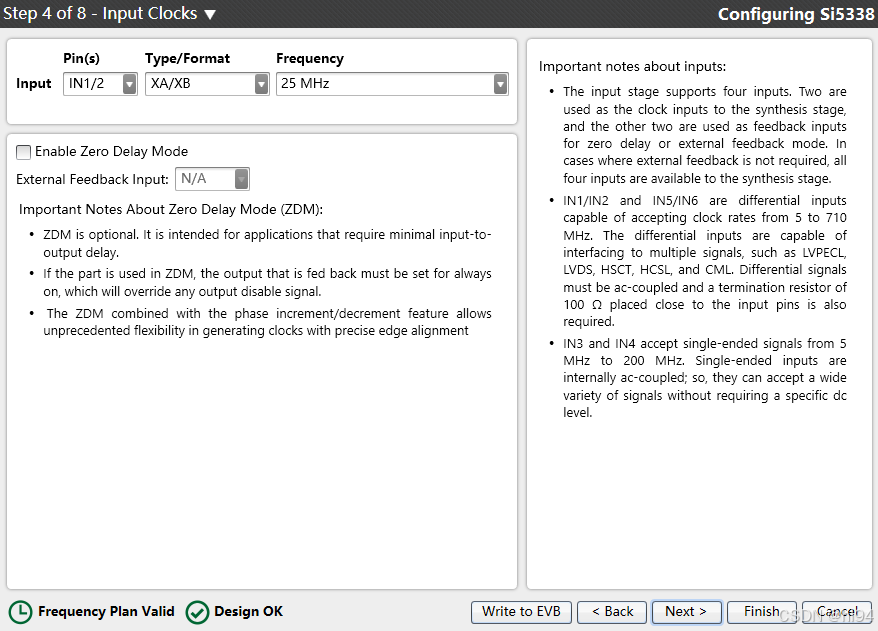

2.2.3 Input Clocks

EVB 板載晶振為?25MHz。

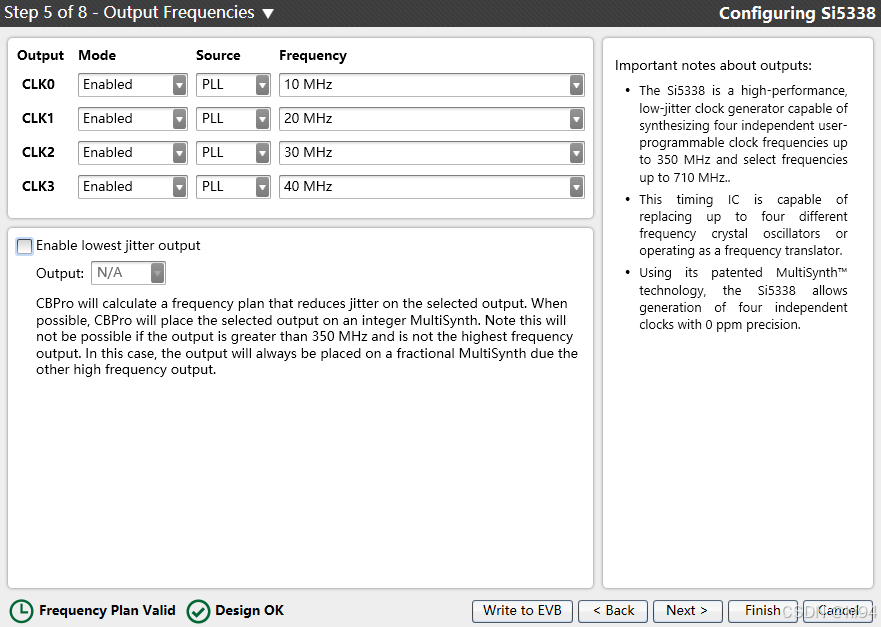

2.2.4 Output Frequencies

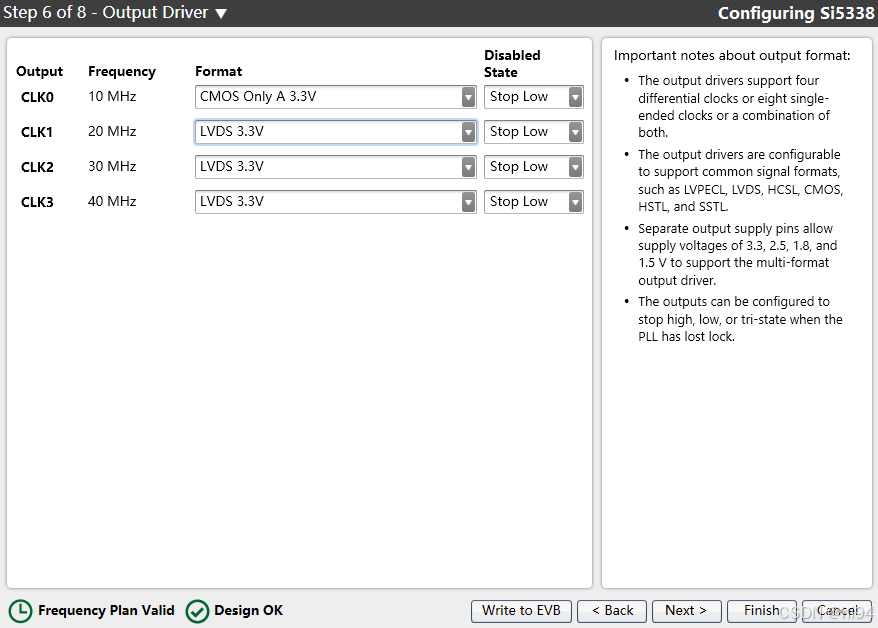

2.2.5 Output Driver

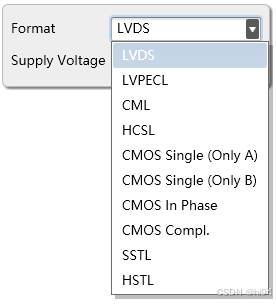

可選項:

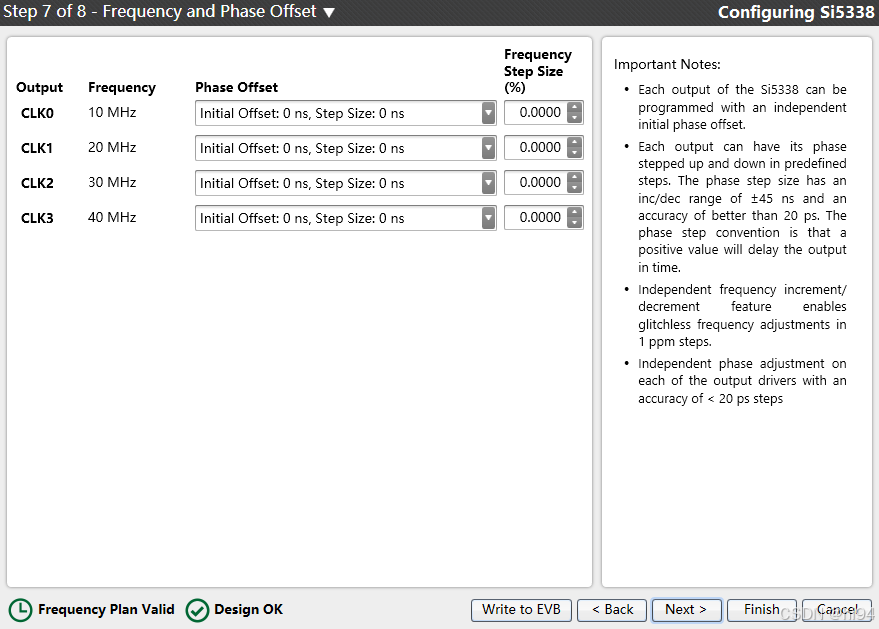

2.2.6 Freq and Phase Offset

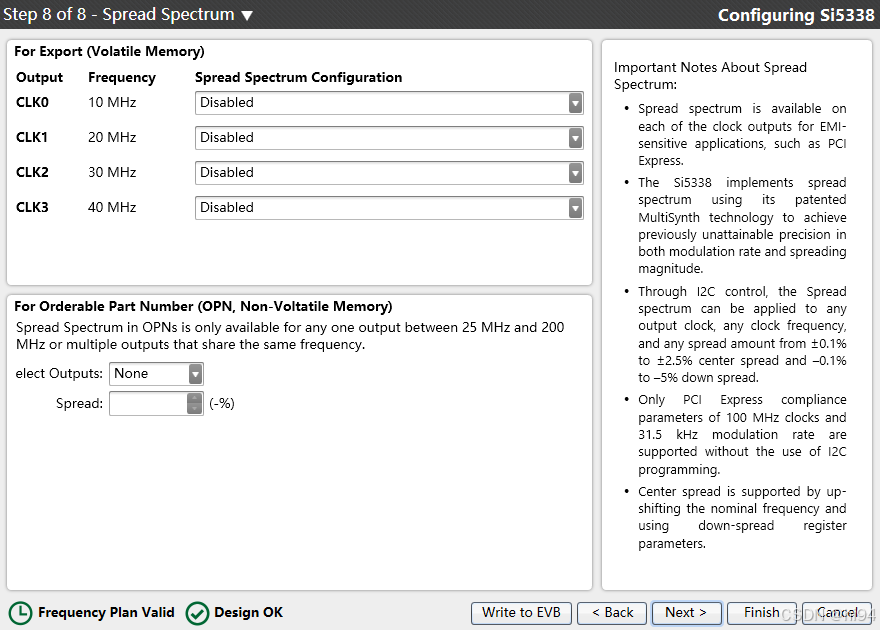

2.2.7 Spread Spectrum

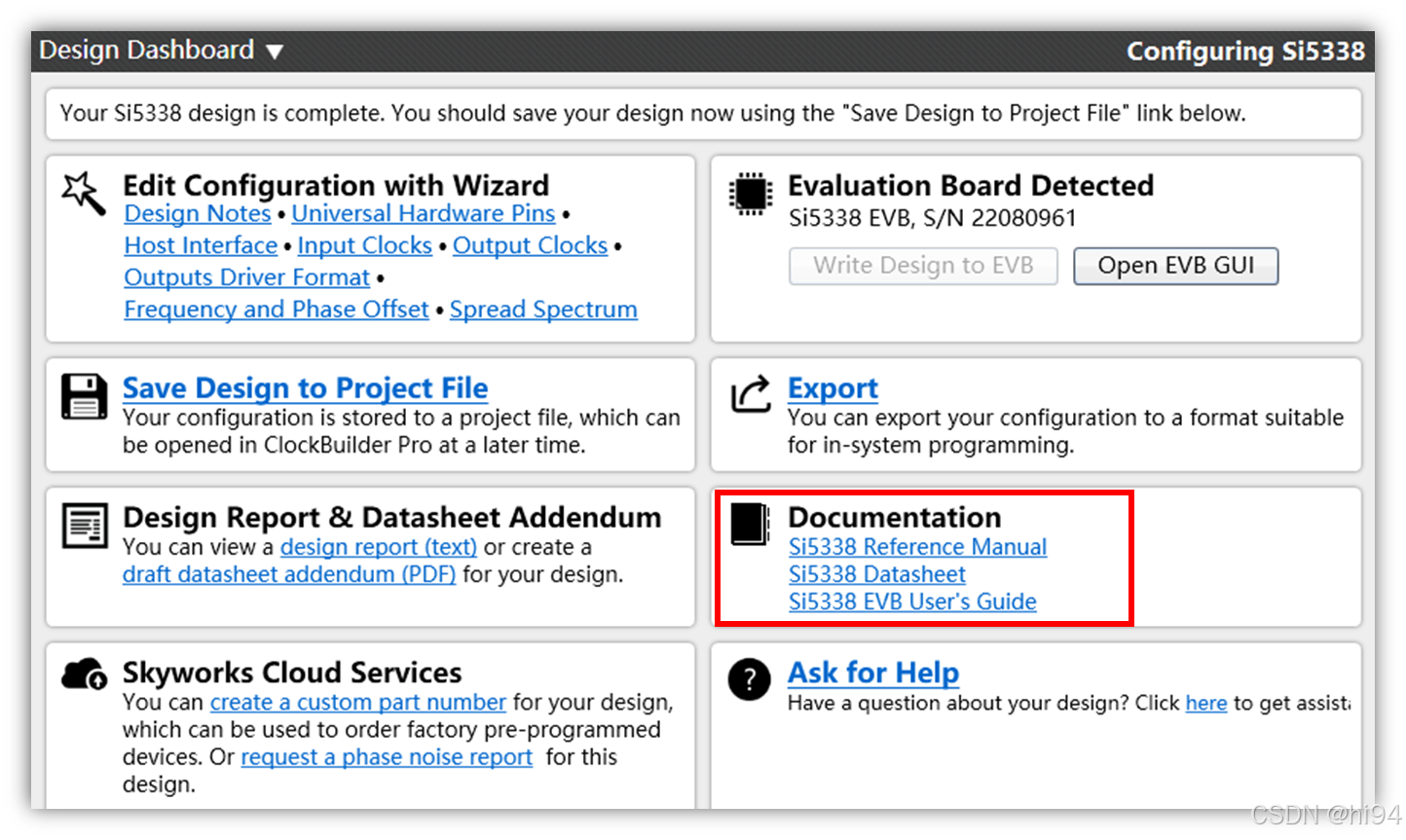

2.2.8 快速參考手冊

2.3 可編程電壓

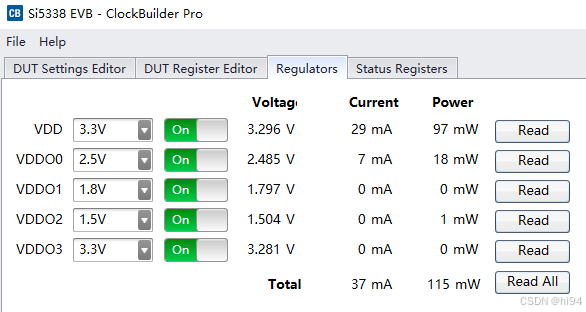

2.3.1 GUI 配置

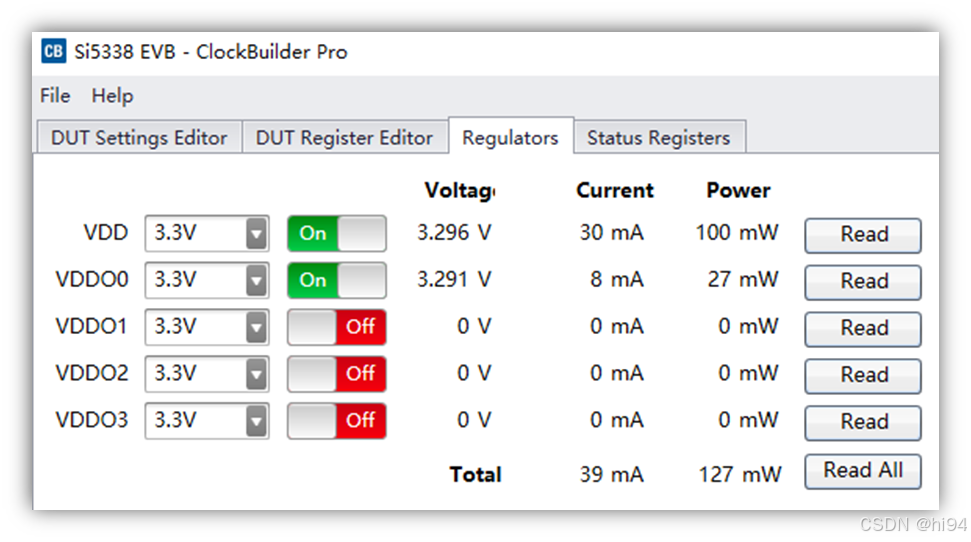

可通過 GUI 編程設定 VDD 供電電壓(3.3V、2.5V、1.8V)。

可通過 GUI 獨立配置四個輸出的 VDDO 電壓(3.3V、2.5V、1.8V、1.5V)。

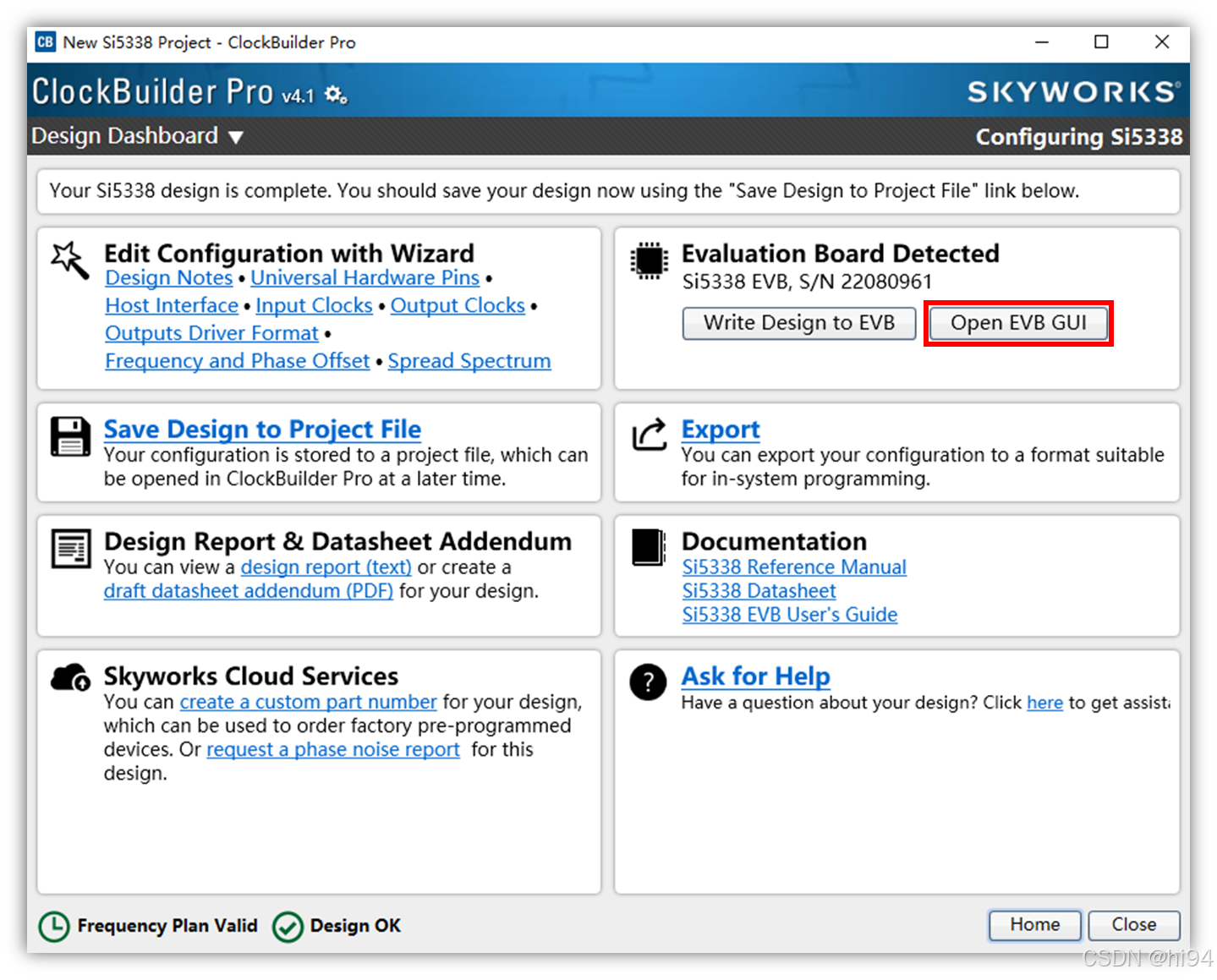

1)在 Design Dashboard 中,選擇 Open EVB GUI

2)在 Si5338 EVB 中,選擇 Regulators

2.3.2 原理解析

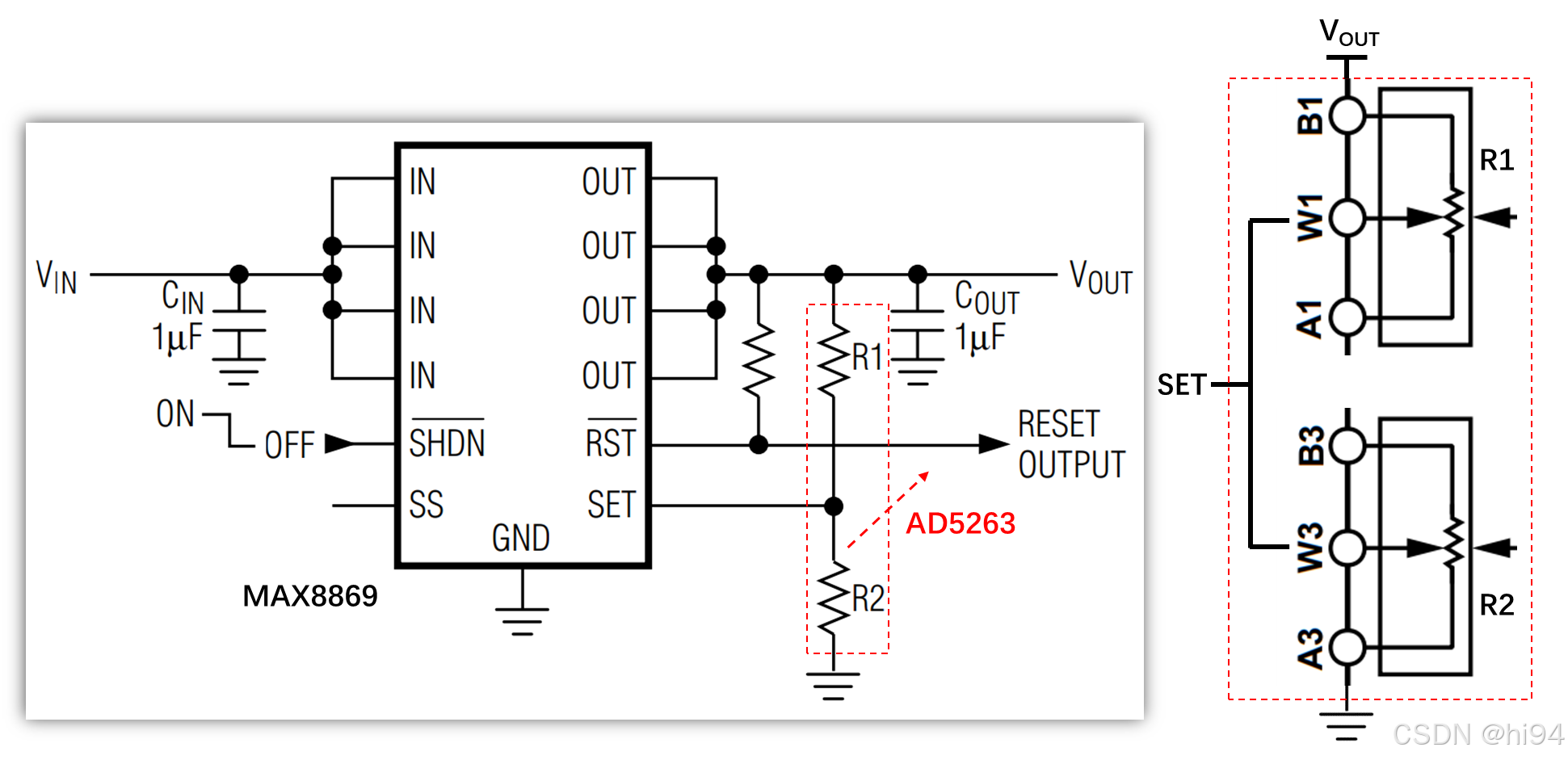

1)示意圖

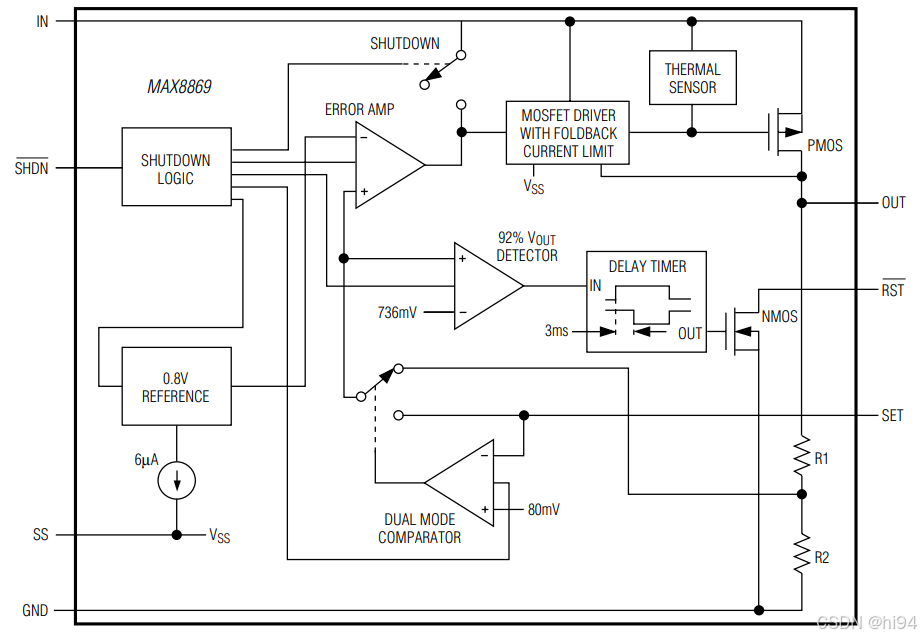

VOUT = Vset × (1 + R1 / R2)?,其中 Vset = 0.8V

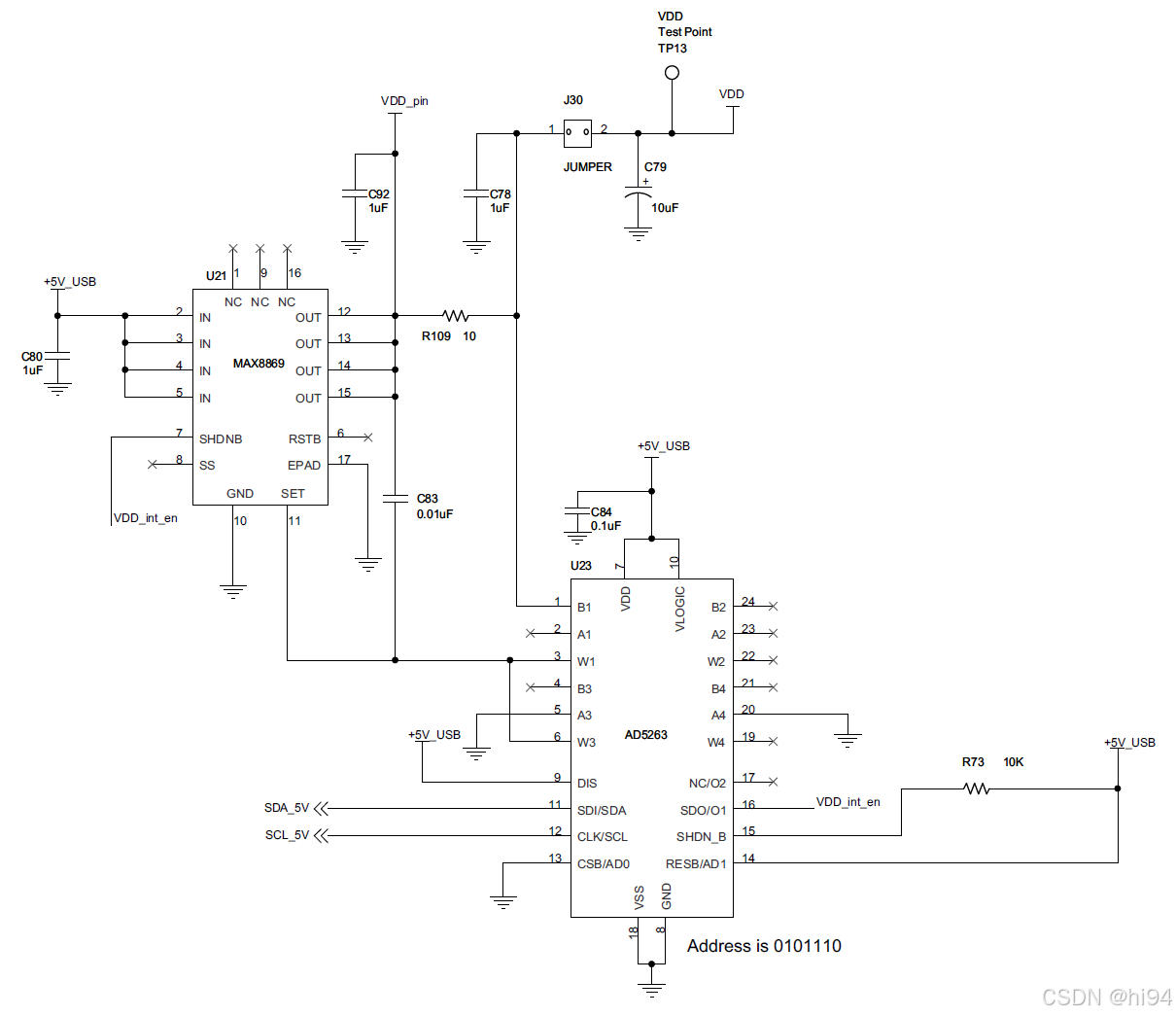

2)原理圖

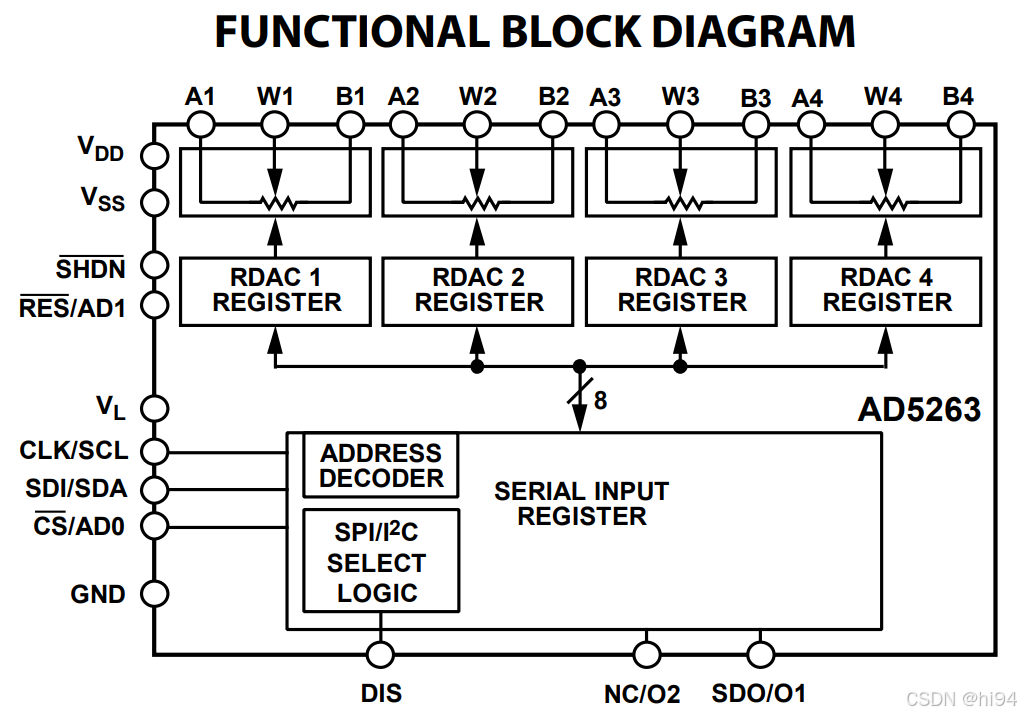

2.3.3?AD5263

一個四通道、15 V、256 位數字電位計,提供引腳可選的 SPI/I2C,它可實現與機械電位計或可變電阻相同的電子調整功能,具備低溫度系數。

- 溫度系數(變阻器模式):30 ppm/°C

- 溫度系數(分壓器模式):5 ppm/°C

- 供電:可采用 +4.5V 至 +15V 或 ±5V 電源供電

系統上電后,游標位默認為中量程。游標位可通過口進行編程設置。

I2C 模式下,用戶可以利用附加可編程邏輯輸出,驅動其系統中的數字負載、邏輯門和模擬開關。

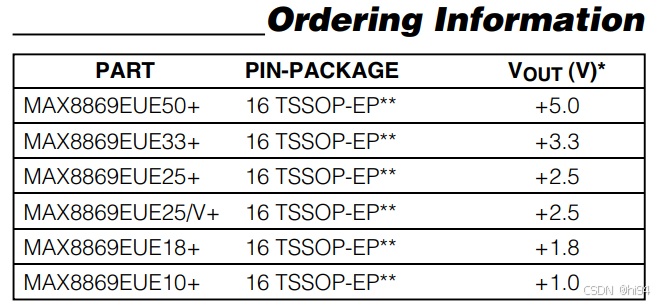

2.3.4?MAX8869

低壓差線性穩壓器

輸出電壓精度 ±1%,預設為 +5V、+3.3V、+2.5V、+1.8V、+1.0V,也可通過外部電阻分壓器在+0.8V 至 +5V 范圍內調節。

2.4?供電

2.4.1 VDD

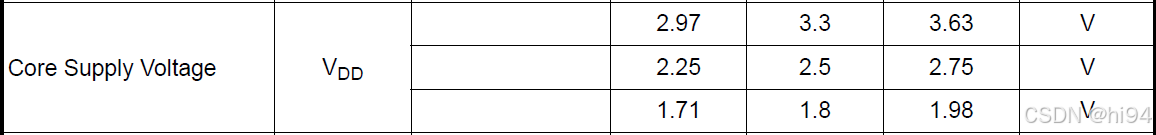

1)VDD:內核供電電壓,支持?1.8V、2.5V、3.3V?輸入。

VDD 不影響時鐘的性能指標(Performance Characteristics)

參見:Table 5. Performance Characteristics

(VDD = 1.8 V –5% to +10%, 2.5 V ±10%, or 3.3 V ±10%, TA = –40 to 85 °C)

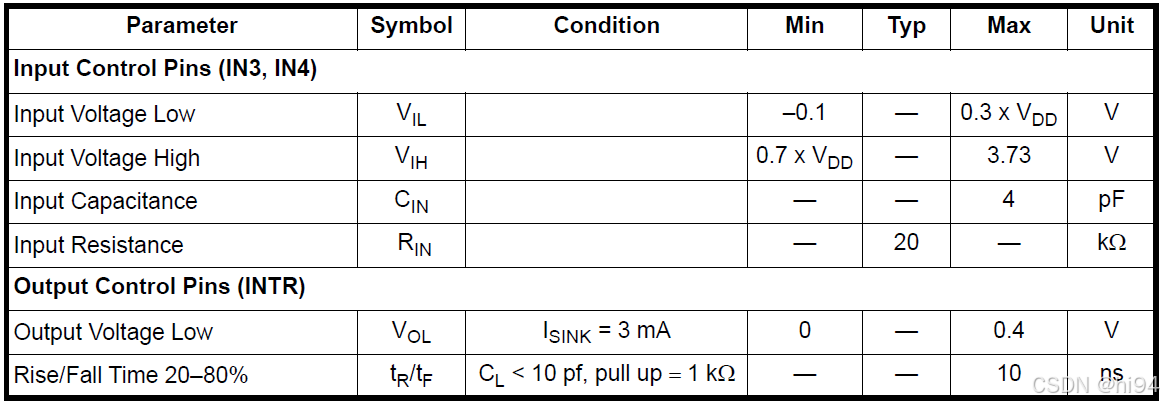

2)VDD 影響 Control Pins

3)VDD 影響 IIC Pins

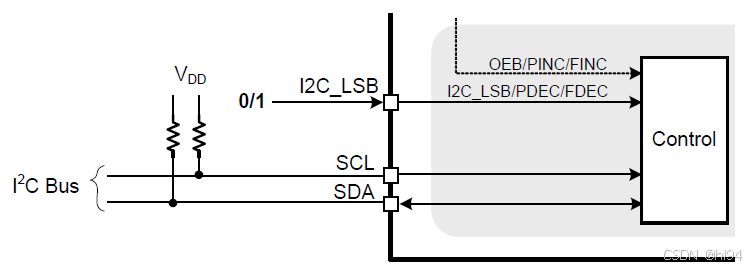

- IIC 總線可在 1.71V 至 3.63V 的電壓范圍內工作。

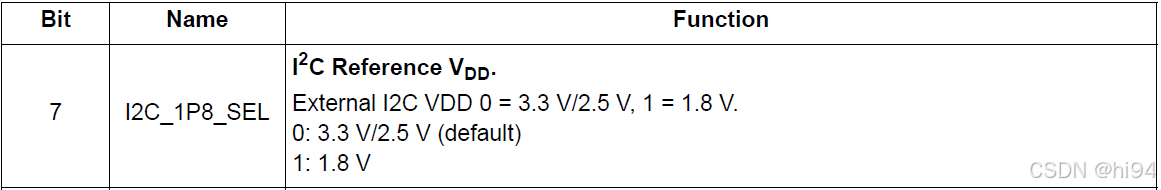

- 當 IIC 總線電壓低于 2.5V 時,必須將寄存器 27[7] 置為 1 以確保符合 IIC 總線標準。

?

?

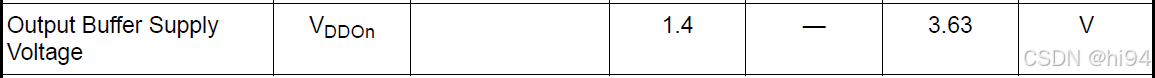

2.4.2?VDDOn

VDDOn:Output Clock Supply Voltage,支持 1.5V、1.8V、2.5V、3.3V?輸入。

3. Si5338

3.1 Input Stage

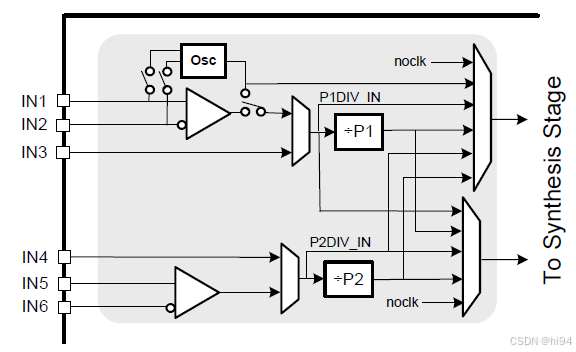

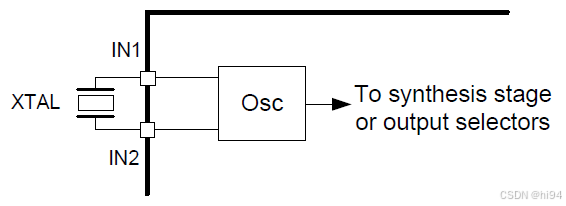

3.1.1 Diagram

3.1.2 時鐘輸入

時鐘輸入可以連接差分、單端信號

3.1.3 自由晶振

可以連接晶振

3.1.4 單端至差分

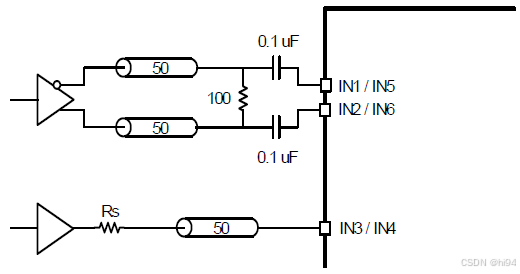

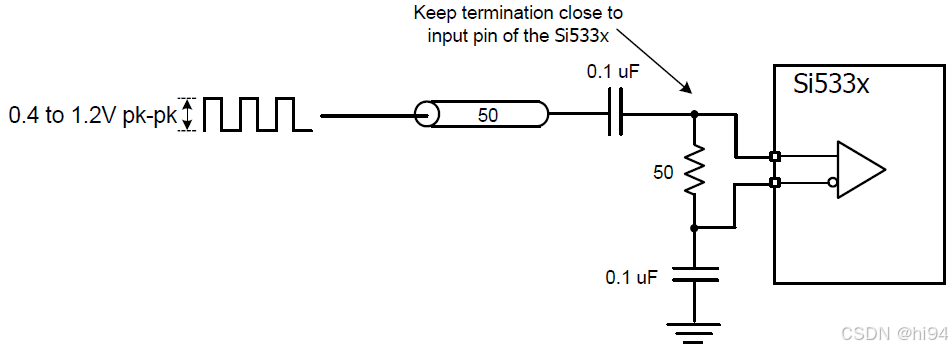

可以將任何單端信號連接到差分輸入引腳(IN1/IN2 或 IN5/IN6)。

對于需要 50 Ω 負載的信號,推薦的接口如圖所示。

示例中,輸入電平小于 1.2 VPP SE(峰峰值單端)且大于 0.4 VPP SE。此時,建議的最大輸入頻率為 350 MHz。

3.2?Output Stage

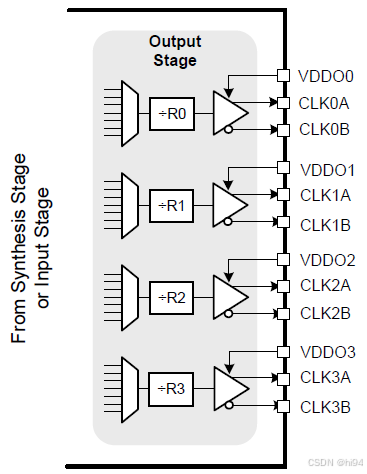

3.2.1 Diagram

如下圖陰影部分所示:

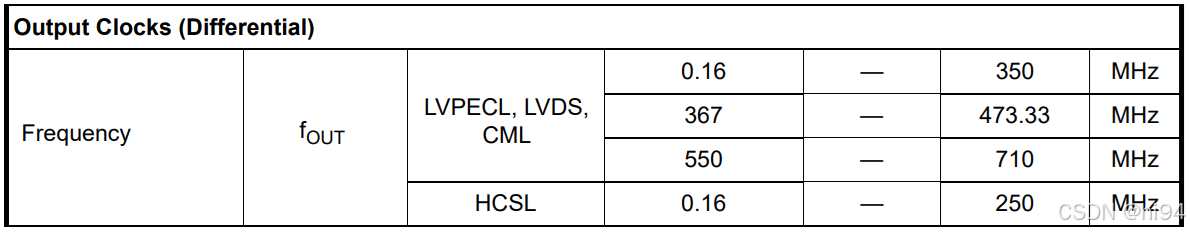

每個通道可獨立配置輸出格式:

- LVPECL/LVDS:0.16 至 710 MHz

- HCSL:0.16 至 250 MHz

- CMOS:0.16 至 200 MHz

- SSTL/HSTL:0.16 至 350 MHz

每個通道可獨立配置電壓:

- 1.5, 1.8, 2.5, 3.3 V

3.2.2?Output CLK Info

- VDD = 1.8 V –5% to +10%

- VDD = 2.5 V ±10%

- VDD = 3.3 V ±10%

- TA = –40 to 85 °C

?

?

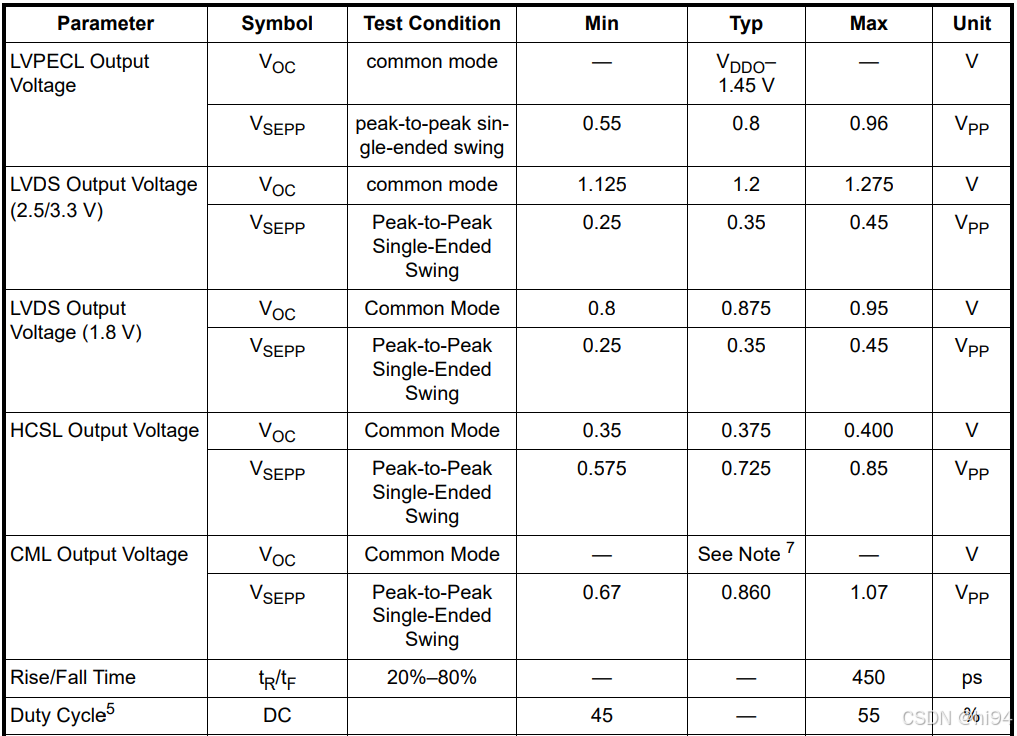

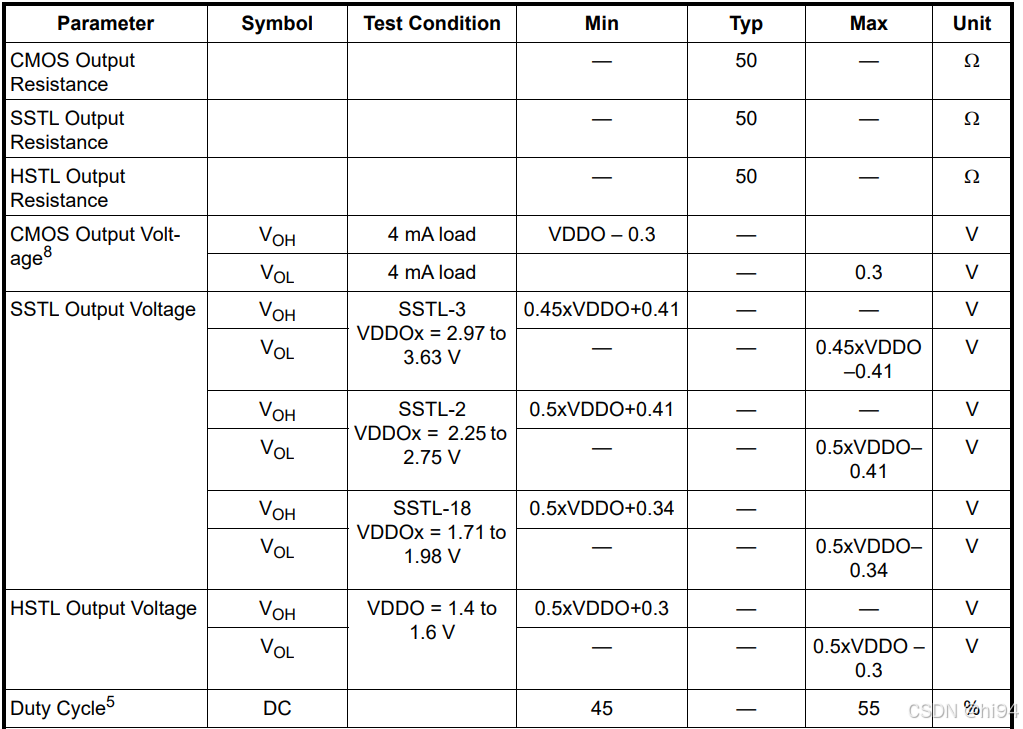

3.2.3?Output Volt Info

- VDD = 1.8 V –5% to +10%

- VDD = 2.5 V ±10%

- VDD = 3.3 V ±10%

- TA = –40 to 85 °C

?

3.3 LVDS

3.4?ECL

3.4.1 ECL 系列

ECL(Emitter-Coupled Logic,發射極耦合邏輯),是一種高速數字邏輯。它的核心特點在于使用晶體管(通常是雙極性結型晶體管 BJT)以一種特殊的方式連接,使得晶體管在開關過程中不會進入飽和區,避免了從飽和狀態中退出的時間延遲,因此開關速度非常快。

常見的變種有:NECL, PECL, LVPECL

命名規則如下:

[Low voltage] [Negative/Positive(Pseudo)] Emitter-coupled logic

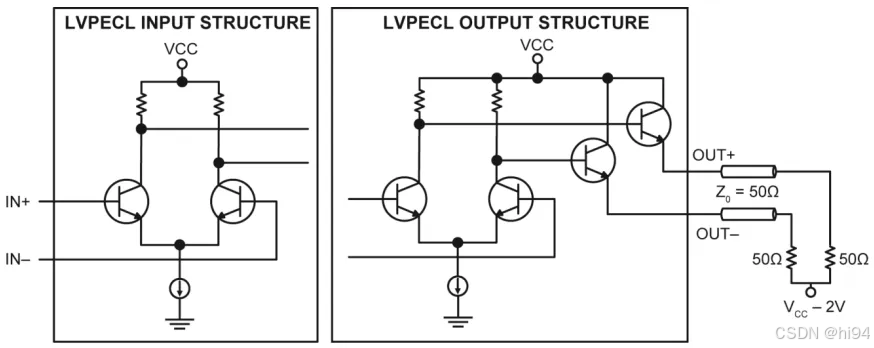

3.4.2 輸入輸出級

輸入輸出級示意圖:

3.4.3 DC 耦合

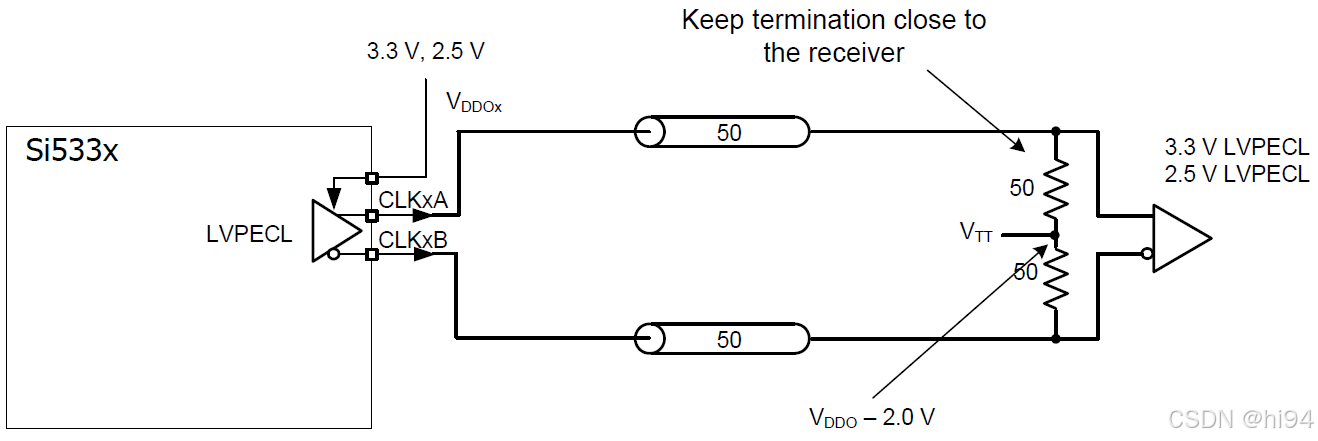

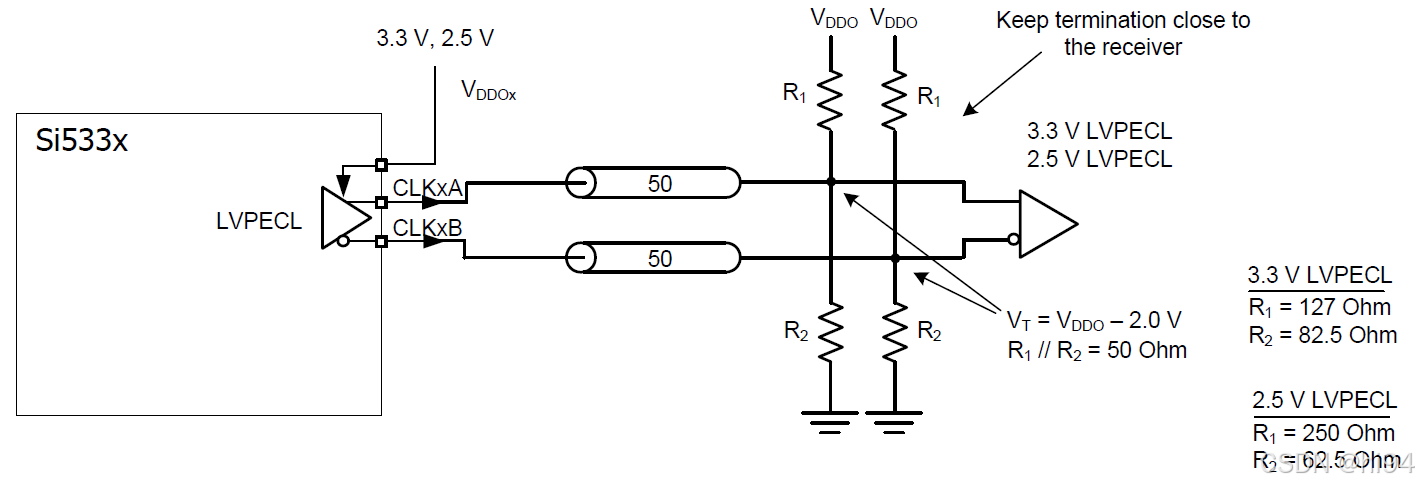

1)DC Coupled Termination of 50 Ohms to VDD – 2.0 V

- 標準的 LVPECL 驅動器支持兩種常用的直流耦合配置。

- LVPECL 驅動器最初設計為端接 50 Ω 到 VDD–2 V。

- VTT 可以通過如圖所示的簡單分壓電路提供。

2)DC Coupled with Thevenin Termination

- 戴維南等效電路提供了一個端接至 VDD–2.0 V 的 50 Ω 負載。

- 對于 3.3 V LVPECL,使用 R1 = 127 Ω 和 R2 = 82.5 Ω。

- 對于 2.5 V LVPECL,使用 R1 = 250 Ω 和 R2 = 62.5 Ω。

- 缺點:戴維南等效電路會從 VDDO 電源消耗額外的功率。

3.4.4 AC 耦合

當接收器和驅動器具有兼容的電壓擺幅但共模電壓不同時,必須使用交流耦合。

交流耦合對于直流平衡信號(例如 50% 占空比的時鐘信號)非常有效。

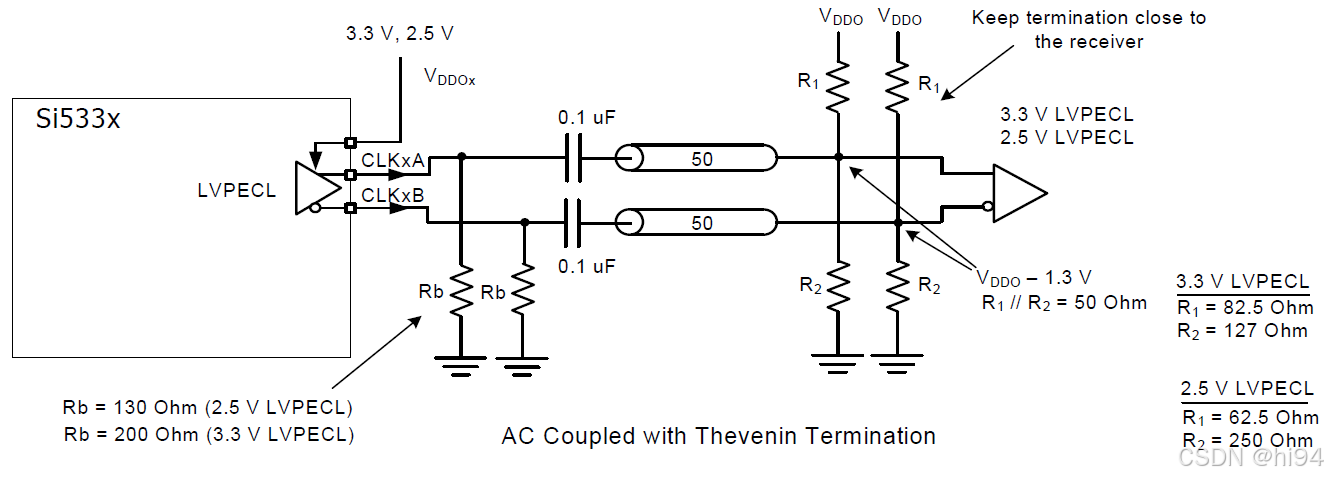

1)AC Coupled with Thevenin Termination

- 戴維南等效終端是一種方便且常用的方法。

- 尤其是在沒有 VBB (即 VDD – 1.3 V) 電源的情況下。

- 它會消耗額外的功率。

(PS:VBB 的全稱是 Bipolar Base Voltage)

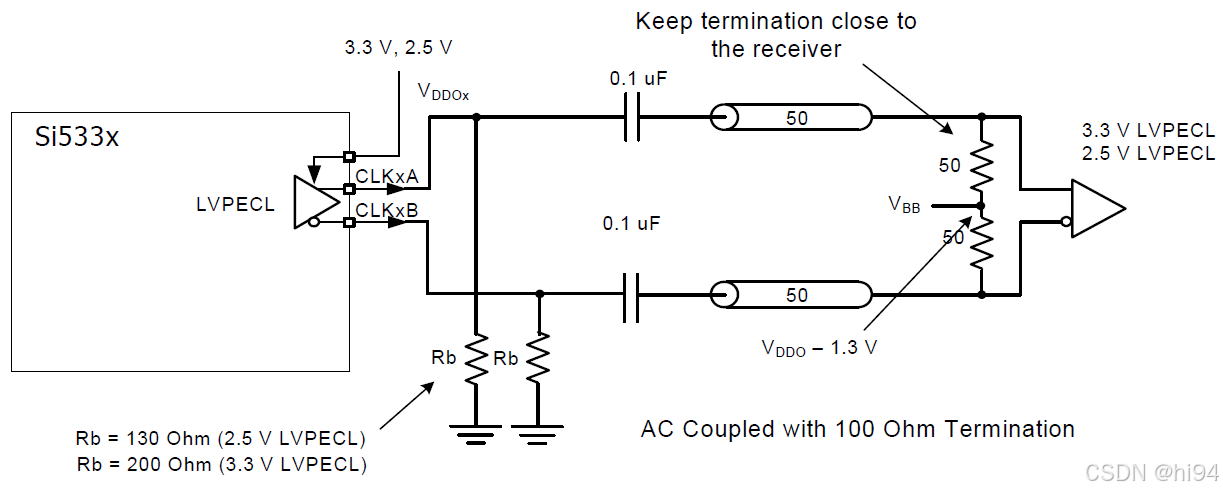

2)AC Coupled with 100 Ohm Termination

- 消耗的功率較少

3.5 CML

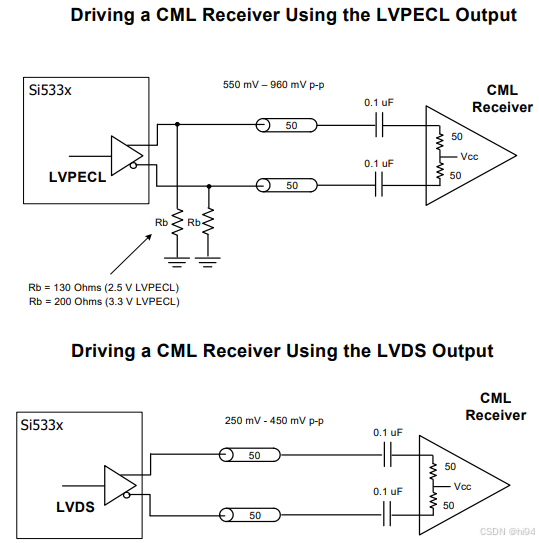

Current Mode Logic,電流模式邏輯。

采用差分傳輸,并在接收端端接至 Vcc,阻值為 50 Ω。

CML 接收器可以由 LVPECL 或 LVDS 輸出驅動,具體取決于接收器所需的信號擺幅。

當使用 LVPECL 輸出驅動 CML 接收器時,可以實現 550 mV 至 960 mV 的單端輸出擺幅。

為了獲得更小的輸出擺幅,建議使用 LVDS 模式,其單端擺幅在 250 mV 至 450 mV 之間。

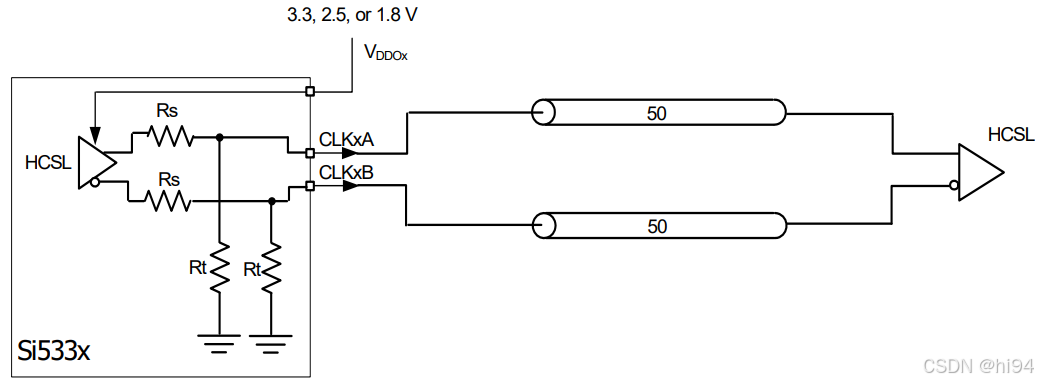

3.6?HCSL

Host Clock Signal Level,主機時鐘信號電平。

輸出常用于 PCI Express 應用中。

典型的 HCSL 驅動器具有一個開路源極輸出,需要一個外部串聯電阻和一個對地電阻。

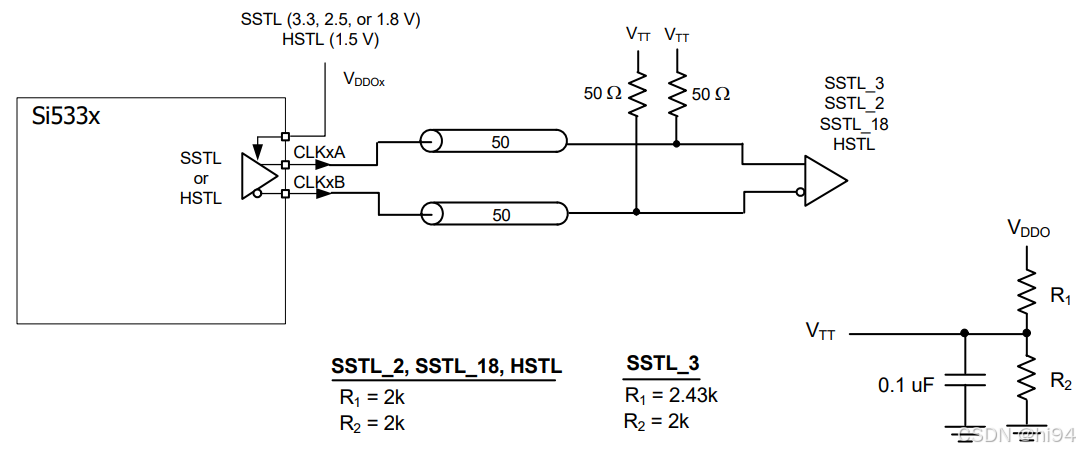

3.7 SSTL

Stub Series Termination Logic,短線串聯終端邏輯。

常用于基于 DRAM 的 DDR 內存芯片和內存模組。

SSTL?可以是單端,也可以是差分。

3.8 HSTL

同 3.6。

4. 總結

本文介紹了 Si5338 EVB 的功能和配置,以及 Si5338 芯片的特性。文檔深入解析了 EVB 的可編程電壓功能,包括 GUI 配置和基于 AD5263 數字電位計及 MAX8869 穩壓器的原理。供電部分闡述了 VDD 和 VDDOn 對芯片和接口的影響。

針對 Si5338 芯片,文檔介紹了其輸入和輸出級,包括多種時鐘輸入方式(差分、單端、晶振)和單端轉差分電路。輸出級支持 LVPECL、LVDS、HCSL、CMOS 和 SSTL/HSTL 等多種格式,并可獨立配置電壓。文檔還詳細解釋了LVDS、ECL(包括 LVPECL 及其直流、交流耦合)、CML、HCSL 和 SSTL/HSTL 等不同輸出接口的特性和應用。

)

走線要求)

)

)

)

)