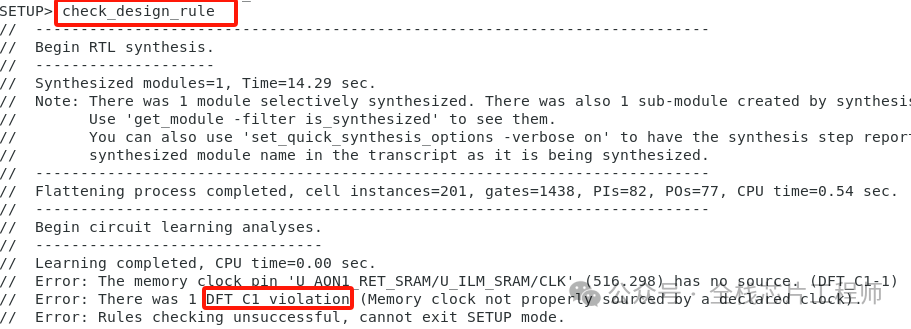

景芯訓練營VIP學員在實踐課上遇到個DFT C1 violation,導致check_design_rule無法通過,具體報錯如下:

遇到這個問題第一反映一定是確認時鐘,于是小編讓學員去排查add_clock是否指定了時鐘,指定的時鐘位置是否正確。

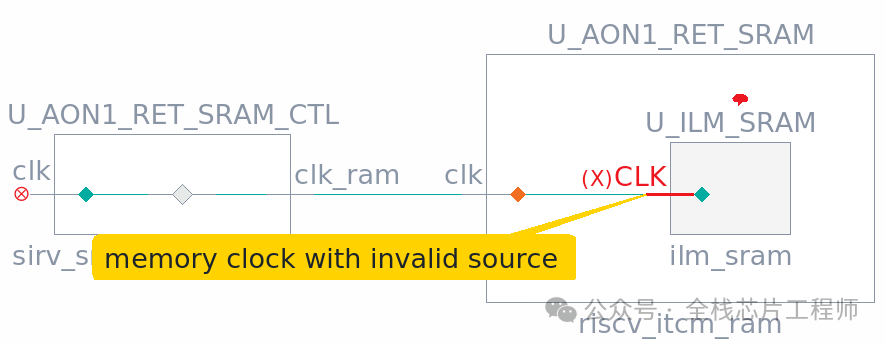

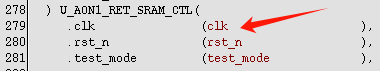

景芯VIP學員說看了幾遍還是正確指定了時鐘,沒有頭緒。然后小編打開RTL代碼一看,發現該同學犯了很低級的問題,大家猜猜是什么問題先,知識星球公布答案。

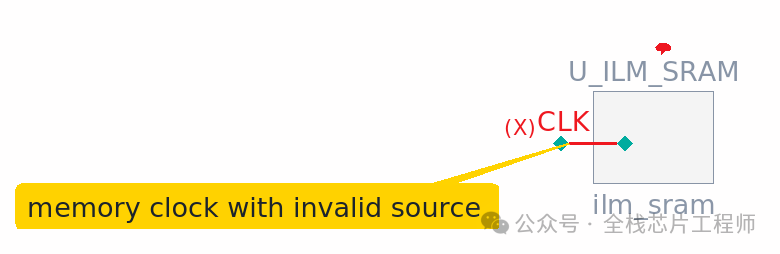

答:原因是該同學直接修改了RTL的clk連接,造成clk連接錯誤,tessent 工具無法trace到正確的時鐘。因此。大家記住,修改代碼一定要慎之又慎,不能隨意改,而且改了代碼一定要做lint、spyglass,保證語法OK,仿真OK。

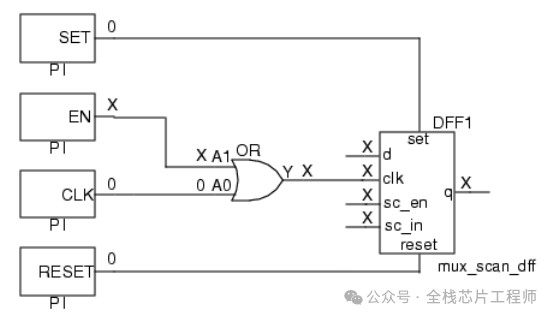

我們知道,在下圖EN端輸出X時,DFF的clk端將是X,于是就會產生C1的 violation,那么如果或門換成與門呢?

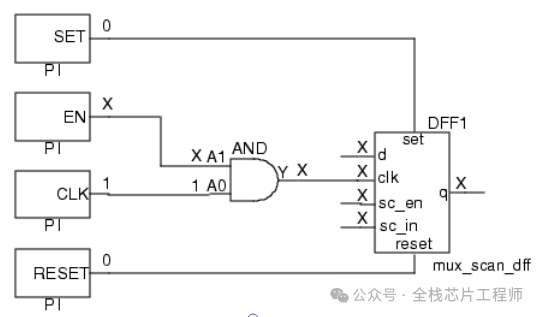

如果或門換成與門呢?如果EN是X,那么與門依然輸出X到DFF的clk,造成DFF無法上鏈,也會造成覆蓋率下降。

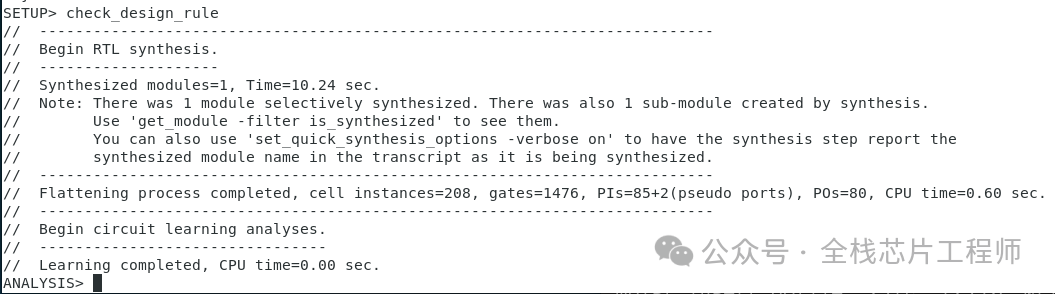

只要改了這個問題就輕松過了DRC:

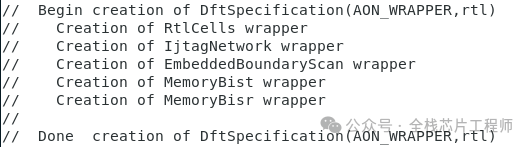

然后進行AON_WRAPPER這個harden的create_dft_specification:

)

)

)

)