一、input delay約束

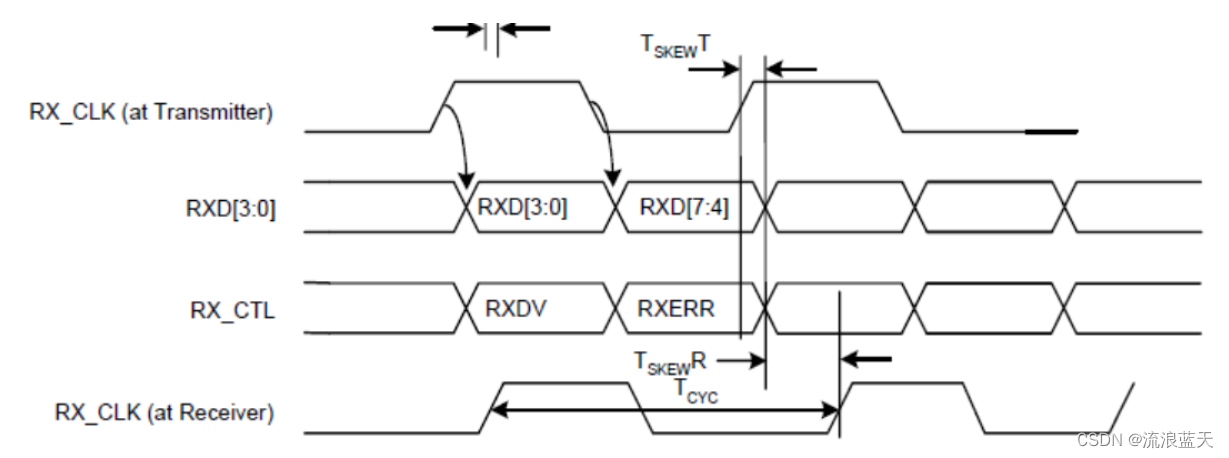

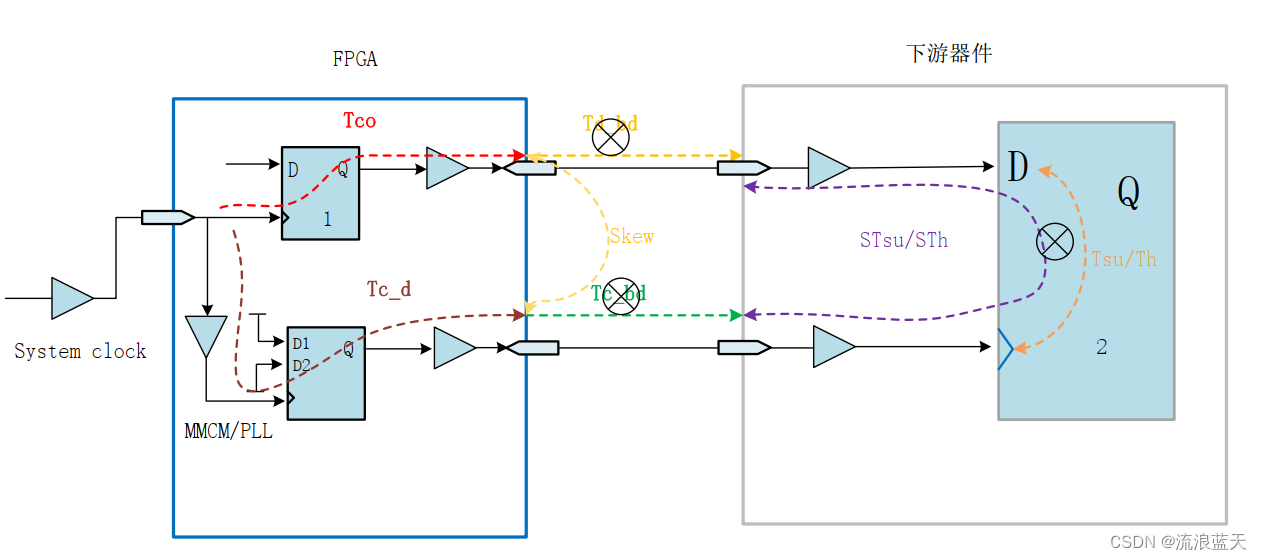

在千兆以太網數據收發項目中,RGMII的數據輸入方式為DDR,源同步輸入方式,可以用之前提到的分析模型進行約束。?

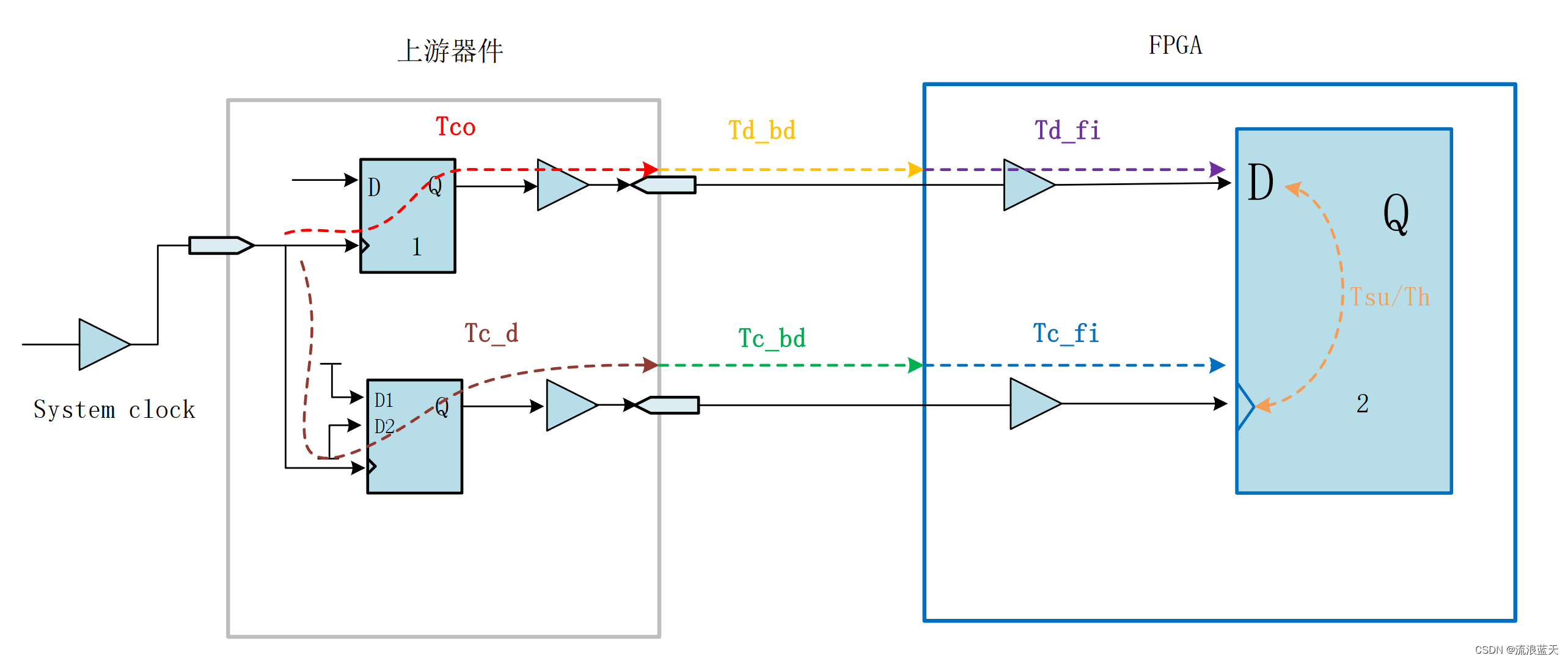

在時序約束原理中我們提到,input delay約束的就是發射沿lunch到數據有效的延時,根據時序圖得到:

?????????LrMax = Tco max + Td_bd max -(Tc_d + Tc_bd) ------分析建立時間時序

?????????LrMin?? = Tco min?+ Td_bd min?-(Tc_d + Tc_bd)? ------分析保持時間時序

一般在input delay分析中,我們默認Td_bd ==Tc_bd,并不考慮Tc_d。因此LrMax和LrMin就指的是上游器件輸出數據和輸出時鐘的延時。

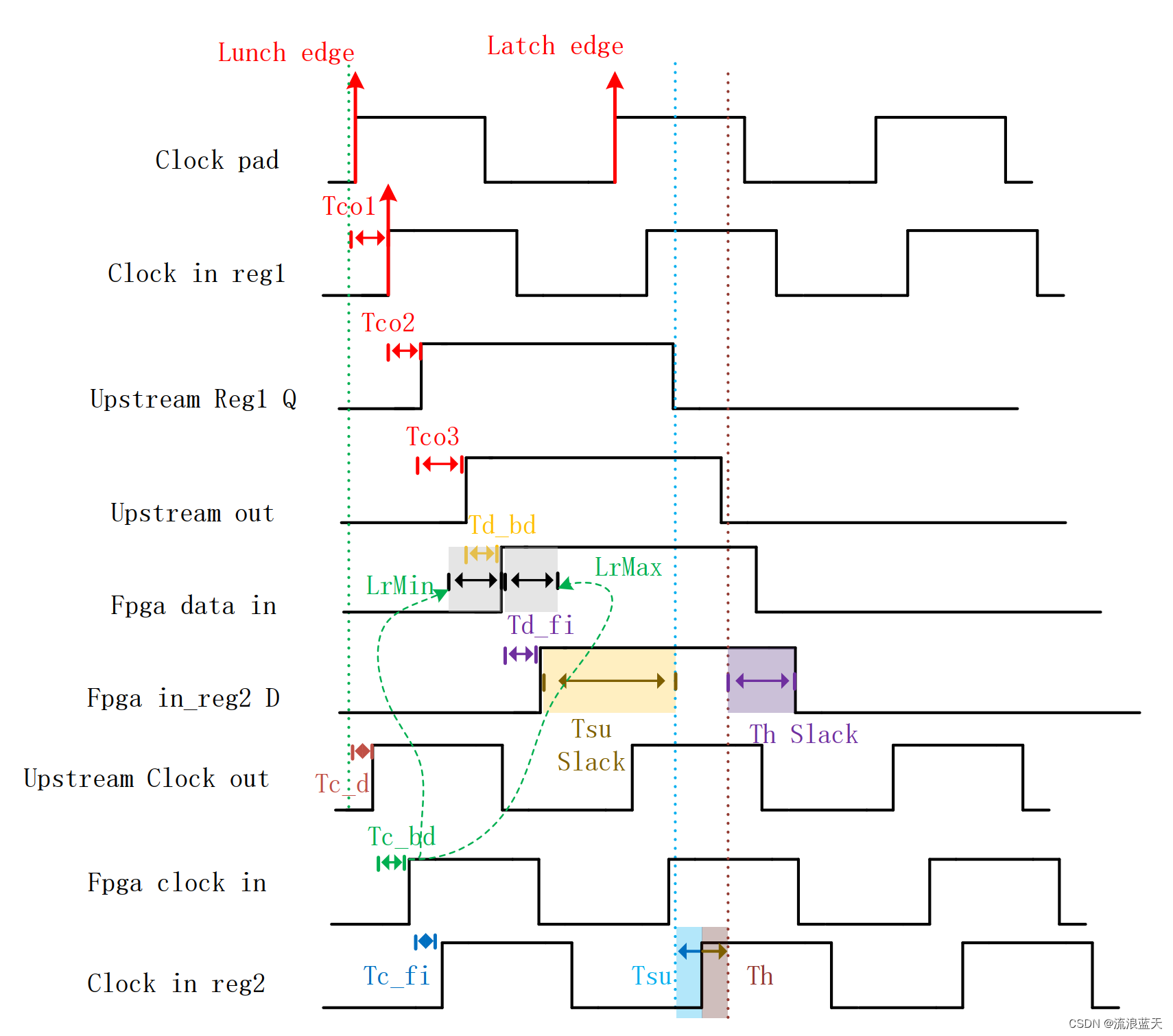

PHY芯片datasheet中時序圖如下,圖中的TskewR==2ns是時鐘信號相對于數據信號的延時。數據線之間的SKEW未知,我們假設為0.2ns。

可以得到:

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?LrMax = 2 + skew/2 = 2.1

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?LrMin = 2 - skew/2 = 1.9

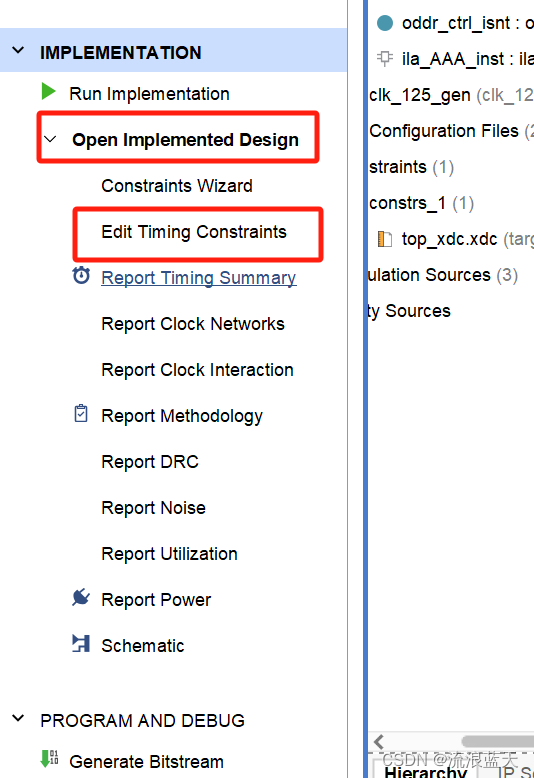

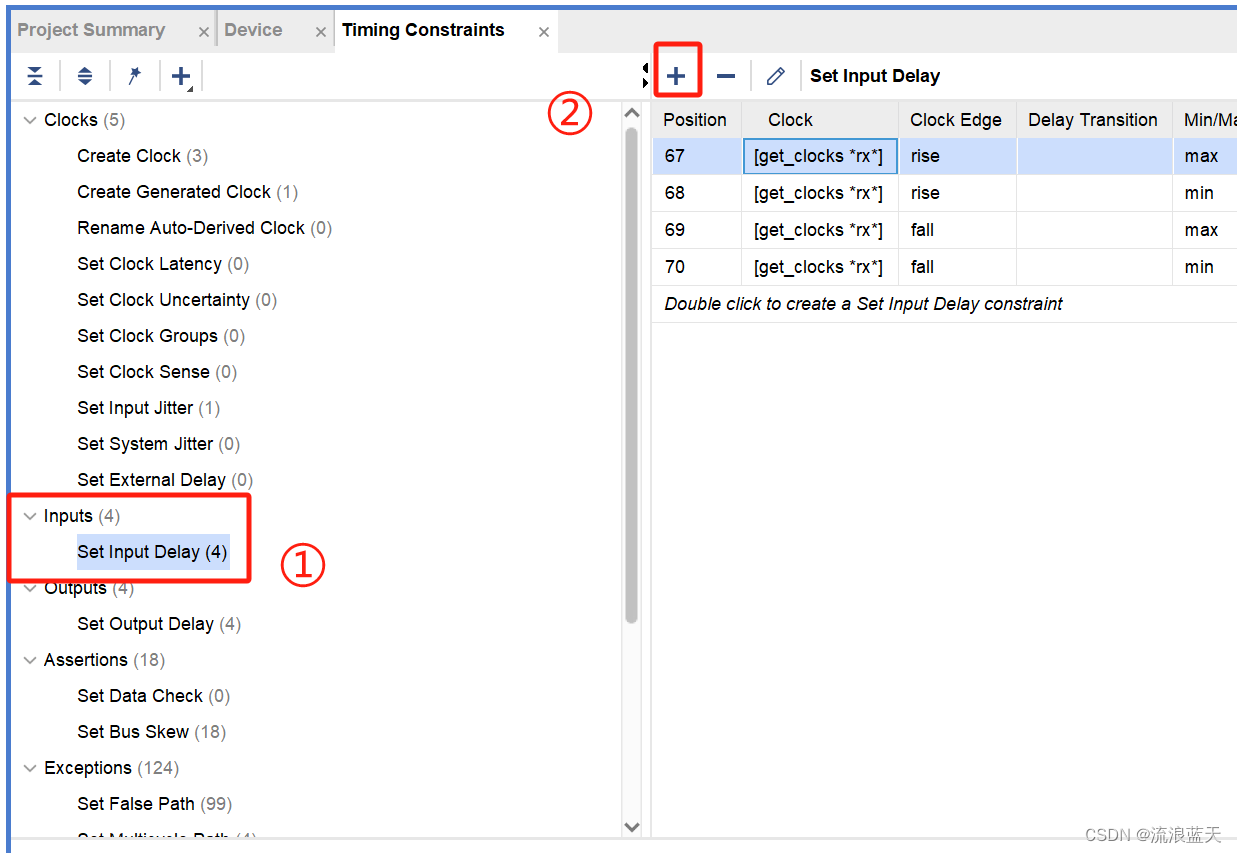

接下來就可以在工具中進行約束。首先,打開Open Implementation----->Edit Timing constraints。

然后選擇Set Input delay,點擊加號“+”添加約束信息。

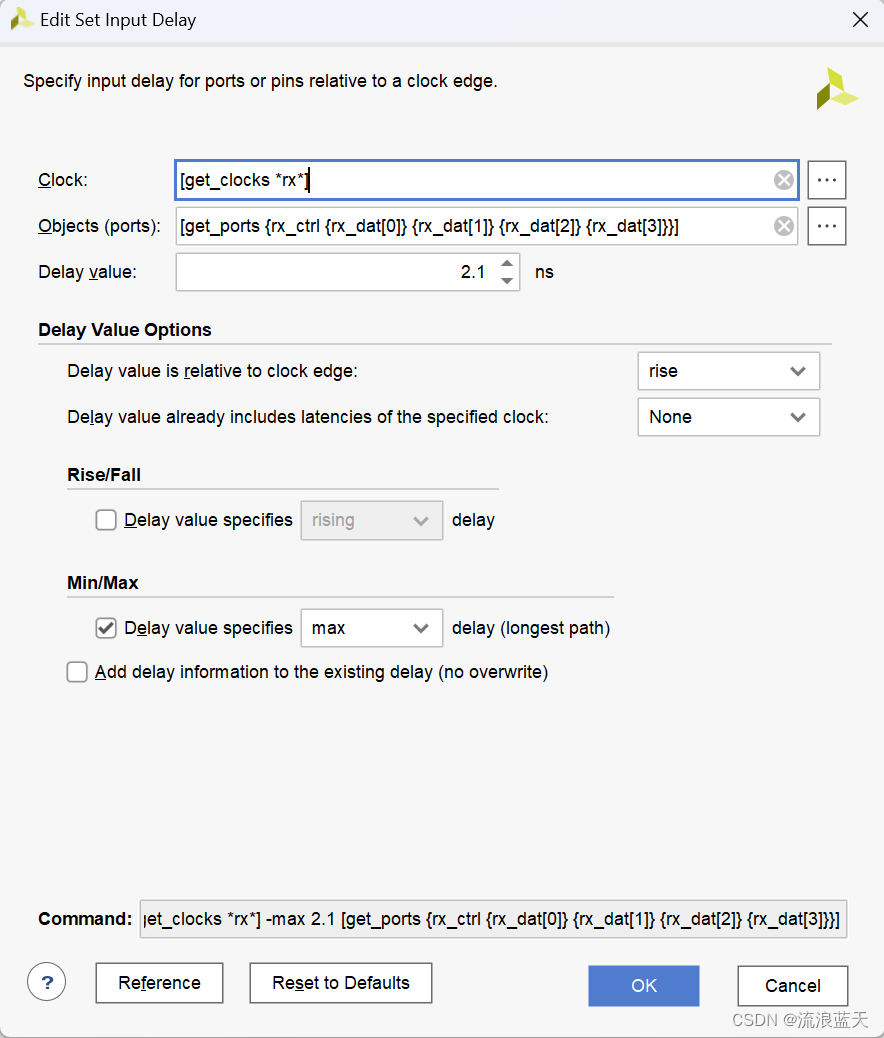

設置參數。

? ? ? ? Clock:時鐘,選擇rx_clk。

? ? ? ? Objects:約束目標,選擇RGMII輸入信號。

? ? ? ? Delay value:延時時間。

? ? ? ? Delay value is relative to clock edge:邊沿選擇。

? ? ? ? Delay value specifies:最大最小選擇。

Delay value is relative to clock edge選擇rise,Delay value specifies選擇max,在Delay value處設置上升沿的最大、最小延時;Delay value is relative to clock edge選擇full,Delay value specifies選擇max,在Delay value處設置上升沿的最大延時;Delay value is relative to clock edge選擇rise,Delay value specifies選擇min,在Delay value處設置上升沿的最小延時。下降沿的延時最大、最小延時設置同理。

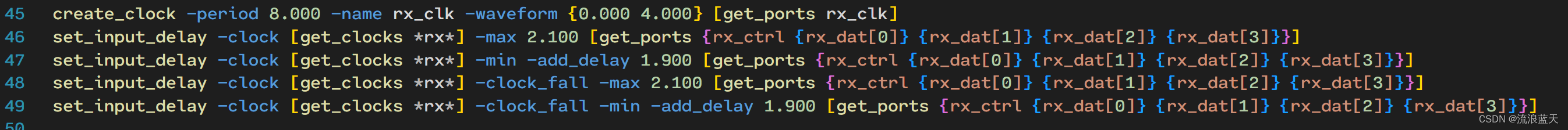

這樣就完成了input delay的約束,點擊保存,可以看到input delay約束信息已經更新到了.xdc文件中。

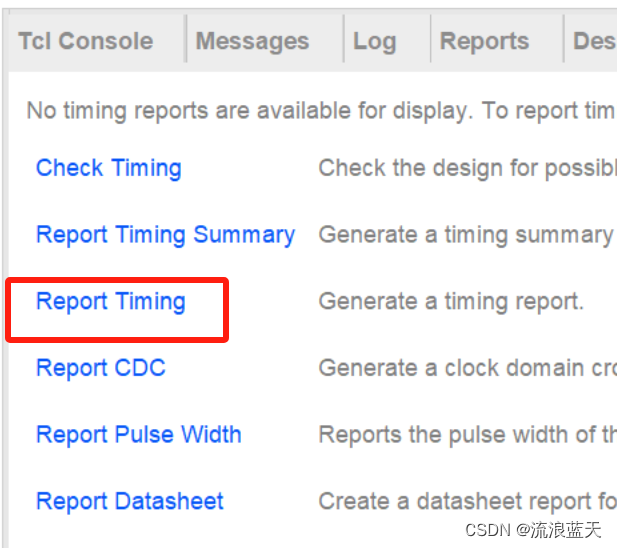

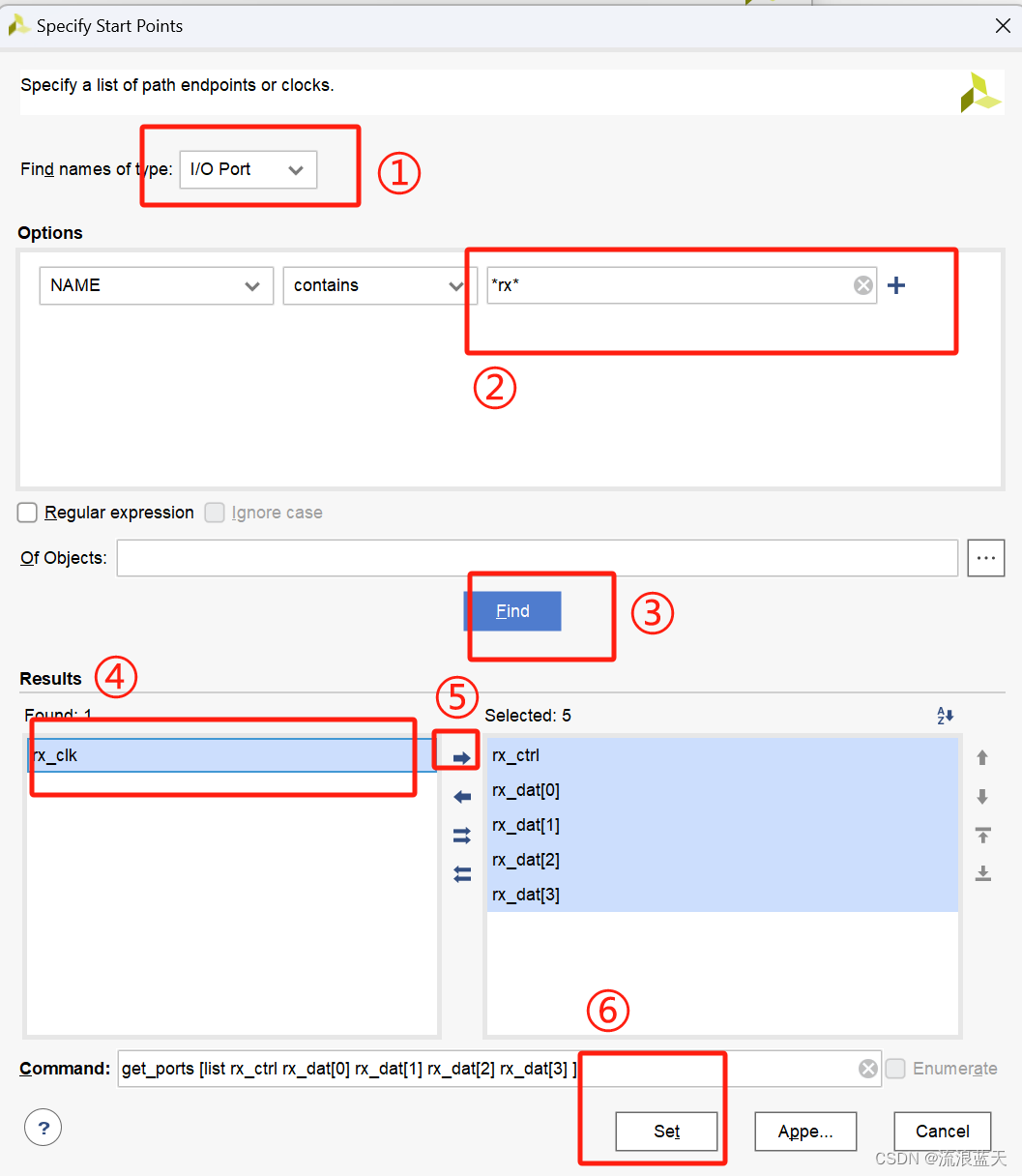

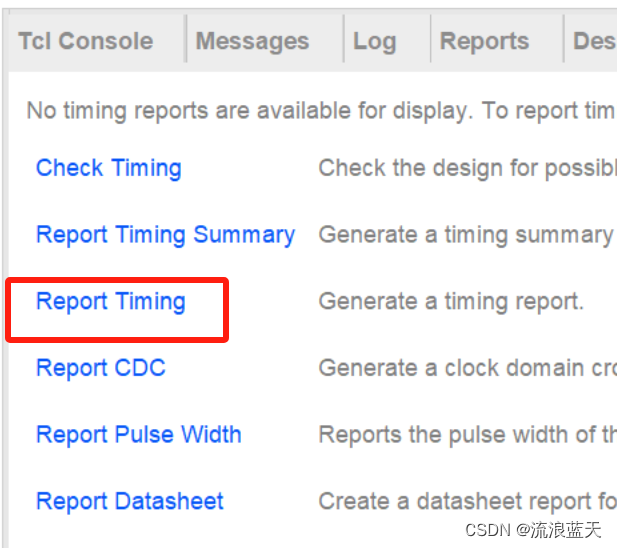

?重新綜合、布局布線,點擊Report Timing。

?設置要打印的時序報告的參數。設置要打印的信號。

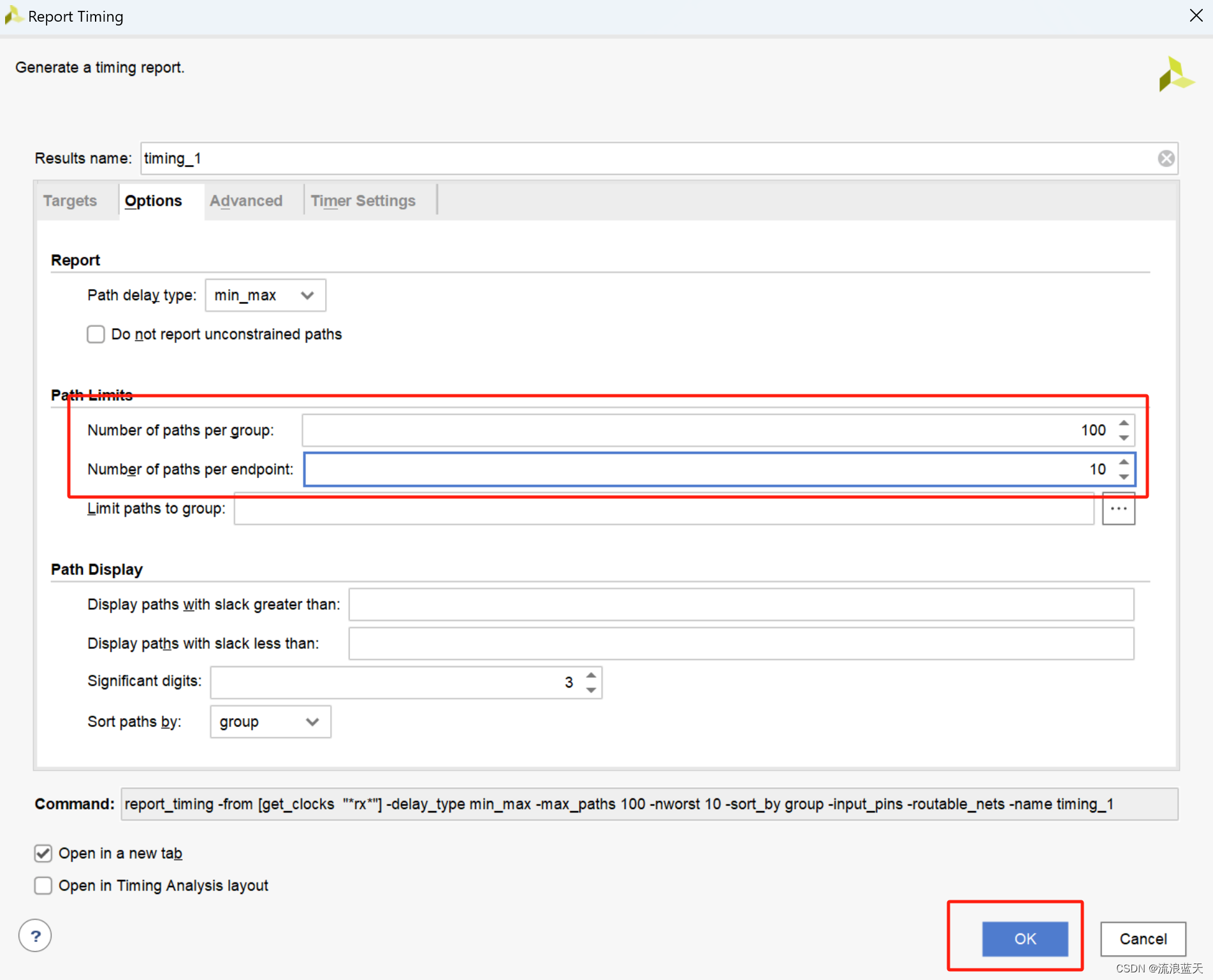

?在option 中的設置觀察時序路徑條數和每個路徑打印多少條信息, 點擊 OK 。

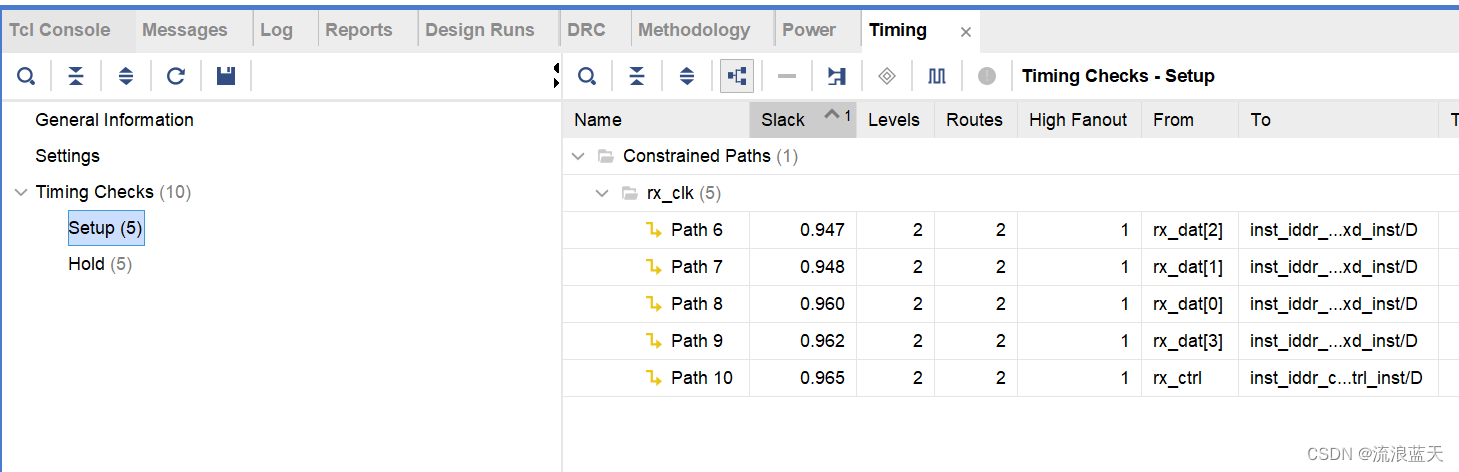

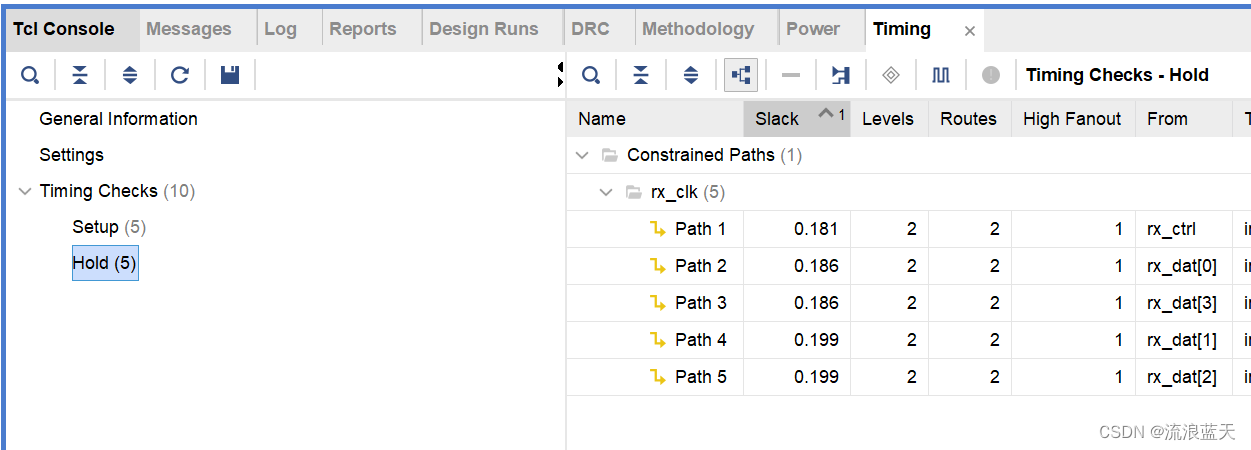

?這樣就生成了時序報告。可以看到建立時間和保持時間沒有發生時序違例。

二、indelay control方式input delay約束?

?????????以上的input delay約束方式是通過PLL調整時鐘相位以達到時序要求,indelay control方式是通過對數據進行延時以滿足時序要求。

? ? ? ? 通過IDELAY2源語實現這個功能,例化該源語在ODDR模塊中,模塊輸入數據信號tx_dat[7:0]和使能信號tx_en首先進入該源語進行數據延時,源語輸出再進行ODDR轉換。

DELAYE2 #(

.CINVCTRL_SEL("FALSE"), // Enable dynamic clock inversion (FALSE, TRUE)

.DELAY_SRC("IDATAIN"), // Delay input (IDATAIN, DATAIN)

.HIGH_PERFORMANCE_MODE("FALSE"), // Reduced jitter ("TRUE"), Reduced power ("FALSE")

.IDELAY_TYPE("FIXED"), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE

.IDELAY_VALUE(0), // Input delay tap setting (0-31)

.PIPE_SEL("FALSE"), // Select pipelined mode, FALSE, TRUE.REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz (190.0-210.0, 290.0-

.0)..SIGNAL_PATTERN("DATA") // DATA, CLOCK input signal)IDELAYE2_inst_dv (.CNTVALUEOUT(), // 5-bit output: Counter value output.DATAOUT(rx_ctrl_t), // 1-bit output: Delayed data output.C(1'b0), // 1-bit input: Clock input.CE(1'b0), // 1-bit input: Active high enable increment/decrement input.CINVCTRL(1'b0), // 1-bit input: Dynamic clock inversion input.CNTVALUEIN(5'd0), // 5-bit input: Counter value input.DATAIN(1'b0), // 1-bit input: Internal delay data input.IDATAIN(rx_ctrl), // 1-bit input: Data input from the I/O.INC(1'b0), // 1-bit input: Increment / Decrement tap delay input.LD(1'b0), // 1-bit input: Load IDELAY_VALUE input.LDPIPEEN(1'b0), // 1-bit input: Enable PIPELINE register to load data input.REGRST(1'b0) // 1-bit input: Active-high reset tap-delay input);IDDR #(.DDR_CLK_EDGE("SAME_EDGE_PIPELINED"), // "OPPOSITE_EDGE", "SAME_EDGE"// or "SAME_EDGE_PIPELINED".INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1.INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC") IDDR_rxctrl_inst (.Q1(rxdv), // 1-bit output for positive edge of clock.Q2(rxerr), // 1-bit output for negative edge of clock.C(rx_clk_90), // 1-bit clock input.CE(1'b1), // 1-bit clock enable input.D(rx_ctrl_t), // 1-bit DDR data input.R(1'b0), // 1-bit reset.S(1'b0) // 1-bit set);其中IDELAY_VALUE表示設置延時大小,可以填寫的值為0~31,具體分辨率是多少每個器件并不相同,需要查看手冊。

此外,這個源語還要配合IDELAYCTRL使用:

IDELAYCTRL IDELAYCTRL_inst (.RDY(RDY), // 1-bit output: Ready output.REFCLK(sysclk), // 1-bit input: Reference clock input.RST(~locked) // 1-bit input: Active high reset input通過調整IDELAY_VALUE的值,就可以調整數據和時鐘之間的延時,消除時序違例。當IDELAY_VALUE增大時延時增大,建立時間裕量減小,保持時間裕量增大。

三、output delay約束?

同樣使用千兆以太網數據收發中的RGMII輸出端作為約束對象。在不知道目標端的建立時間和保持時間時,可以利用數據的skew進行output delay約束。

?根據時序圖可得:

????????????????????????????????????????????????dMax = Tcycle - askew

????????????????????????????????????????????????dMin = bskew

設置SKEW 的目的是讓綜合工具知道輸出的時鐘采樣沿不能落在 SKEW 的區域?。我們可以通過調整skew的值使時鐘沿落在數據的中心位置。這里設置askew=bskew=1.5ns,則dMax = 2.5,dMin = 1.5。

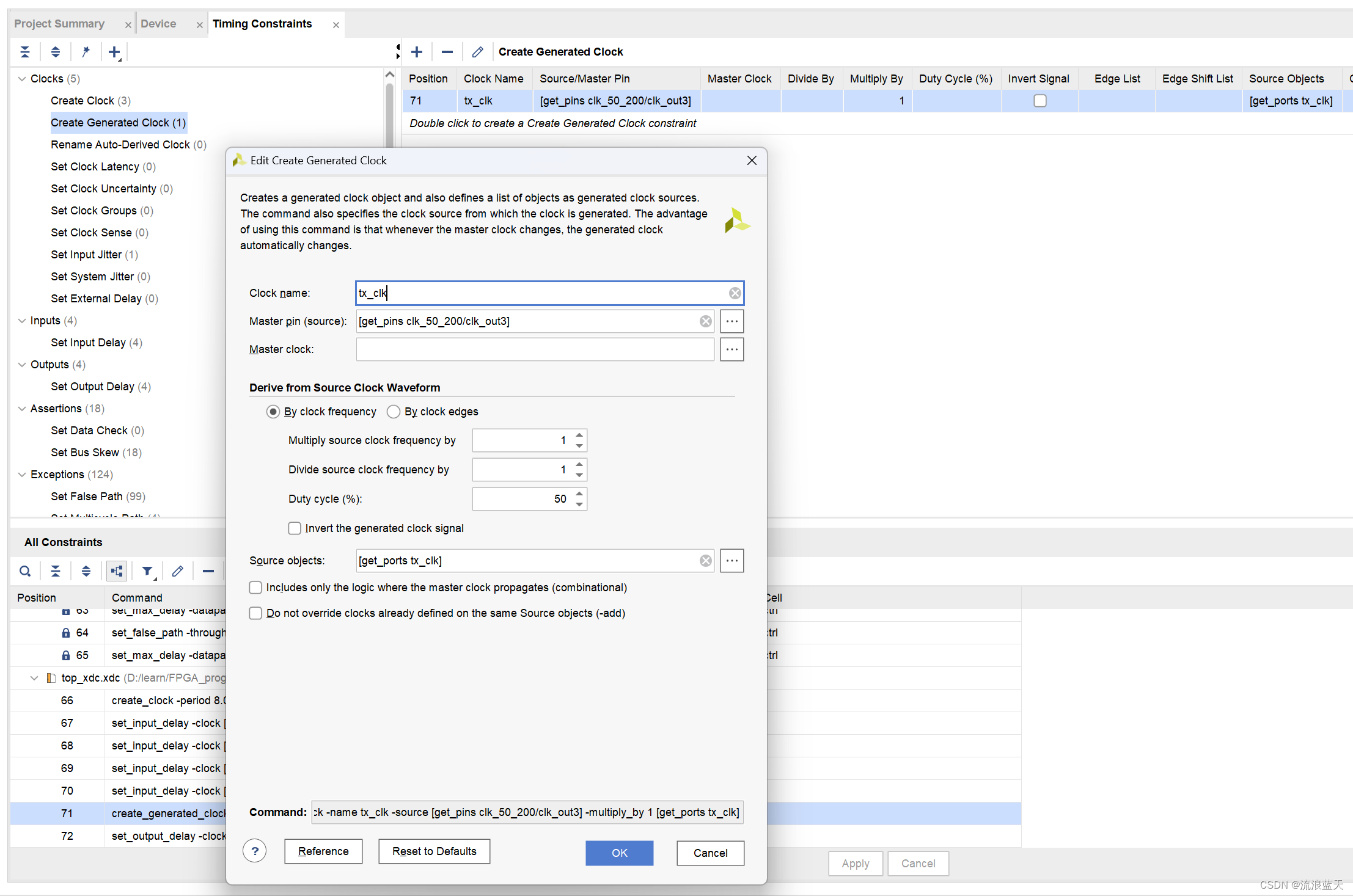

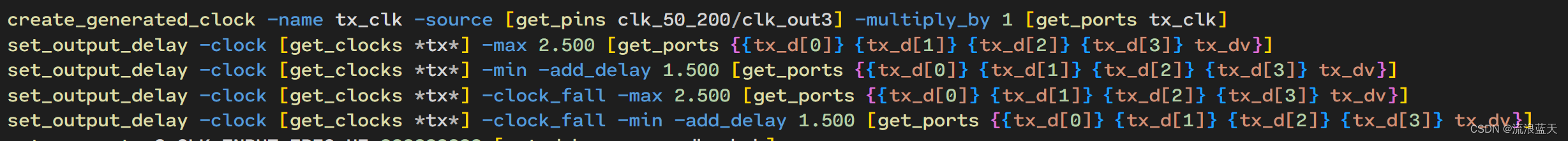

這樣就可以在工具中進行約束了。首先要創建生成時鐘,告訴綜合工具tx_clk是時鐘信號。打開Open Implementation----->Edit Timing constraints,選中Creat Generated Clock,點擊加號“+”,這里設置時鐘源為PLL輸出時鐘,目標時鐘為tx_clk。

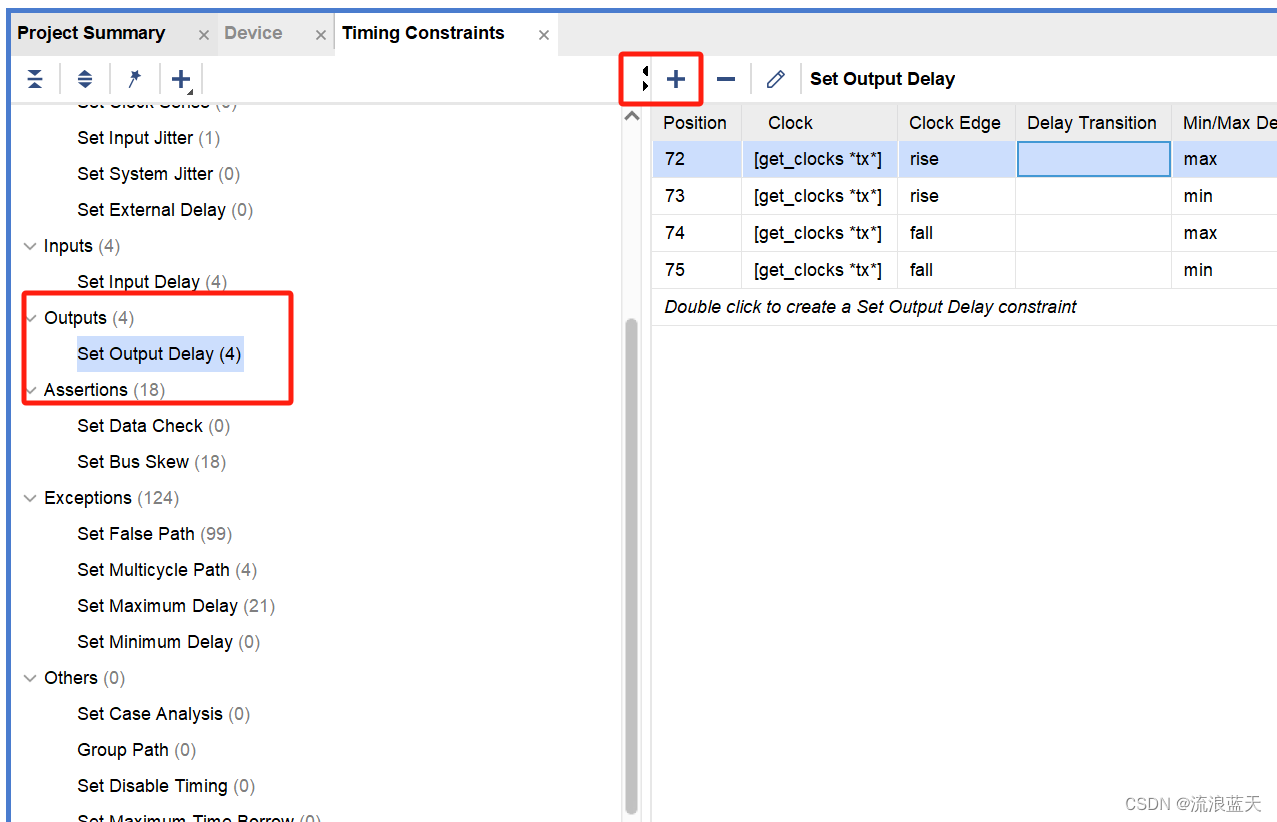

?然后選擇set Output Delay,點擊加號“+”添加約束信息。

設置參數。

? ? ? ? Clock:時鐘,選擇tx_clk。

? ? ? ? Objects:約束目標,選擇RGMII輸出信號。

? ? ? ? Delay value:延時時間。

? ? ? ? Delay value is relative to clock edge:邊沿選擇。

? ? ? ? Delay value specifies:最大最小選擇。

Delay value is relative to clock edge選擇rise,Delay value specifies選擇max,在Delay value處設置上升沿的最大、最小延時;Delay value is relative to clock edge選擇full,Delay value specifies選擇max,在Delay value處設置上升沿的最大延時;Delay value is relative to clock edge選擇rise,Delay value specifies選擇min,在Delay value處設置上升沿的最小延時。下降沿的延時最大、最小延時設置同理。

這樣就完成了output delay的約束,點擊保存,可以看到output delay約束信息已經更新到了.xdc文件中。

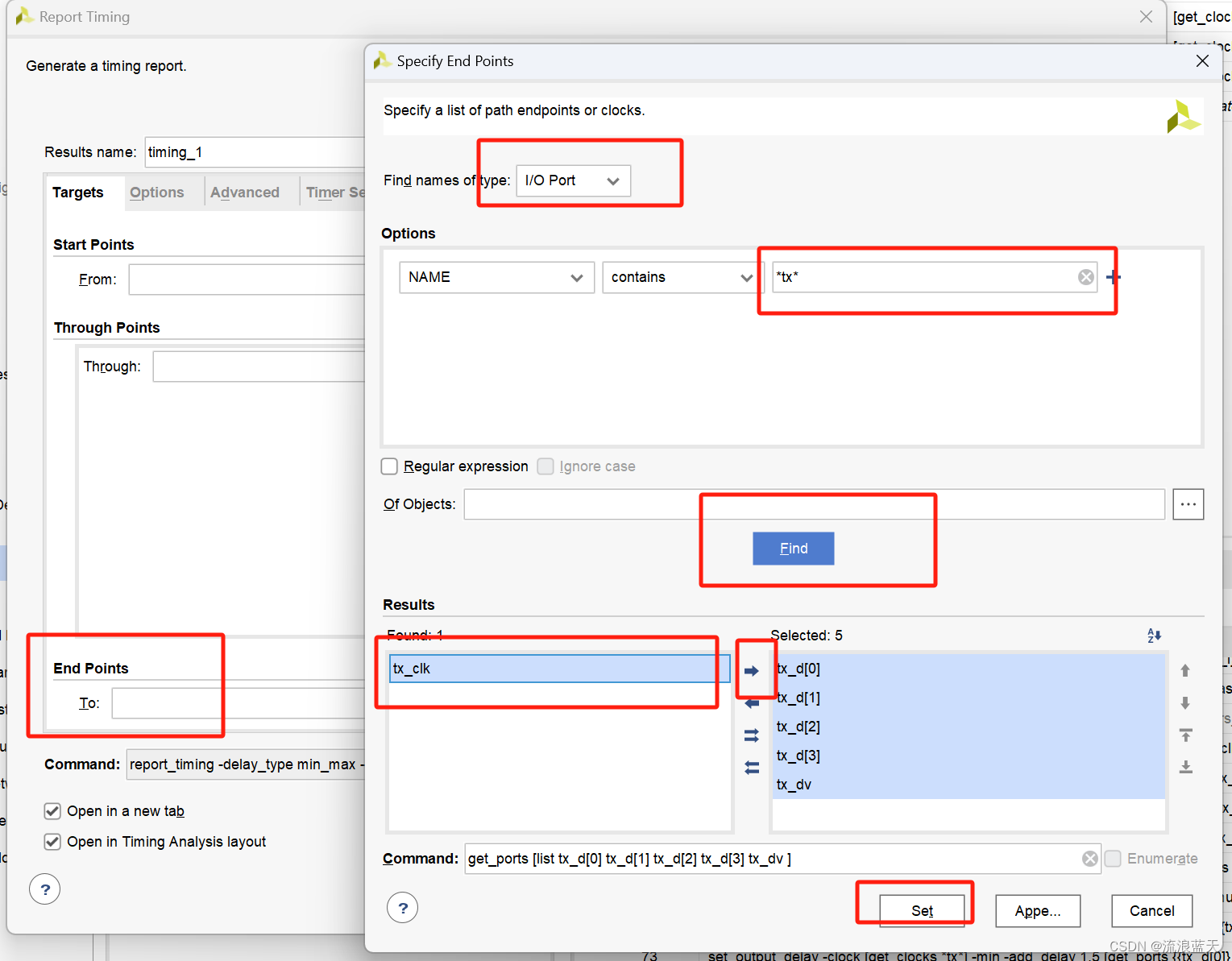

? 接下來我們重新綜合、布局布線,Open Implemented Design,點擊Report Timing。

設置時序報告打印參數。這里在End Points處添加。

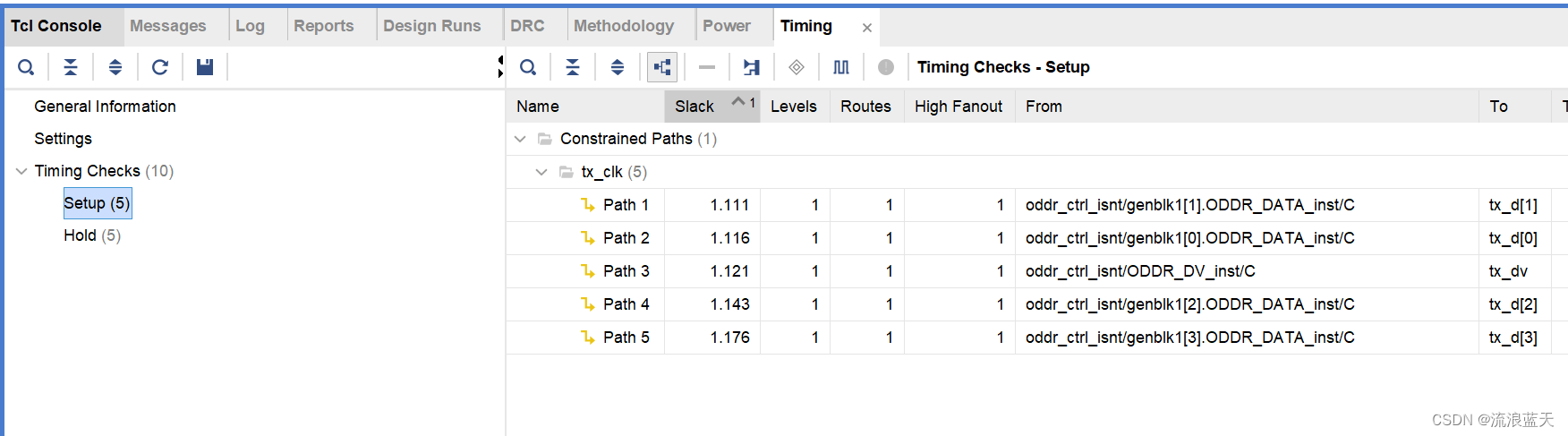

?這樣就生成了時序報告。可以看到建立時間和保持時間沒有發生時序違例。

?

JSON數據的回寫)