????????????????????????????????????????????????????????????????????????????蘇澤?

“棄工從研”的路上很孤獨,于是我記下了些許筆記相伴,希望能夠幫助到大家

目錄

微指令的形成方式

微指令的地址形成方式

對應考題

題目:微指令的地址形成方式 - 斷定方式

解題思路:

答題:

分析考點:

微程序控制單元設計

靜態微程序設計和動態微程序設計(小知識點 )

靜態

動態

指令流水線

在設計指令流水線時,需要考慮以下幾個方面:

易錯點

考題

示例問題

微指令的形成方式

微指令的地址形成方式

-

斷定方式

- 微指令格式中包含下地址字段。

- 后繼微指令的地址由該字段直接指定。

-

根據操作碼形成

- 機器指令加載到指令寄存器后,微指令地址由操作碼決定。

- 通過微地址形成部件來生成微指令地址。

-

增量計數器法

- 微指令地址寄存器(CMAR)的當前值加1。

- 公式表示為:(𝐶𝑀𝐴𝑅)+1→𝐶𝑀𝐴𝑅(CMAR)+1→CMAR。

-

分支轉移

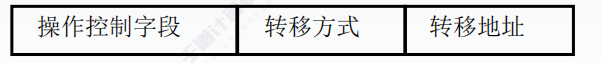

- 轉移方式:根據特定的判別條件進行轉移。

- 轉移地址:指明轉移成功后的微指令地址。

-

操作控制字段

- 包含轉移方式和轉移地址。

-

通過測試網絡

- 微指令地址的形成可能依賴于測試網絡的結果。

-

硬件產生微程序入口地址

- 第一條微指令地址由專門的硬件產生。

- 取指周期和中斷周期的微程序首地址由硬件記錄。

對應考題

題目:微指令的地址形成方式 - 斷定方式

題目描述: 某計算機采用微程序控制器,共有32條指令。公共的取指令微程序包含2條微指令,各指令對應的微程序平均由4條微指令組成。采用斷定法(下地址字段法)確定下條微指令地址。求:

- 微指令中下地址字段可以沒有的位數至少是多少位?

- 總共需要存儲多少條微指令?

- 標注出130個不同的位置至少需要多少個二進制位?

解題思路:

-

理解題目要求:

- 確定微指令的下地址字段位數。

- 計算總共需要存儲的微指令數量。

- 計算標注130個不同位置所需的二進制位數。

-

計算微指令數量:

- 取指令微程序固定為2條微指令。

- 每條指令對應的微程序平均有4條微指令,共有32條指令。

-

計算下地址字段位數:

- 使用斷定法,需要足夠位數的下地址字段來唯一標識每一條微指令。

-

計算二進制位數:

- 需要的位數能夠表示從1到130的所有微指令地址。

答題:

-

計算微指令數量:

- 取指令微程序:2條

- 每條指令對應的微程序:32條指令 × 4條微指令/指令 = 128條

- 總共:2 + 128 = 130條微指令

-

計算下地址字段位數:

- 由于需要唯一標識130條微指令,使用二進制表示需要的位數為??log?2(130)??log2?(130)?。

- 計算得?27=12827=128,28=25628=256,因此至少需要8位。

-

計算二進制位數:

- 130個不同位置至少需要的二進制位數為??log?2(130)??log2?(130)?。

- 由于?27=12827=128?不足以表示130,所以需要?28=25628=256,即8位。

分析考點:

- 考點1:?微程序控制器的工作原理和微指令的地址形成方式。

- 考點2:?斷定法的理解和應用。

- 考點3:?二進制數的位數計算,以及如何確定能夠表示特定數量的唯一值所需的位數。

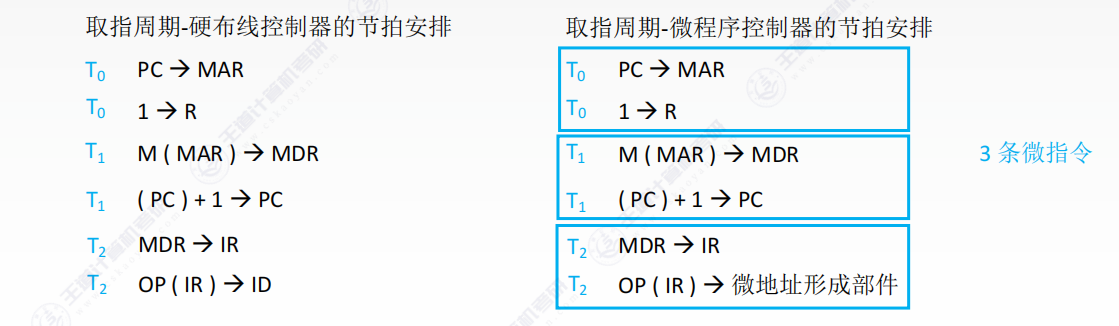

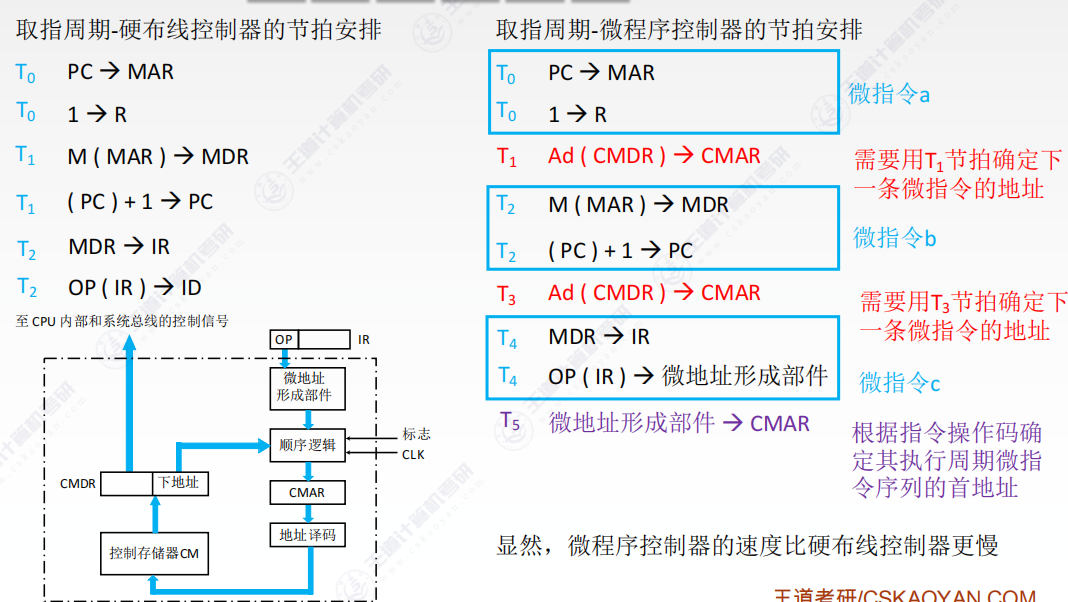

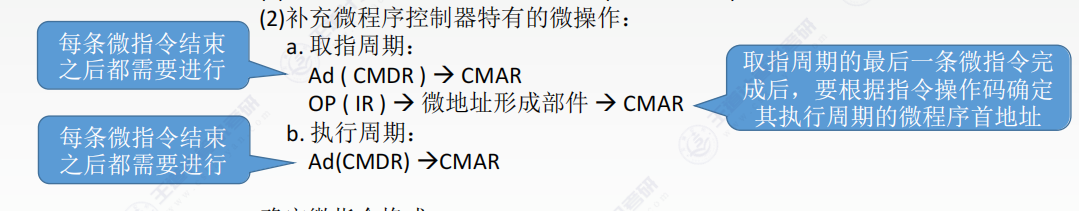

微程序控制單元設計

與硬布線控制單元設計做對比

絕大多數都一樣,但唯一的區別在最后:把形成的微命令 交給 微地址形成部件 最后形成微命令+微地址的形式組成微指令

而硬布線是直接把這樣的微命令做成電路去實現

也正是因為這個特性 他的每一個微命令段(由若干微命令形成的微命令段)多一個節拍 用于把下一次的微命令存到CMAR 作用是為了讓機器知道 “下一步”執行誰

這也是他跟硬布線控制器最大的區別?

靜態微程序設計和動態微程序設計(小知識點 )

靜態

動態

指令流水線

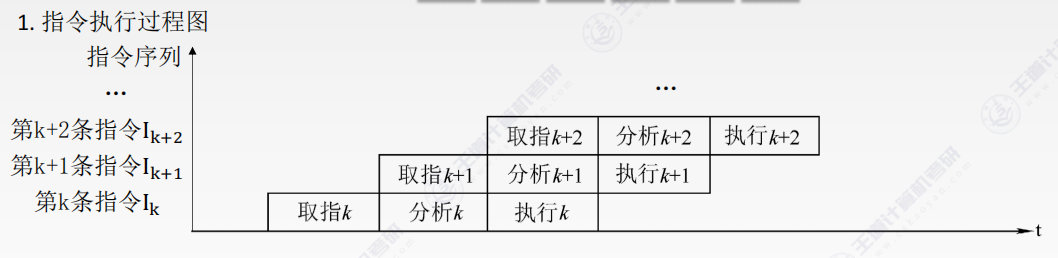

是CPU中的一種技術,它允許多個指令在不同的階段同時進行處理,從而提高執行效率。指令流水線的基本步驟包括:

- 取指周期:根據程序計數器(PC)中的內容從指定地址讀出指令代碼并放在指令寄存器(IR)中。

- 譯碼周期:對指令進行譯碼,確定需要的操作和操作數。

- 執行周期:根據指令的操作碼和操作數執行相應的操作。

- 訪存周期:如果需要,訪問內存以獲取或存儲數據。

- 寫回周期:將執行結果寫回寄存器或內存。

流水線技術可以并行處理多個指令,但也可能遇到一些問題,如數據沖突、控制沖突等,需要采取相應的策略來解決。

指令流水線的本質

就是把一個動作拆解成無數個細小的動作 (由不同的部件完成不同的動作)? 然而流水線就體現在 異步? 通俗點講就是你是切菜的 你不用上一個菜做完 你就一直切菜 你的任務不需要等到別人執行完成你才能夠開始? 這就叫異步? 流水線的本質 就是希望將各種部件最大異步化? 僅此而已

在設計指令流水線時,需要考慮以下幾個方面:

- 指令的順序:指令順序不能改變,以確保程序的正確性。

- 指令的并行性:編譯器可以通過分析指令之間的依賴關系,將能夠并行執行的指令合并成一條超長指令字,以提高執行效率

指令流水線是一種在CPU中用于提高指令執行效率的技術,它將指令的執行過程分解成多個子過程,這些子過程可以并行執行。然而,在指令流水線的設計和實現中存在一些易錯點,這些易錯點在考題中也經常被考察。以下是一些指令流水線中的易錯點和相關問題:

易錯點

-

資源沖突(結構相關):當多條指令同時爭用同一資源時會發生結構相關,導致流水線中斷或效率降低。

-

數據相關(數據冒險):某些指令依賴于前一條指令的結果,如果前一條指令的結果尚未計算完成,后一條指令就無法執行。

-

控制相關(控制冒險):轉移指令和程序計數器的改變可能導致流水線中斷。

-

流水線的啟動和排空:流水線在開始時需要一定的時間來填滿各個階段,稱為啟動時間;在最后一條指令執行完畢后,流水線需要一段時間來清空,稱為排空時間。

-

超標量流水線的指令亂序發射:超標量流水線允許在一個時鐘周期內發射多條指令,但需要處理指令亂序執行帶來的問題。

-

異常和中斷的處理:流水線需要能夠處理異常和中斷,這可能會影響流水線的效率。

考題

-

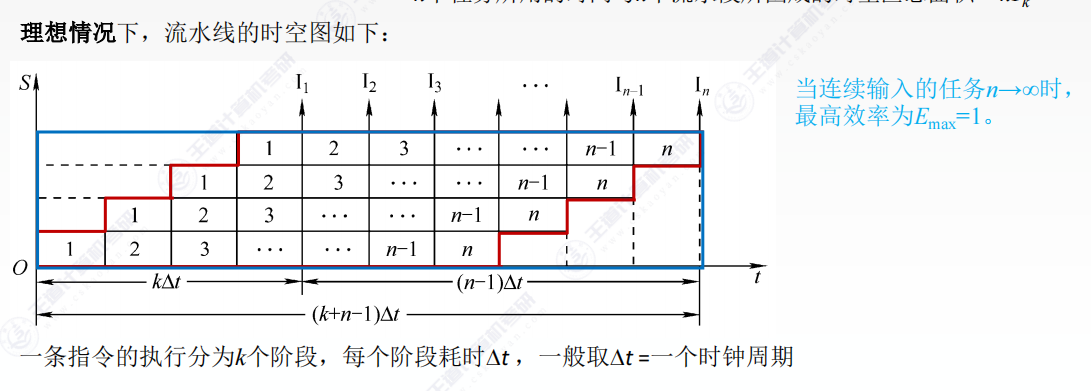

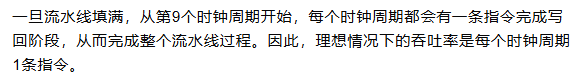

計算流水線的性能指標:如吞吐率、加速比、效率等。

- 吞吐率:單位時間內完成的指令數量。

- 加速比:引入流水線后與未引入流水線的執行時間之比。

- 效率:流水線中各功能的利用率。

-

分析流水線中的相關類型:確定指令流水線中可能發生的數據相關、控制相關和結構相關。

-

設計超標量流水線:設計一個超標量流水線,并分析其CPI(每條指令的時鐘周期數)。

-

處理異常和中斷:設計流水線的異常和中斷機制,確保流水線在遇到異常情況時能夠正確處理。

-

流水線的優化:提出方法來減少流水線的啟動時間和排空時間,提高流水線的效率。

-

指令流水線的實現:給出指令流水線的具體實現方式,包括數據通路的設計、控制信號的生成等。

示例問題

假設有一個五段式指令流水線,包括取指、譯碼、執行、訪存和寫回五個階段。請計算以下情況:

- 吞吐率:如果有8條指令需要執行,每個時鐘周期完成一個階段,那么吞吐率是多少?

- 加速比:如果沒有流水線,執行這8條指令需要多少時鐘周期?引入流水線后,加速比是多少?

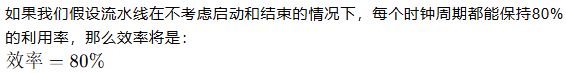

- 效率:如果流水線的設備利用率是80%,那么流水線的效率是多少?

可以嘗試自己根據理解做一下哦? 下一期把做題筆記發出來

答案:

![]()

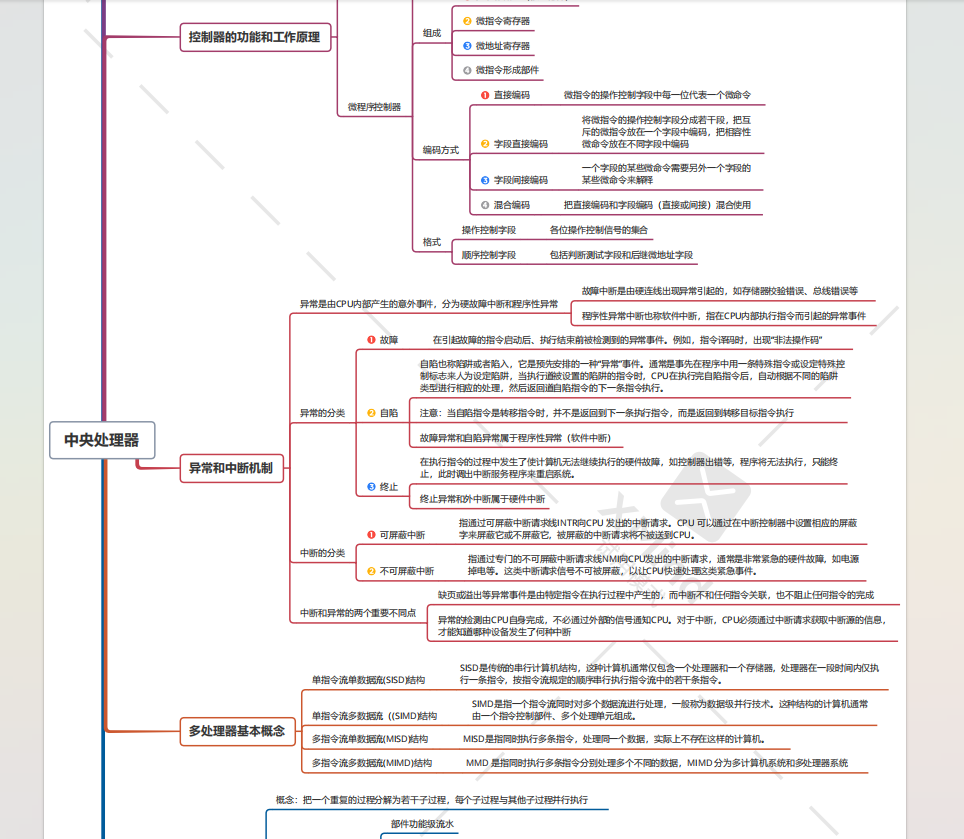

另外,利用了工作之余的一點點時間,整理了一套考研408的知識圖譜,

我根據這一套知識圖譜打造了這樣一個408知識圖譜問答系統

里面的每一個回答都是根據考研408的考點回復的

目前暫時只接入了微信,如果大家對這個問答系統感興趣的話可以在我的主頁里找到我的微信號

找我拉進測試群免費體驗哦

--學習記錄之迭代器與生成器(下))

9千字好文)