目錄

- 1.Verilog提供多級邏輯強度。

- 2.基本單元強度說明語法

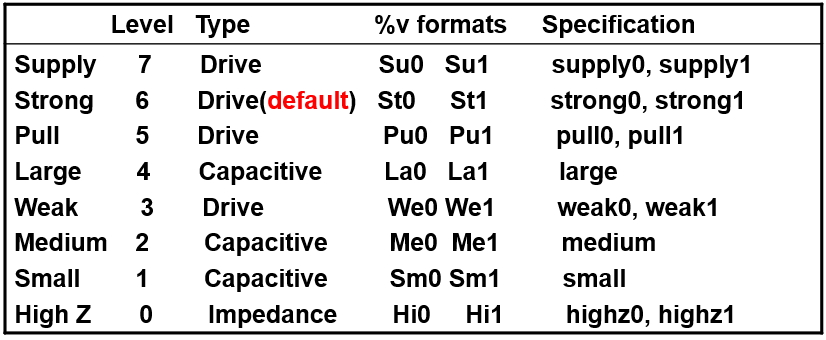

- 3.信號強度值系統

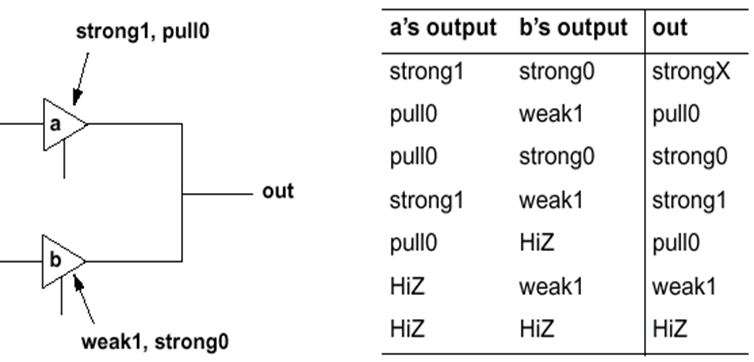

- 4.Verilog多種強度決斷

微信公眾號獲取更多FPGA相關源碼:

1.Verilog提供多級邏輯強度。

- 邏輯強度模型決定信號組合值是可知還是未知的,以更精確的描述硬件的行為。

- 下面這些情況是常見的需要信號強度才能精確建模的例子。

- 開極輸出(Open collector output)(需要上拉)

- 多個三態驅動器驅動一個信號

- MOS充電存儲

- ECL門(emitter dotting)

- 邏輯強度是Verilog模型的一個重要部分。通常用于元件建模,如ASIC和FPGA庫開發工程師才使用這么詳細的強度級。但電路設計工程師使用這些精細的模型仿真也應該對此了解。

- 用戶可以給基本單元實例或net定義強度。

2.基本單元強度說明語法

- <基本單元名> <強度> <延時> <實例名> (<端口>);

例:

nand (strong1, pull0) #( 2: 3: 4) n1 (o, a, b); // strength and delay

or (supply0, highz1) (out, in1, in2, in3); // no instance name

- 用戶可以用%v格式符顯示net的強度值

m o n i t o r ( monitor ( monitor( time," output = %v", f);

- 電容強度(large, medium, small)只能用于net類型trireg和基本單元tran

例如:

trireg (small) tl;

3.信號強度值系統

4.Verilog多種強度決斷

- 在Verilog中,級別高的強度覆蓋級別低的強度。

微信公眾號獲取更多FPGA相關源碼:

元素定位 xpath定位css定位)

)

格式的視頻 H.264格式的可以播放)