- S32K3 系列 eMIOS 介紹

1.1 資源介紹

該設備具有 3 個 eMIOS 模塊,每個模塊的配置如表 1.1 所示。

1.2 功能介紹

eMIOS 提供了用于生成或測量時間事件的功能。它使用 UCs,您可以為不同的芯片應

用中的不同功能進行編程。此外,eMIOS 體系結構允許使用執行特定功能的專用通道。

1.2.1 通道配置

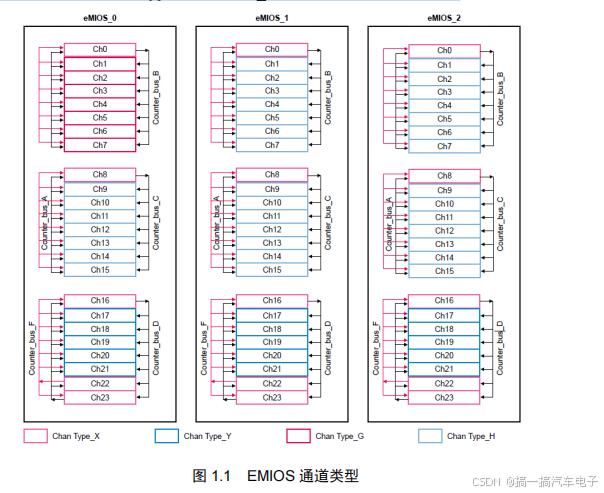

下面圖 1.1 顯示了有關 Type 和 Counter_bus 的 eMIOS 通道配置。

1.2.2 框圖

1.2.3 功能

? 在統一或專用通道中最多選擇 24 個通道,不必按連續順序編號

? 8 位,16 位,24 位或 32 位寬度的數據寄存器

? 計數器總線 B,C,D 可以分別由 UC 0、8 和 16 驅動計數器總線 A 可以由 UC 23 驅動。

? 計數器總線 F 可以由系統配置定義的 UC 驅動。

? 每個通道都有自己的時基,與計數器總線不同

? 兩個全局預分頻器

? 每個通道一個 CP

? 通過計數器總線共享時基

? 每個 UC 都有自己的一組控制和狀態寄存器

? 時基之間的同步

? 影子標志寄存器(全局標志(GFLAG))

? 可以凍結 UC 狀態以進行調試

? 電機控制能力

您可以將 UC 配置為在以下模式下運行:

? 通用輸入/輸出(GPIO)模式

? 單邊沿輸入捕捉(SAIC)模式

? 單動作輸出比較(SAOC)模式

? 輸入脈沖寬度測量(IPWM)模式

? 輸入周期測量(IPM)模式

? 雙動作輸出比較(DAOC)模式

? 脈沖/邊沿計數(PEC)模式

? 模數計數器(MC)模式

? 模數計數器緩沖(MCB)模式

? 輸出脈沖寬度和頻率調制緩沖(OPWFMB)模式

? 具有死區插入緩沖的中心對齊輸出脈沖寬度調制(OPWMCB)模式

? 輸出脈沖寬度調制緩沖(OPWMB)模式

? 帶觸發的輸出脈沖寬度調制(OPWMT)模式

每個通道可以具有一組特定的模式。

1.2.4 功能描述

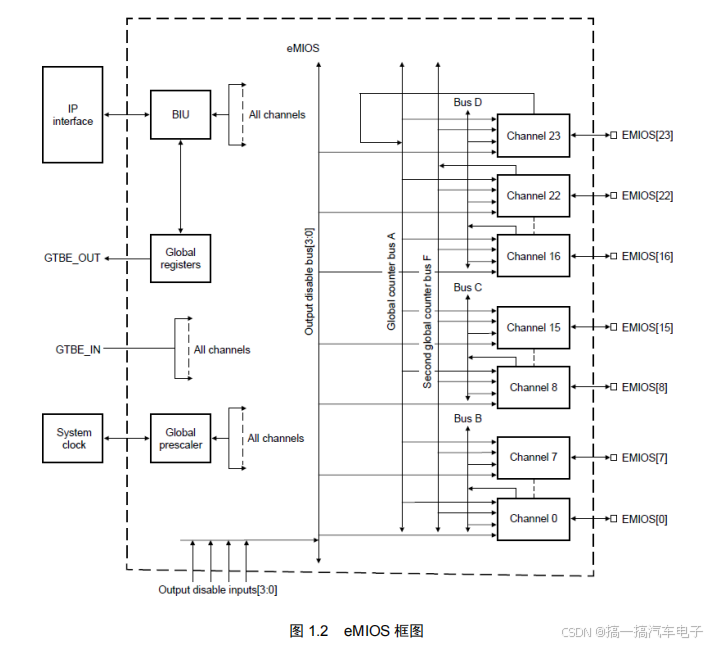

eMIOS 提供了獨立的統一通道,可由主機 MCU 配置和訪問。通道們最多可以共享五個

時基,但每個通道只能有一個時基。

eMIOS 模塊基于多總線計時器體系結構,其中多個計時器通道用于驅動在通道之間共

享的計數器總線,也就是說有些用作計數器的通道可以用于作為驅動計數器的通道。通過五

個計數器總線,通道們最多可以共享五個時基,每個通道可以生成自己的時基。有兩條全局

計數器總線:時基 A 和時基 F,可以被所有通道共享,可以在時基 A 或 F 中進行選擇作為

全局計數器總線;還有三條本地計數器總線(B,C,D),每條專用于 8 個通道。計數器總

線 A 和 F 稱為全局計數器總線。計數器總線 B,C,D 是本地計數器總線。

eMIOS 計數器總線是由特定位置的通道驅動的。全局計數器總線 A 由通道插槽[23]中

的通道驅動,計數器總線 F 由通道插槽 22 中的通道驅動。計數器總線 B,C,D 分別由插

槽 0、8 和 16 中的通道驅動。計數器總線 A 或 F 驅動所有通道。計數器總線 B 驅動從 0 到

7 的插槽中的通道。計數器總線 C 驅動從 8 到 15 的插槽中的通道。計數器總線 D 驅動從 16

到 23 的插槽中的通道。

eMIOS 模塊異步復位。復位時,所有寄存器均被清除。

1.2.5 模數計數器(MC)模式

MC 模式可用于為計數器總線或通用計時器提供時基。

MODE [0]位分別在清零或置位時選擇內部或外部時鐘源。選擇外部時鐘時,將輸入信

號引腳用作時鐘源,并通過 EMIOSC [n]寄存器中的 EDPOL 和 EDSEL 選擇觸發極性邊沿。

內部計數器從當前值開始遞增計數,直到與寄存器 A1 中的值匹配為止。寄存器 B1 被

清除,MCU 無法訪問。MODE [2]位分別在清除或設置時選擇向上模式或向上/向下模式。

在遞增計數模式下,內部計數器和寄存器 A1 之間的匹配將設置 FLAG 并清除內部計數

器。

這些事件的時間根據 MC 模式設置而有所不同,如下所示:

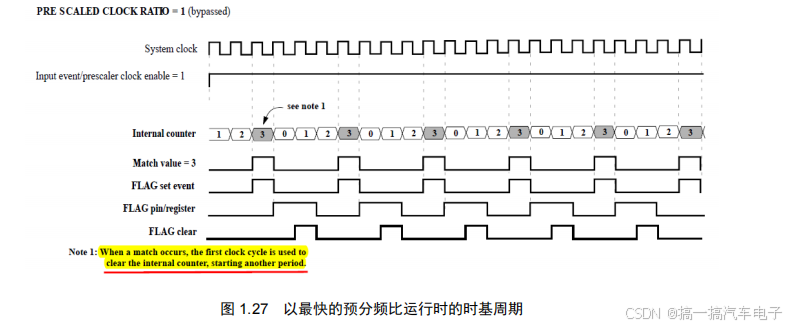

? 匹配開始時內部計數器清除(MODE[6:0] = 001000b)

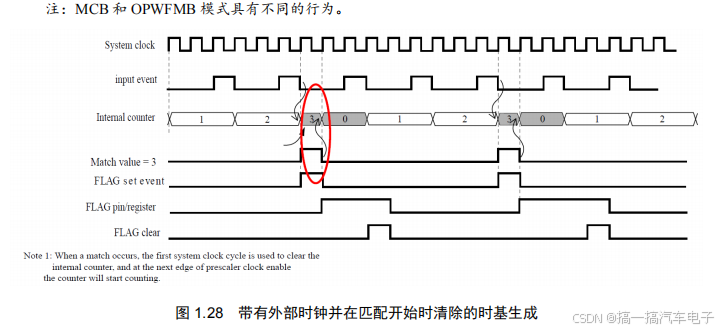

—如果設置了 MODE[6],則選擇外部時鐘。在這種情況下,一旦出現匹配信號,內部

計數器就會清除。匹配發生的同時設置通道 FLAG。請注意,通過在發生匹配時立即清除內

部計數器,并在下一個輸入事件時將其遞增,便會生成較短的零計數。參見圖 1.27 和圖 1.28。

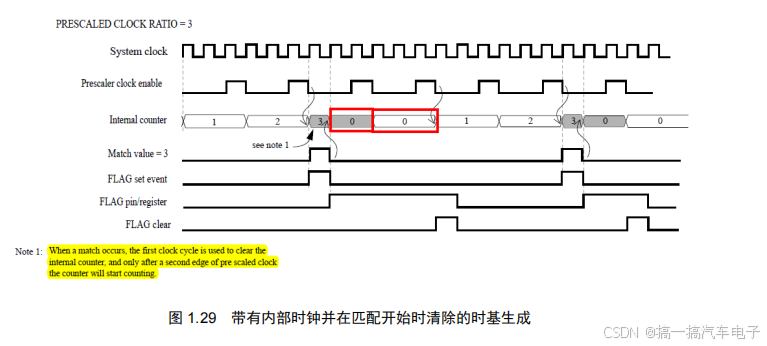

—如果清除了 MODE[6],則選擇內部時鐘源。在這種情況下,一旦出現匹配信號,計

數器就會清除。匹配發生的同時設置通道 FLAG。匹配結束后的下一個預分頻器滴答時,內

部計數器保持為零,僅在下一個滴答時恢復計數。參見圖 1.27 和圖 1.29。

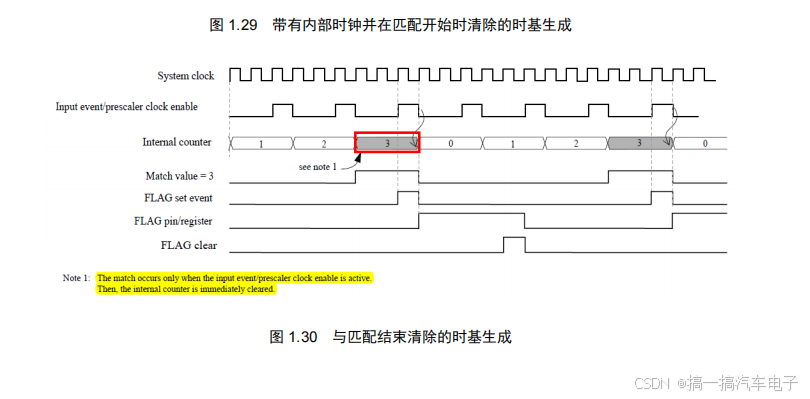

? 匹配結束時的內部計數器清除(MODE[6:0] = 001001b)

—如果設置了 MODE[6],則選擇外部時鐘。在這種情況下,當匹配信號有效并且發生

輸入事件時,內部計數器將清零。清除計數器的同時設置通道 FLAG。參見圖 1.27 和圖 1.30。

—如果清除了 MODE[6],則選擇內部時鐘源。在這種情況下,當匹配信號有效并且發

生預分頻器滴答時,內部計數器將清零。清除計數器的同時設置通道 FLAG。參見圖 1.27

和圖 1.30。

注:如果選擇了內部時鐘源,并且內部計數器的預分頻器設置為 1,MC 模式的行為相同,即使在“匹

配開始時清除”或“匹配結束時清除”子模式下也是如此。

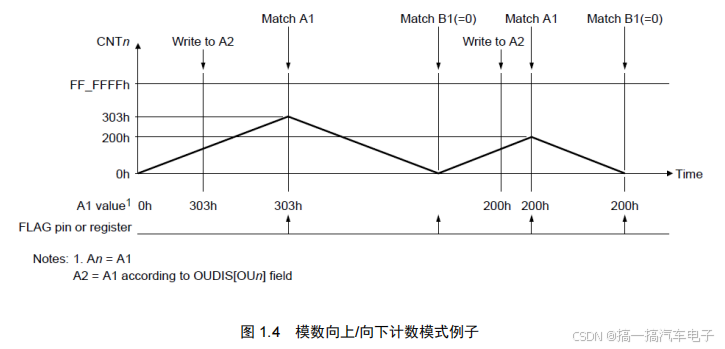

當處于遞增/遞減計數模式(MODE[6:0] = 00101bb)時,內部計數器與寄存器 A1 之

間的匹配將設置 FLAG,并將計數器方向從遞增更改為遞減。寄存器 B1 與內部計數器之間

的匹配將計數器的方向從遞減更改為遞增,并且僅在 MODE[1]位置 1 時設置 FLAG。

只能將非 0x0 的值寫入 A 寄存器。加載 0x0 會導致不可預測的結果。

如果傳輸在匹配附近發生,則在 MC 模式下對寄存器 A 或計數器的更新可能會導致當

前周期的匹配丟失。

在這種情況下,計數器可能會翻轉并在下一個周期恢復操作。

寄存器 B2 在 MC 模式下無效。不過,可以通過尋址 EMIOSB 來訪問寄存器 B2 以進行

讀取和寫入。

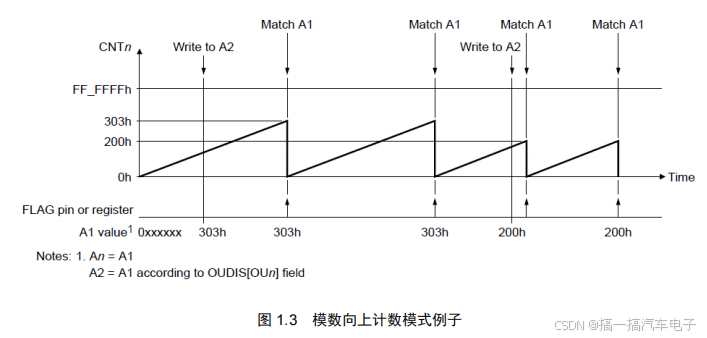

圖 1.3 和圖 1.4 顯示了如何分別在向上模式和向上/向下模式下將統一通道作為模數計數

器。

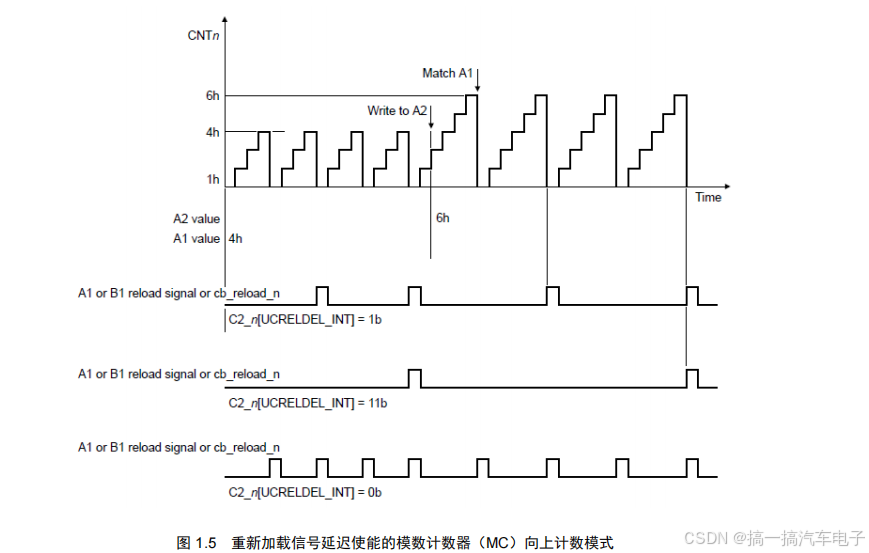

每當計數器值與向上模式下的 A1 寄存器或向上/向下模式下的 B1 寄存器匹配時,MC

模式下的統一通道都會生成一個“計數器總線重載信號”。該重載信號可以由在 OPWMB,

OPWFMB,OPWMCB 模式下運行的相關 UC 使用。也可以延遲“計數器總線重載信號”,

以便在第 n 個時機(n = 2、3、4,… 32)生成重載信號。重新加載信號延遲使能的模數計數

器(MC)向上計數模式如圖 1.5 所示

1.2.6 模數計數器緩沖(MCB)模式

MCB 模式提供了一個時基,可以通過內部計數器總線與其他通道共享該時基。寄存器

A1 是雙緩沖的,因此在動態更改 A2 寄存器值時允許在周期之間平滑過渡。寄存器 A1 在周

期邊界更新,周期邊界定義為內部計數器轉換為 0x1 時的邊界。

內部計數器的值在 0x1 到寄存器 A1 值的范圍內運行。如果從 GPIO 模式進入 MCB 模

式時,內部計數器值不在 A1 值范圍內,則不會發生 A 匹配,這從而導致通道內部計數器換

為 16 位計數器的最大計數器值,即 0xffff。計數器變換發生后,它將返回 0x1 并恢復正常的

MCB 模式操作。因此,為避免計數器變換條件,請確保進入 MCB 模式時計數器值在 0x1

以內以寄存器 A1 的值范圍。

MODE[0]位選擇內部時鐘源(如果清零)或外部時鐘源(如果置位)。選擇外部時鐘時,

輸入通道引腳用作通道時鐘源。該時鐘的有效沿由 EMIOSC[n]通道寄存器中的 EDPOL 和

EDSEL 位定義。

進入 MCB 模式時,如果通過 MODE [2] = 0(MODE[6:0] = 101000b)選擇了遞增計數

器,則內部計數器將從其當前值開始向上計數,直到發生 A1 匹配為止。當內部計數器的值

與 A1 值匹配并且發生時鐘滴答(預分頻時鐘或輸入引腳事件)時,內部計數器將設置為 0x1。

如果通過設置 MODE[2] = 1 選擇了遞增/遞減計數器,則計數器會在 A1 匹配處改變方

向并遞減計數,直到達到值 0x1。達到 0x1 后,將其設置為再次向上計數。如果選擇了向上

/向下模式,則寄存器 B1 用于產生匹配,以便將內部計數器設置為向上計數方向。選擇此模

式時,不能更改寄存器 B1。

請注意,與 MC 模式不同,MCB 模式在 0x1 和 A1 寄存器值之間計數。只能將大于 0x1

的值寫入寄存器 A1。加載那些值之外的值會導致不可預測的結果。在遞增計數器模式下,

計數器周期等于 A1 值。如果處于遞增/遞減計數器模式,則周期由以下表達式定義:(2 * A1)

-2。

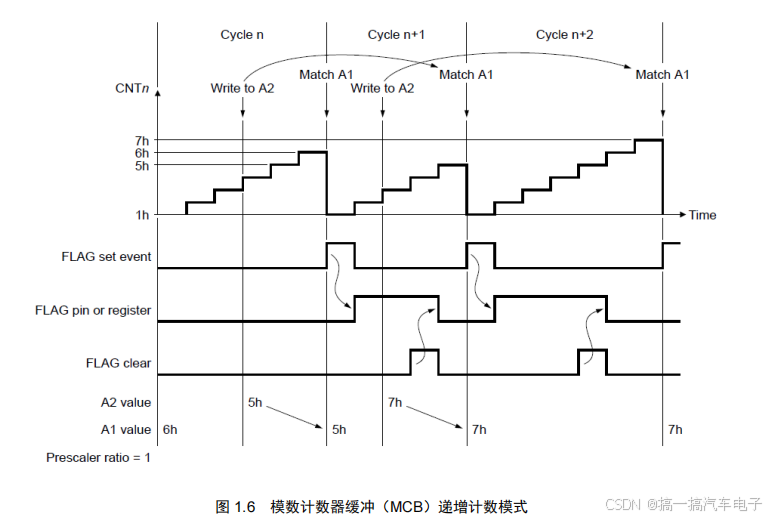

圖 1.6 描述了幾個 A1 值的計數周期。寄存器 A1 在循環邊界處加載有 A2 寄存器值。因

此,在周期 n 內寫入 A2 寄存器的任何值都將在下一個周期邊界更新為 A1,因此將在周期 n

- 1 上使用。定義周期 n 和周期 n + 1 之間的周期邊界為內部計數器從周期 n 中的 A1 值過渡

到周期 n + 1 中的 0x1 的時間。請注意,FLAG 在周期邊界生成并具有同步操作,這意味著

在 FLAG 設置事件后的一個系統時鐘周期將其置為有效。

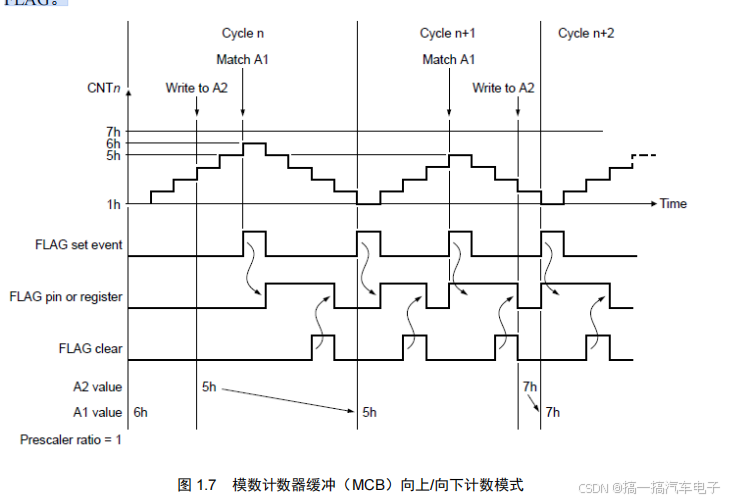

圖1.7描述了向上/下計數器模式的 MCB(模式[6:0] = 10101BB)。寄存器 A1 在循環

邊界處更新。如果 A2 寫入循環 N,則此新值將用于 A1 匹配的循環 N + 1。如果 MODE [1]

為 0,僅在 A1 匹配啟動時生成 FLAG。如果 MODE [1]設置為 1,則在循環邊界處也產生

FLAG。

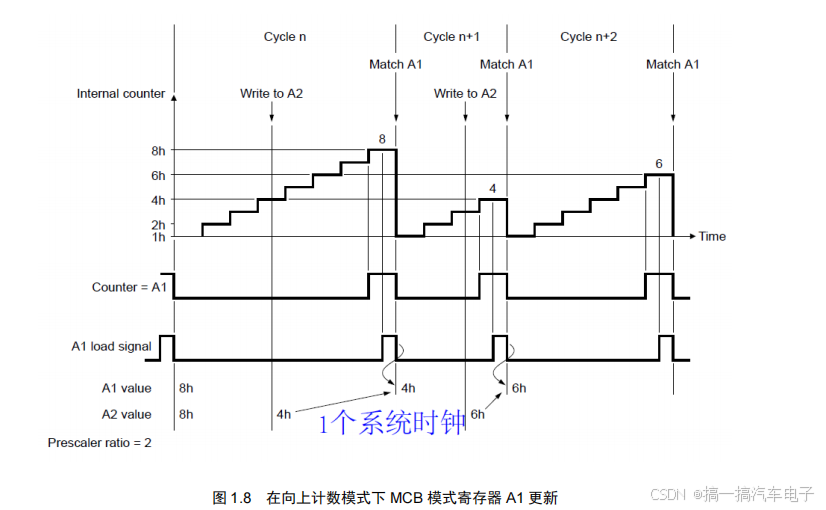

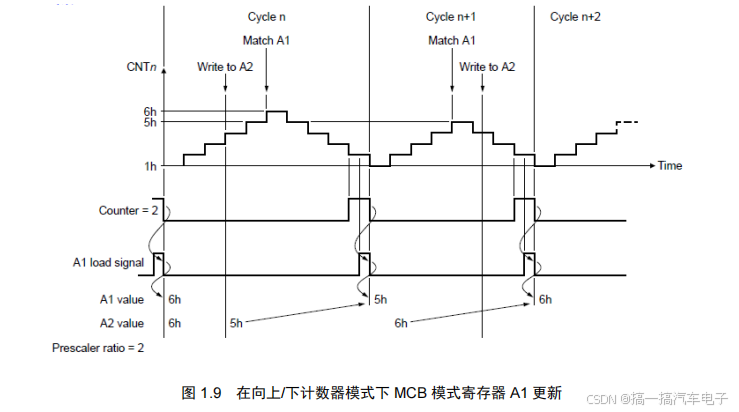

1.8圖 更詳細地描述了向上計數器模式下的寄存器 A1 更新過程。A1 加載信號在計數器

1.9描述了遞增/遞減計數器模式下的寄存器 A1 更新。注意,可以在周期 n 內的任何

時間寫入 A2,以便在周期 n + 1 中使用。因此,A1 在下一個循環邊界處接收到該新值。注

意,EMIOSOUDIS 寄存器的更新禁止位 OU [n]可用于禁止寄存器 A1 的更新。

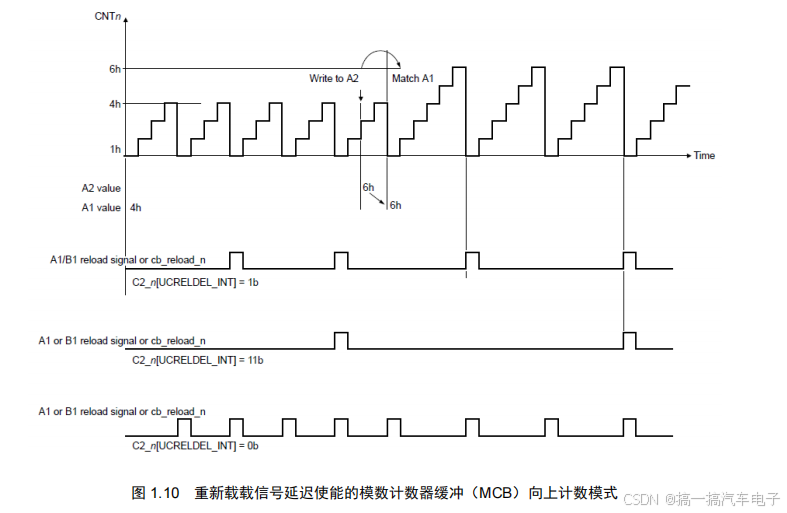

每當計數器值與向上計數模式下的 A1 寄存器或向上/向下計數模式下的 0x1 匹配時,

MCB 模式下的統一通道都會生成一個“計數器總線重載信號”。該重載信號可以由在

OPWMB,OPWFMB,OPWMCB 模式下運行的相關 UC 使用。也可以延遲“計數器總線重

載信號”,以便在第 n 次機會生成重載信號(n = 2、3、4,…32)。圖 1.10 是重新載載信號延

遲使能的模數計數器緩沖(MCB)向上計數模式的時序圖。

注:處于凍結狀態時,不應將 EMIOSCNT 寄存器的值寫入 0x1。原因:在 MCB 上下模式下,如果計

數器遞減至 1;否則,計數器遞減。將計數器覆蓋為 1 可能會錯過 B 匹配,并且計數器可能會溢出

1.2.7 輸出脈沖寬度和頻率調制緩沖(OPWFMB)模式

此模式(MODE[6:0] = 10110b0)提供占空比和頻率可變的波形。選擇此模式時,將

自動選擇內部通道計數器作為時基。寄存器 A1 指示占空比,而 B1 記錄頻率。寄存器 A1

和 B1 都經過雙緩沖,以在更改寄存器值時允許平滑的信號生成。支持 0%和 100%占空比。

在進入 OPWFMB 模式時,輸出觸發器被設置為 EMIOSC [n]寄存器中 EDPOL 位的值。

為了提供平穩一致的通道操作,此模式與 OPWFM 模式大不相同。主要區別在于 A1 和

B1 寄存器的更新,從 A1 匹配到輸出引腳轉換的延遲以及內部計數器值的范圍(從 0x1 開

始直到寄存器 B1 值)。

當進入從 GPIO 模式退出的 OPWFMB 模式時,內部計數器值不在 B1 值范圍內,則不

會發生 B 匹配,從而導致通道內部計數器換為 16 位計數器的最大計數器值,即 0xffff。計

數器變換發生后,它將返回 0x1 并恢復正常的 OPWFMB 模式操作。因此,為避免計數器變

換條件,請確保進入 OPWFMB 模式時計數器值在 0x1 至 B1 寄存器值范圍內。

當比較器 A 發生匹配時,輸出寄存器將設置為 EDPOL 的值。當比較器 B 發生匹配時,

輸出寄存器將設置為 EDPOL 的補碼。B1 匹配還會使內部計數器轉換為 0x1,從而重新啟動

計數器周期。

只允許將大于 0x1 的值寫入寄存器 B1。加載那些值之外的值會導致不可預測的結果。

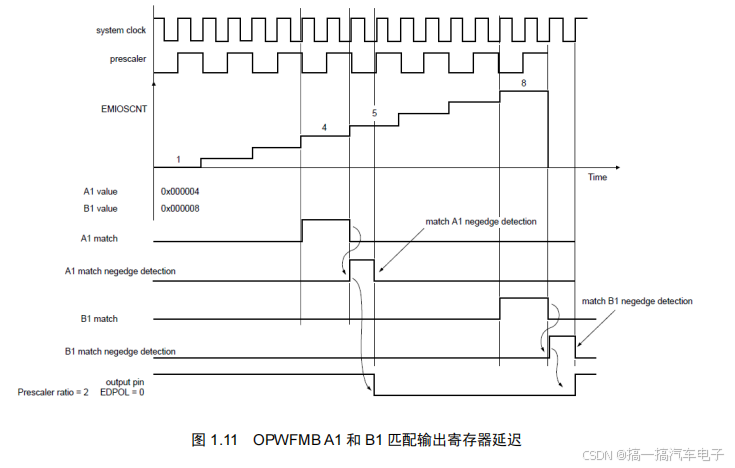

圖 1.11 描述了 OPWFMB 模式的操作,涉及輸出引腳轉換和 A1 / B1 寄存器匹配事件。

請注意,當 A1 或 B1 匹配信號置為無效時,將發生輸出引腳轉換,這由 A1 匹配忽略

檢測信號指示。如果寄存器 A1 設置為 0x4,則在周期開始后加上一個系統時鐘周期后,輸

出引腳將轉換 4 個計數器周期。請注意,在圖 1.11 所示的示例中,內部計數器預分頻器的

比率為 2。

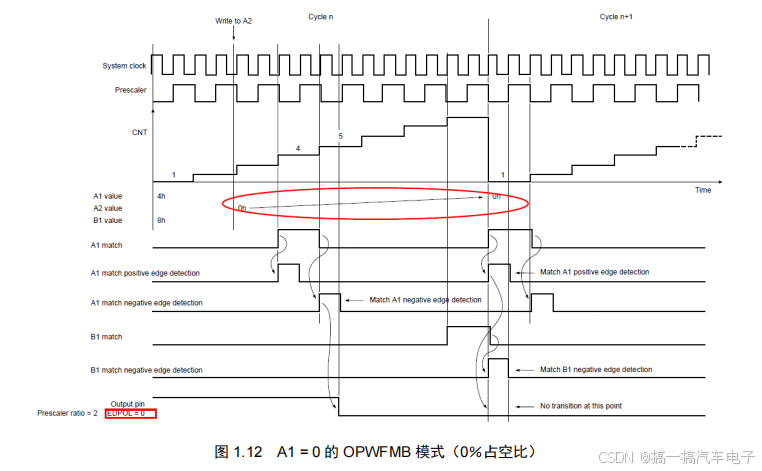

圖 1.12 描述了如果 A1 設置為 0x0 時產生的輸出信號。由于在此模式下計數器未達到零,

因此通道內部邏輯就像 A1 = 0x1 一樣推斷匹配,所不同的是,當 A1 = 0x1 時,在這種情況

下,使用匹配信號的擺幅來觸發輸出引腳轉換,而不是使用忽略值。注意,來自周期 n +1

的 A1 匹配信號與來自周期 n 的 B1 匹配信號同時出現。當它們同時發生時,這允許使用 A1

匹配來掩蓋 B1 忽略匹配。結果是在輸出觸發器上不會發生跳變,并且會產生 0%的占空比。

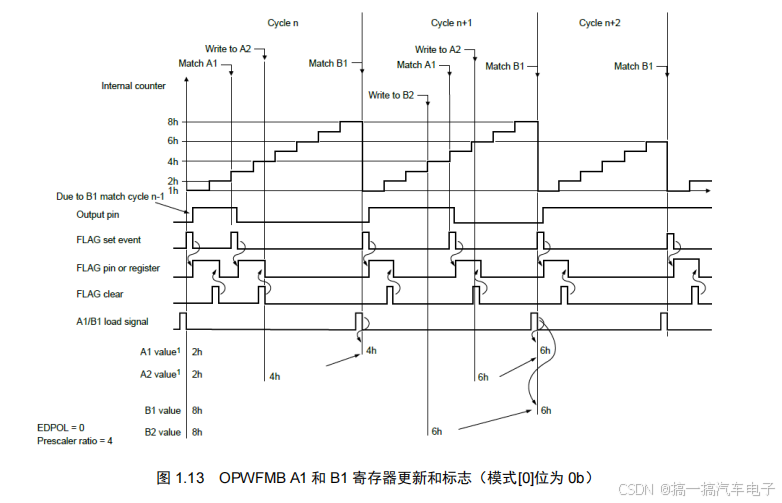

圖 1.13 描述了 A1 和 B1 寄存器加載的時序。A1 和 B1 加載信號在計數器周期的最后一

個系統時鐘周期生成的相同信號。因此,在計數器(EMIOSCNT [n])加載 0x1 的同時,分

別用 A2 和 B2 值更新 A1 和 B1。該事件定義為循環邊界。加載信號脈沖具有一個系統時鐘

周期的持續時間。如果在周期 n 內寫入 A2 和 B2,則它們的值分別在周期 n + 1 的第一個時

鐘在 A1 和 B1 可用,并且新值用于周期 n + 1 的匹配。EMIOSOUDIS 寄存器的更新禁止位

OU [n]可用于控制這些寄存器的更新,從而允許延遲 A1 和 B1 寄存器的更新以進行同步。

在圖 1.13 中,假定通道和全局預分頻器都設置為 0x1(每個分頻比為 2),這意味著通

道內部計數器每四個系統時鐘周期轉換一次。僅當 MODE [1]設置為 0 時在 B1 匹配上生成

FLAG,或者在 MODE [1]設置為 1 時在 A1 和 B1 匹配上生成 FLAG。由于 B1 標志出現在

周期邊界,因此該標志可用于指示將寫在周期 n 上的 A2 或 B2 數據分別加載到 A1 或 B1,

從而在周期 n + 1 中生成匹配項。請注意,FLAG 具有同步操作,這意味著在 FLAG 設置事

件后的一個系統時鐘周期將其置為有效。

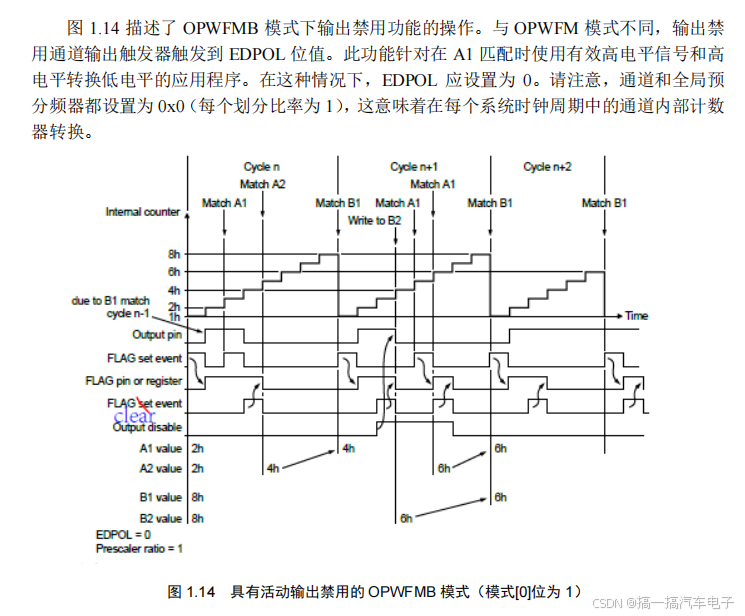

請注意,輸出禁用具有同步操作,這意味著輸出禁用輸入引腳的置位將導致通道輸出觸

發器在下一個系統時鐘周期轉換為 EDPOL。如果輸出禁用輸入被置為無效,則輸出引腳在

以下 A1 或 B1 匹配處轉換。

在圖 1.14 中,假設輸出禁用輸入已啟用并被通道選擇。請參考 UC 控制寄存器

(EMIOSCn),以獲得有關 ODIS 和 ODISSL 位(分別啟用和選擇輸出禁用輸入)的詳細說

明。

FORCMA 和 FORCMB 位分別允許軟件將輸出觸發器強制為對應于比較器 A 或 B 上的

匹配的電平。與 B1 匹配類似,FORCMB 將內部計數器設置為 0x1。FORCMA 或 FORCMB

位置為有效,不能把 FLAG 位置 1。

圖 1.15 描述了占空比為 100%和 0%的信號的產生。假設 EDPOL = 0,并且預分頻器的

最終值為 1。最初,A1 = 0x8,B1 = 0x8。在這種情況下,B1 匹配優先于 A1 匹配,因此輸

出觸發器被設置為 EDPOL 位的補碼。該周期對應于 100%的占空比信號。對于任何大于或

等于 B1 的 A1 值,都可以生成相同的輸出信號。

如圖 1.15 周期 9 所示,如果 A1 = 0x0,則產生 0%占空比信號。在這種情況下,與周期

9 的 A1 = 0x0 匹配同時發生周期 8 的 B1 = 0x8 匹配。有關 A1 和 B1 匹配生成的說明,請參

見圖 1.12。在這種情況下,A1 匹配優先于 B1 匹配,并且輸出信號轉換為 EDPOL。

1.2.8 死區時間插入的中心對齊輸出脈沖寬度調制緩沖(OPWMCB)模式

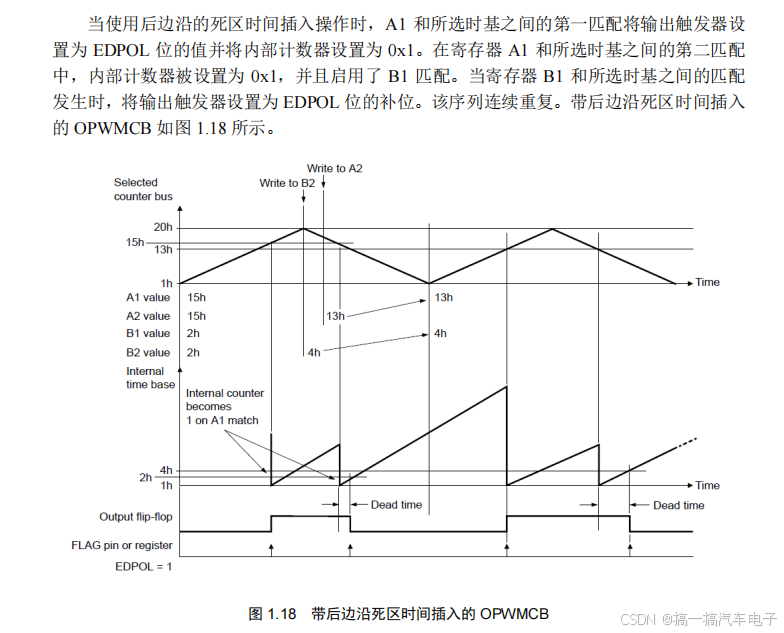

該操作模式生成一個死區時間插入前邊沿(模式[6:0] = 10111b1)或后邊沿(模式[6:

0] = 10111b0)的中心對齊的 PWM。A1 和 B1 寄存器是雙緩沖的,以允許在更改 A2 或 B2

寄存器值時允許平滑的輸出信號。

BSL [1:0]位選擇時基。被配置為 OPWMCB 模式的通道所選擇的時基應是配置為 MCB

向上/向下模式的通道,如圖 1.7 所示。建議在輸入 OPWMCB 模式后啟動 MCB 通道時基,

以避免在第一個占空比下丟失匹配項。

寄存器 A1 包含 PWM 信號的理想占空比,與所選時基進行比較。

寄存器 B1 包含死區時間值并與內部計數器進行比較。對于前邊沿死區時間插入,輸出

PWM 占空比等于寄存器 A1 和寄存器 B1 之間的差異,并且對于后邊沿死區時間插入,輸出

PWM 占空比等于寄存器 A1 和寄存器 B1 的總和。MODE[0]分別在后邊沿和前邊沿插入之

間選擇。

注:內部計數器以內部預分頻器的比率運行,而所選擇的時間基數可以以不同的預分頻器比率運行。

當輸入 OPWMCB 模式,從 GPIO 模式出來時,將輸出觸發器設置為 EMIOSC[n]寄存器

中 EDPOL 位的補位。

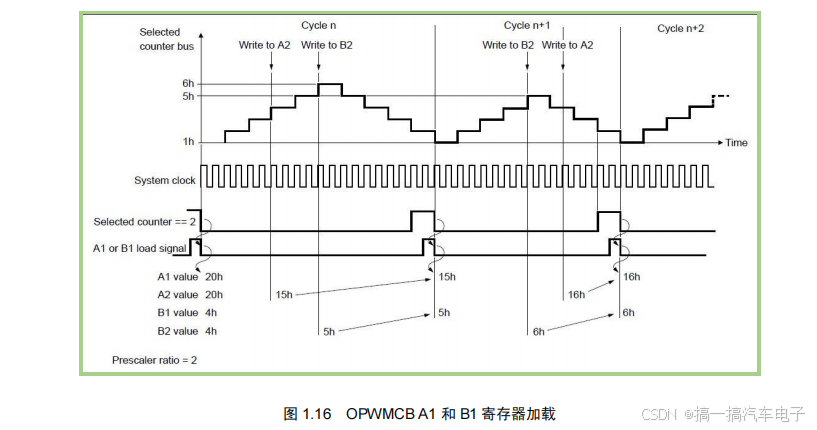

圖 1.16 描述了當所選擇的計數器總線從 0x2 到 0x1 轉換時發生 A1 和 B1 寄存器的加載。

此事件定義為循環邊界。注意,將在循環 n 內寫入 A2 或 B2 的值分別加載到 A1 或 B1 寄存

器中,并用于在循環 n + 1 中生成匹配。

EMIOUDIS 寄存器的 OU [n]位可用于禁用 A1 和 B1 更新,從而允許在其他通道中與

A1 或 B1 寄存器的加載同步這些寄存器上的加載。注意,使用更新禁用位 A1 和 B1 寄存器

可以在相同的計數器周期上更新,從而允許同時改變兩個寄存器。

在此模式下,A1 匹配始終將內部計數器設置為 0x1。當使用前邊沿死區時間插入時,

第一 A1 匹配將內部計數器設置為 0x1。當寄存器 B1 和內部時基之間發生匹配時,將輸出

觸發器設置為 EDPOL 位的值。在寄存器 A1 和所選時基接下來的匹配中,將輸出觸發器設

置為 EDPOL 位的補充。該序列連續重復。由于翻轉后,內部計數器不應達到 0x0。為了避

免它,用戶不應寫入 EMIOSB 寄存器的值大于外部計數限制和 EMIOSA 值之間的差異的兩

倍。

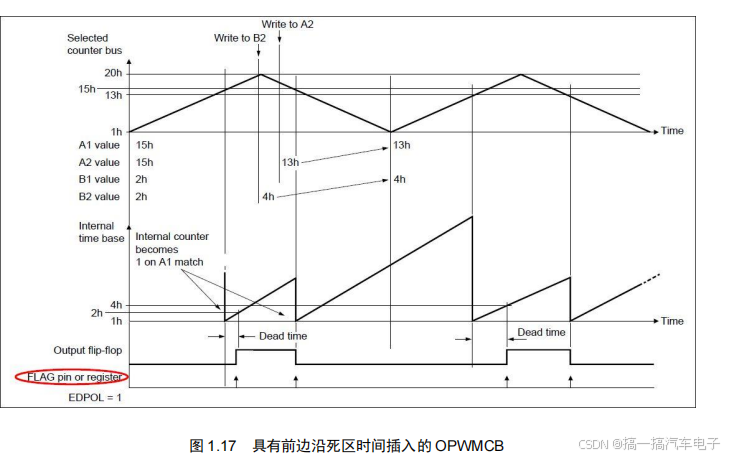

圖 1.17 顯示了中心對齊 PWM 信號的兩個循環。請注意,A1 和 B1 寄存器值都在同一

周期內更改,允許同時變化占空比和死區時間值。

PWM 信號可以在后邊沿當 MODE[1]設置為 0 時或者在前后邊沿當 MODE[1]設置為 1

時生成 FLAG。如果在比較器 A 和 B 上發生后續匹配,則不管 FLAG 位的狀態如何,繼續

生成 PWM 脈沖。

注:在 OPWMCB 模式下,FORCMA 和 FORCMB 與常規匹配沒有相同的行為。相反,它們將輸出觸

發器強制到恒定值,這取決于所選的死區時間插入模式,前邊沿或者后邊沿以及 EDPOL 位的值。

FORCMA 具有不同的行為,具體取決于所選擇的死區時間插入模式,前邊沿或者后邊

沿。在前邊沿死區時間插入 FORCMA 強制輸出觸發器過渡到 EDPOL 的補位。在后邊沿死

區時間插入,輸出觸發器被強制到 EDPOL 位的值。

如果設置了 FORCMB 位,則輸出觸發器值取決于所選的死區時間插入模式。在前邊沿

死區時間插入 FORCMB 強制輸出觸發器轉換到 EDPOL 位值。在后邊沿死區時間插入輸出

觸發器被強制與 EDPOL 值的補位。

注:FORCMA 位設置不會將內部時間基于 0x1 設置為常規 A1 匹配。

在 FORCMA 或 FORCMB 置位的情況下,不設置 FLAG 位,甚至是 ORCMA 和 FORCMB

同時置位。

注:FORCMA 和 FORCMB 即使在關于輸出引腳轉換的凍結或正常模式中也具有相同的行為。

當 FORCMB 和 FORCMA 一起置位時,輸出觸發器設置為相反的 EDPOL 位值。這等

于說,在選擇前邊沿插入死區時間時 FORCMA 的優先級高于 FORCMB,并且在選擇后邊

沿死區時間插入時 FORCMB 的優先級高于 FORCMA。

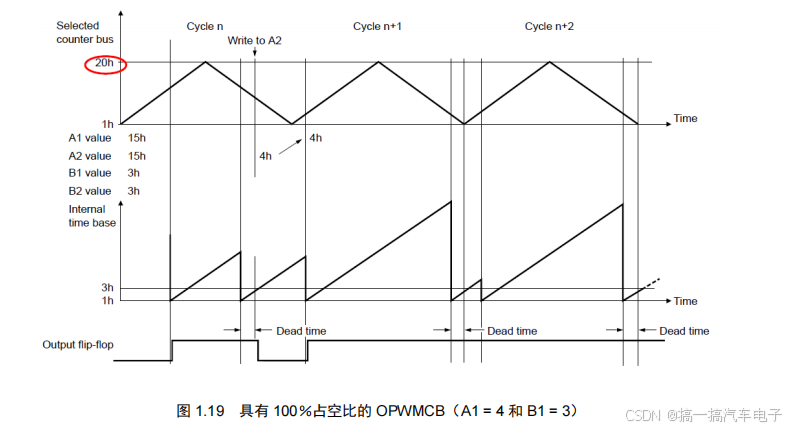

根據外部時基的周期,可以通過將適當的值設置為 A1 和 B1 寄存器來生成 0%至 100%

的占空比。設置 A1 = 0x1 生成 100%占空比波形。假設 EDPOL 被設置為 1 和帶后邊沿死區

時間插入的 OPWMCB 模式,如果 B1 發生在循環邊界(外部計數器= 1)之后,則可以生成

100%占空比信號。僅當引腳以 EDPOL 值的補位的當前周期開始,如果 A1 大于所選擇的計

數器總線周期的最大值,則才會產生 0%的占空比。在 100%占空比的情況下,可以通過使

用 FORCMA 和/或 FORCMB 來獲得從 EDPOL 到 EDPOL 的補位的轉變。

注:如果當 A1 在 OPWMCB 置為有效設置為 0x1,可能由于模式進入的時候引腳的電平,在第一個

PWM 周期中可能無法獲得 100%占空比。

只允許將不同于 0x0 的值寫入 A1 寄存器。如果 0x0 加載到 A1,則結果是不可預測的。

注:當 A1 設置為(外部計數器總線周期)/ 2 時,會發生特殊情況,這是外部計數器的最大值。在這

種情況下,輸出觸發器不斷設置為 EDPOL 位值。

內部通道邏輯可防止從一個周期匹配以傳播到下一個周期。在后邊沿死區時間插入 B1

匹配從循環 n 最終通過循環邊界越過并發生在循環 n + 1 中。在這種情況下,B1 匹配被屏蔽,

不會導致輸出觸發器轉換。因此,循環 n + 1 中的匹配不受來自循環 n 的 B1 匹配的影響。

圖 1.19 顯示了通過設置 A1 = 0x4 和 B1 = 0x3 產生的 100%占空比輸出信號。在這種情

況下,后邊沿位于循環 n + 1 的邊界處,實際上被認為屬于循環 n + 2,因此不會導致輸出觸

發器轉換。

輸出禁用功能(如果已啟用)會導致輸出觸發器轉換到 EDPOL 的補位狀態。此功能允

許應用程序將通道輸出引腳強制到“安全”狀態。即使在這種情況下,內部通道匹配也繼續

發生,從而生成 FLAG。一旦輸出禁用被禁用,通道輸出引腳再次由 A1 和 B1 匹配控制。

請注意,此過程是同步的,這意味著輸出通道引腳僅在系統時鐘邊緣轉換。

重要的是要注意到,例如在 OPWMB 和 OPWFMB 模式中,

用于設置或清除通道輸出觸發器的匹配信號在通道組合比較器輸出信號的失效上生成,

該頻道組合與 A1 或 B1 寄存器值比較信號。請參閱圖 1.11,該圖 1.11 描述了 OPWFMB 模

式下從匹配到輸出觸發器轉換的延遲。OPWMCB 模式在關于匹配和輸出引腳轉換的操作類

似于 OPWFMB。

1.2.9 輸出脈沖寬度調制緩沖(OPWMB)模式

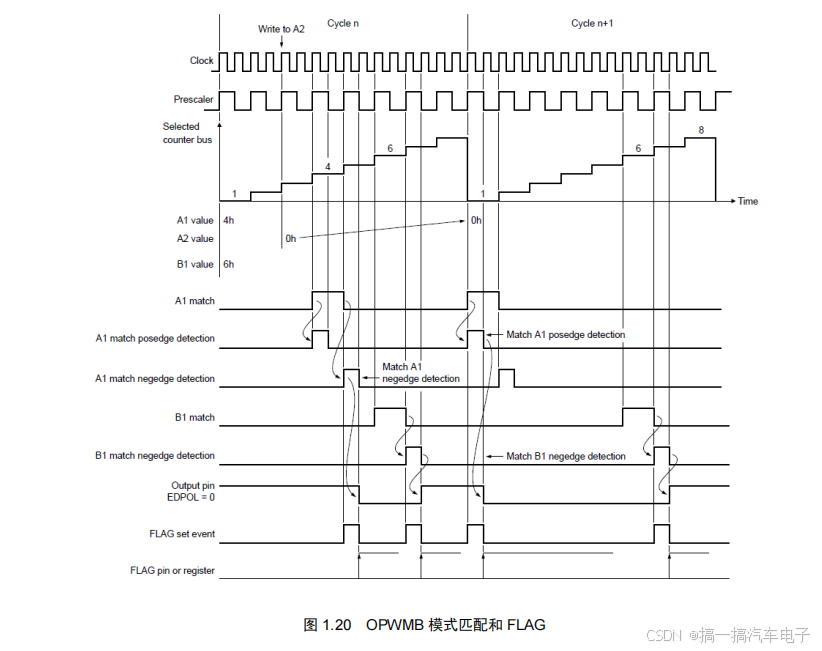

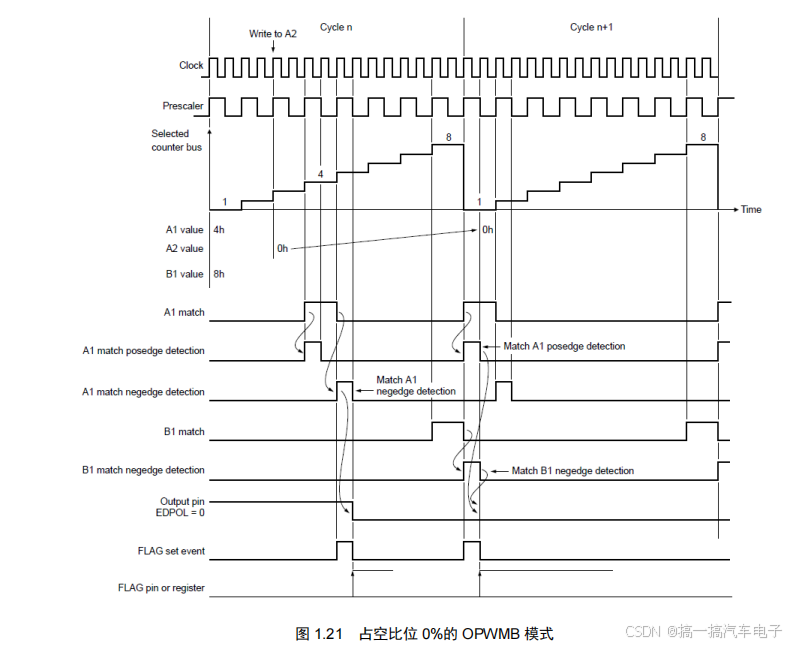

OPWMB 模式(MODE[6:0] = 11000B0)用于生成具有可編程前邊沿和后邊沿放置的

脈沖。必須從計數器總線中選擇一個 MCB 向上模式驅動的外部計數器。

A1 寄存器值定義第一個邊緣和 B1 寄存器定義第二邊緣。輸出信號極性由 EDPOL 位定

義。如果 EDPOL 為零,則當 A1 匹配所選擇的計數器總線時發生負邊沿,并且當 B1 與所

選計數器總線匹配時發生正邊沿。

A1 和 B1 寄存器在循環邊界處分別從 A2 和 B2 雙緩沖和更新。加載操作類似于

OPWFMB 模式。有關 A1 和 B1 寄存器更新的更多信息,請參閱圖 1.13。

當 Mode[1]清除時,B1 匹配時可以生成 FLAG,或當 MODE[1]置 1 時,在 A1 和 B1 匹

配可以生成 FLAG。如果在比較器 A 和 B 上發生后續匹配,則不管 FLAG 位的狀態如何,

繼續生成 PWM 脈沖。

FORCMA 和 FORCMB 位允許軟件強制輸出觸發器分別對應于 A1 或 B1 上匹配的電平。

FORCMA 和 FORCMB 操作不能設置 FLAG 位。

在 OPWMB 模式下,將輸出觸發器設置為 EMIOSC[n]寄存器中的 EDPOL 位的值。

適用于 OPWMB 模式的一些規則是:

? 如果在同一計數器周期內發生同時發生,B1 匹配最優先于 A1 匹配項;

? A1 = 0 匹配來自循環 n,優先于 B1 匹配從循環 n-1 匹配;

? 如果在同一周期內的 B1 匹配后發生,則屏蔽 A1 匹配項;

? 在循環 n 上寫入 A2 或 B2 的任何值都加載到以下循環邊界處的 A1 和 B1 寄存器(假

設 OUIOUDIS 寄存器的位不被置位)。因此,新值將用于循環 n + 1 中的 A1 和 B1

匹配。

圖 1.20 描述了關于 A1 和 B1 匹配的 OPWMB 模式的操作和通道輸出引腳的轉換。在此

示例中,EDPOL 設置為零。

請注意,輸出引腳轉換基于 A1 和 B1 匹配信號。圖 1.20 顯示了循環 n + 1 中的 A1 寄存

器的值設置為零。在這種情況下,使用匹配上升沿代替下降沿來轉換輸出觸發器。

圖 1.21 描述了 0%占空比的通道操作。請注意,A1 匹配的上升沿信號與 B1 = 0x8 下降

沿信號同時發生。在這種情況下,A1 匹配優先于 B1 匹配,使輸出引腳保持在 EDPOL 值,

從而產生 0%的占空比信號。

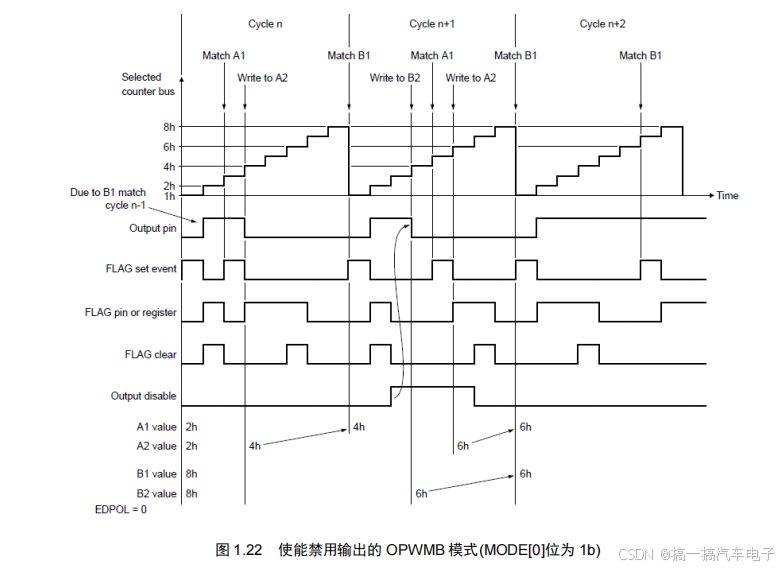

圖 1.22 描述了輸出禁用信號有效的 OPWMB 模式的操作。輸出禁用在輸出引腳中的轉

換強制轉換到 EDPOL 值。在輸出禁用信號為無效后,輸出禁用允許輸出引腳在接下來的

A1 或 B1 匹配時轉換。請注意,輸出禁用不會修改 FLAG 位行為。注意,在輸出禁用信號

的有效和輸出引腳的轉換之間存在一個系統時鐘延遲與 EDPOL 的轉換。

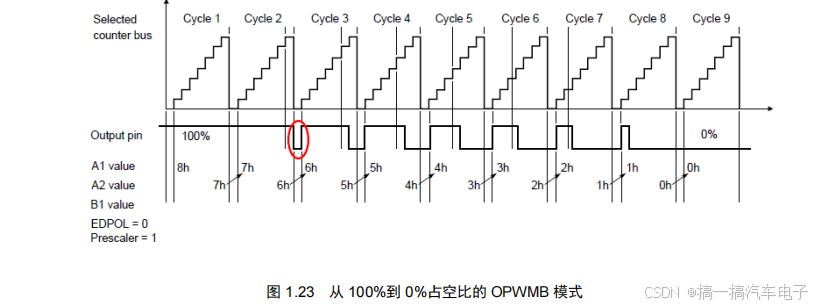

圖 1.23 顯示了從 100%到 0%占空比的波形。在這種情況下 EDPOL 為零。在該示例中,

B1 被編程為與外部所選時基的周期相同的值。

在圖 1.23 中,如果 B1 被設置為低于 0x8 的值,則通過僅通過改變 A1 寄存器值來實現

0%的占空比。

由于 B1 匹配優先于 A1,因此將輸出引腳轉換與 B1 匹配的 EDPOL 位的補位。還要注

意,例如如果 B1 設置為 0x9,不發生 B1 匹配,因此生成 0%占空比信號。

1.2.10 用觸發器(OPWMT)模式輸出脈沖寬度調制

OPWMT 模式(MODE[6:0] = 0100110)旨在支持產生脈沖寬度調制信號,其中在信

號輸出時不修改周期,但是在占空比將變化并且不得產生毛刺。該模式旨在與以相同模式執

行并共享共同時基的其他通道結合使用。它將支持相對于其他通道的固定 PWM 前沿位置的

每個信道以及在可以從模塊輸出的周期的任何點處產生觸發信號的能力,以啟動 SOC 的其

他部分中的活動,例如啟動 ADC 轉換。

必須從其中一個計數器總線中選擇以 MC 向上或 MCB 向上模式驅動的外部計數器。

寄存器 A1 定義 PWM 輸出脈沖的前沿,并如 PWM 期間的開始。這使得可以確保在使

用共享時基時可以在相對于其他通道的特定時間內發生 OPWMT 模式中的多個通道的前沿。

這可以允許引入每個通道的固定偏移,這在發光 PWM 控制信號的產生中可以特別有用,其

中期望邊緣彼此不一致以幫助消除噪聲產生。寄存器 A1 的值表示 PWM 通道相對于所選時

位的偏移。A1 可以配置在所選時基范圍內的任何值。請注意,如果時基模式由 MCB 模式

下的通道驅動,則加載有 0x0 的寄存器不會產生匹配。

由于在生成 PWM 信號時不得修改 PWM 通道的偏移,因此不緩沖 A1。在修改 A1 的情

況下,立即更新,一個 PWM 脈沖可能會丟失。

EMIOSB [n]地址可以訪問 B2 寄存器,用于寫入和 B1 寄存器。寄存器 B1 定義 PWM 輸

出脈沖的后邊沿,以及 PWM 信號的占空比。要使用 PWM 信號同步 B1 更新,因此確保正

確的輸出脈沖生成從 B2 到 B1 的轉移在寄存器 A1 的每一個匹配時完成。此行為與 OPWM

模式在下一周期更新的操作相同。

EMIOSOUDIS 寄存器僅影響 B2 和 B1 之間的傳輸。

為了考慮由寄存器 A1 定義的波形的前沿的偏移,將需要在寄存器 B1 中保持的后邊沿

可以進入下一個時段。這意味著對 B1 寄存器的匹配不必通過 A1 寄存器中的匹配項來限定。

這樣的影響意味著錯誤地將寄存器 B1 設置為小于寄存器 A1 的值將導致輸出在一個循環邊

界上保持,直到遇到 B1 值為止。

該模式通過僅在寄存器A1匹配時用寄存器 B2內容更新寄存器B1 來提供后沿的緩沖更

新。

將寄存器 A1 中的值與所選時基的值進行比較。當比較器 A1 上發生匹配時,將輸出觸

發器設置為 EDPOL 位的值。當比較器 B 上發生匹配時,將輸出觸發器設置為 EDPOL 位的

補位。

請注意,輸出引腳和 FLAG 轉換基于 A1,B1 和 A2 匹配信號的上升沿。有關匹配上升

沿的詳細信息,請參閱輸出脈沖寬度調制緩沖(OPWMB)模式的圖 1.20。

寄存器 A2 定義了 PWM 周期內的觸發事件的生成,A2 應配置在所選時基范圍內的任

何值,否則不會生成觸發器。比較器上的匹配將生成 FLAG 信號,但它對 PWM 輸出信號產

生沒有影響。典型的設置要獲取帶 FLAG 的觸發可以啟用 DMA 并驅動通道的 ipd_done 輸

入。

A2 沒有緩沖,因此其更新即時。如果通道在發生更改時運行,則可能導致一個觸發事

件的丟失或同一時段內的兩個觸發事件的生成。可以通過 eMIOS UC 在 UC [n]基地址的備

用 A 寄存器(eMIOS_ALTA)+ 0x14 中讀取或寫入來訪問寄存器 A2。

FLAG 信號僅在與 A2 上的比較器上匹配。使用 A1 或 B1 或 B2 的比較器上的匹配對

FLAG 沒有影響。

隨時,FORCMA 和 FORCMB 位允許軟件強制輸出觸發器分別對應于對應于 A 或 B 上

匹配的電平。任何 FORCMA 和/或 FORCMB 都優先于有關輸出引腳轉換的任何同時匹配。

注意,由于同時執行 FORCMA / FORCMB 置為有效,因此不禁止在 A 匹配處將 B2 內容加

載到 B1 寄存器中。如果同時 FORCMA 和 FORCMB 設置為有效,則輸出引腳為 EDPOL 值

的補位,例如 A1 和 B1 寄存器具有相同的值。FORCMA 置為有效導致從寄存器 B2 轉移到

B1,例如常規 A 匹配,無論 FORCMB 設置如何。

如果在比較器 A1 和 B 上發生后續匹配,則不管 FLAG 位的狀態如何,都會繼續產生

PWM 脈沖。

在 OPWMT 模式下,將輸出觸發器設置為 EMIOSC [n]寄存器中的 EDPOL 位的補位。

為了實現 0%占空比,寄存器 A1 和 B 必須設置為相同的值。當對比較器 A 和 B 的同時

匹配發生時,輸出觸發器在每個時段都設置為 EDPOL 的補位值。

為了達到 100%的占空比,必須將寄存器 B1 的值設置為大于所選時基的最大值,因此,

如果必須實現 100%的占空比,則對于 A 而言,時基的最大計數器值為 0xFFFFFE 24 位計

數器和 16 位計數器的 0xFFFE。當比較器 A1 發生匹配時,輸出觸發器在每個周期都設置為

EDPOL 位的值。從寄存器 B2 到 B1 的傳輸仍然由比較器 A 的匹配觸發。

與其他 EMIOS 模式一樣,OPWMT 模式將實現輸出禁用功能。在 EMIOS UC 控制寄存

器(EMIOSC[n])中設置 ODIS 位將啟用輸出禁用功能。如果所選輸出禁用輸入信號被置位

通道,則輸出引腳將轉到 EDPOL 的倒數。通道將繼續正常運行,但輸出將是固定的。當輸

出禁用輸入信號被否定時,輸出引腳將返回正常操作。

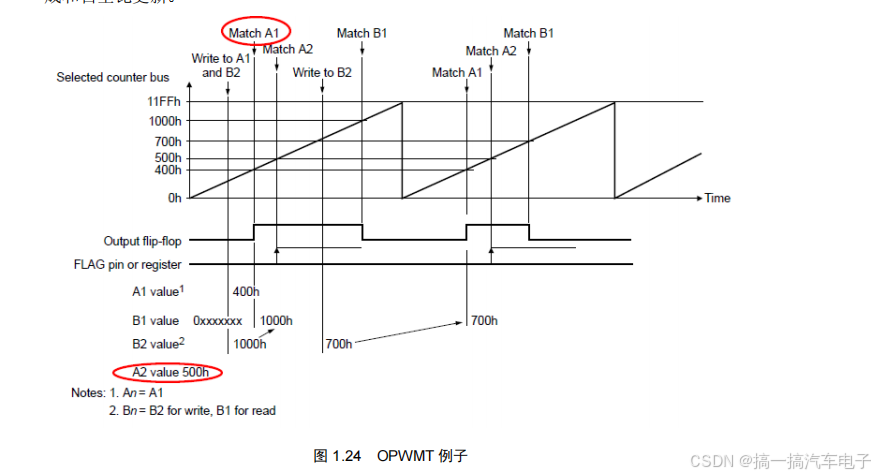

圖 1.24 顯示了在 OPWMT 模式下運行的統一通道,在下一周期更新中具有觸發事件生

成和占空比更新。

圖 1.25 顯示了在觸發事件生成 0%占空比 OPWMT 模式運行的統一通道。

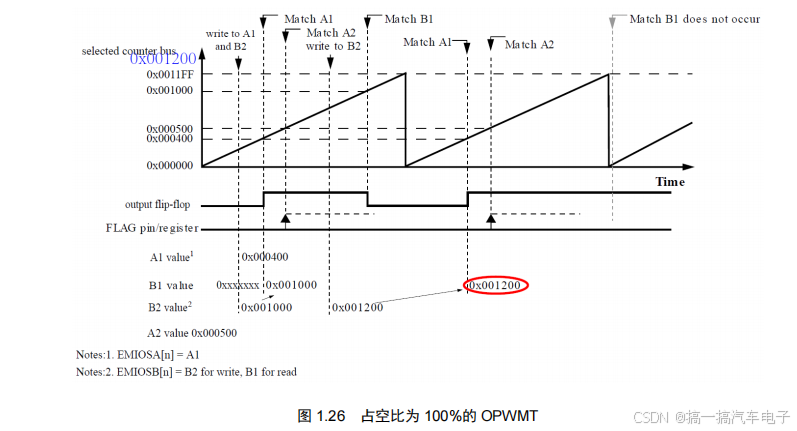

圖 1.26 顯示了在觸發事件生成 100%占空比 OPWMT 模式運行的統一通道。

1.2.11 時鐘預分頻器(CP)

CP 將 GCP 輸出信號劃分為為統一通道的內部計數器生成時鐘啟用。通過在 EMIOSC [n]

寄存器中的 UCPRE [1:0]字段描述中定義的值預先置換 GCP 輸出信號。通過在 EMIOSC [n]

中的 UCPREN 位來啟用預分頻器,并且可以通過清除該位隨時停止,從而停止統一信道中

的內部計數器。

為了確保安全工作并避免故障,每當需要預定速率的任何更新時,必須執行以下步驟:

- 在 EMIOSMCR 寄存器中的 GPREN 位和 EMIOC [n]寄存器中的 UCPREN 位,從而

在寄存器中寫入 0,從而禁用預分頻器; - 在 EMIOSC [n]寄存器中的 UCPRE [1:0]位的預分頻速率下寫出所需的值;

- 通過在 EMIOSC [n]寄存器中的 UCPREN 位,通過在 UCPREN 位中寫入通道預分

頻器; - 通過在 EMIOS MCR 寄存器中的 GPREN 位寫入 1 來啟用全局預分頻器。

在凍結狀態或否定 GTBE 輸入期間,預分頻器未禁用。

1.2.12 凍結對統一頻道的影響

當在調試模式下,EMIOSMCR 寄存器中的 FRZ 位和 EMIOSC [n]中的 FREN 位都設置,

內部計數器和統一通道捕獲和比較功能被停止。UC 在其當前狀態凍結。

在凍結期間,所有寄存器都可以訪問。當統一通道在輸出模式下運行時,匹配功能仍然

可用,允許軟件強制輸出到所需的電平。

請注意,對于輸入模式,忽略通道凍結時可能發生的任何輸入事件。

在退出調試模式或凍結啟用位時(EMIOSMCR 中的 FRZ 或 FREN 在 EMIOSC [n]寄存

器中),通道操作恢復,但在通道再次進入 GPIO 模式之前可能會不一致。

1.2.13 IP 總線接口單元(BIU)

BIU 在內部接口總線和外圍總線之間提供接口,允許所有子模塊和此 IP 接口之間的通

信。

BIU 允許 8,16 和 32 位訪問。它們在單個循環時鐘中的 32 位數據總線上執行。 - 凍結對 BIU 的影響

當設置 EMIOSMCR 寄存器中的 FRZ 位并且模塊處于調試模式時,BIU 的操作不受影

響。

1.2.14 全局時鐘預分頻器子模塊(GCP)

GCP 劃分系統時鐘以為通道的 CPS 生成時鐘。主時鐘信號由 EMIOSMCR 寄存器中的

GPRE [7:0]位中的全局預分頻器時鐘分頻器表中定義的值預先定義。通過在 EMIOSMCR

寄存器中設置 GPLEN 位,通過清除該位,可以隨時停止全局預分頻器,從而停止所有通道

中的內部計數器。

為了確保安全工作并避免故障,每當需要預定速率的任何更新時,必須執行以下步驟: - 在 EmioSMCR 寄存器中的 Gpren 位寫 0,從而禁用全局預分頻器;

- 在 EMIOSMCR 寄存器中的 GPRE [7:0]位,在 GPRE [7:0]比特中寫入所需的值;

- 通過在 EmiOSMCR 寄存器中的 Gpren 位寫入 1 來啟用全局預分頻器。

在凍結狀態或否定 GTBE 輸入期間,預分頻器未禁用。 - 凍結對 GCP 的影響

設置 EMIOSMCR 寄存器中的 FRZ 位并在模塊處于調試模式時,GCP 子模塊的操作不

受影響,即該子模塊中沒有凍結功能。

1.2.15 初始化/應用信息

在重置 EMIO 時,統一通道進入 GPIO 輸入模式。

在更改操作模式之前,必須將 UC 編程為 GPIO 模式,并且 EMIOSA [n]和 EMIOSB [n]

寄存器必須使用正確的下一個操作模式進行正確的值來更新。然后可以使用新的操作模式寫

入 EMIOSC [n]寄存器。如果在不執行此過程的情況下將 UC 從一種模式更改為另一種模式,

則所選時基的第一個操作周期可以是隨機的,即,如果 EMIOSA [n]或 EMIOSB [n]的內容為

在時基與 EMIOSA [n]或 EMIOSB [n]的先前內容匹配之前未使用正確的值更新。

啟用中斷時,軟件必須在退出中斷服務程序之前清除 FLAG 位。 - 應用信息

可以通過所有輸出操作模式生成相關輸出信號。EMIOS_OUDIS 寄存器的位 OU [n]可用

于控制這些輸出信號的更新。

為了保證相關通道的內部計數器在同一時鐘周期中遞增,必須在啟用全局預分頻器之前

設置內部預分頻器。如果在啟用全局預分頻器后設置內部預分頻器,則內部計數器可能以相

同的比率遞增,但在不同的時鐘周期中。

建議使用在 SAIC 模式下運行的一些 UCs 的 EMIO_FLAG_OUT 信號驅動輸出禁用輸入

信號。

當輸出禁用條件發生時,軟件中斷例程必須在服務運行SAIC通道之前為輸出通道服務。

此過程避免輸出引腳中的毛刺。 - 時基生成

對于 MC 和 OPWFM 具有內部時鐘源操作模式,可以通過配置時鐘預分頻器比來修改

內部計數器速率。圖 1.27 所示了具有等于 1 的預分頻器比的時基的示例。

注:MCB 和 OPWFMB 模式具有不同的行為。

如果預分頻器比率大于一或外部時鐘,則計數器可能以四種不同的方式中的一種,具體

取決于通道模式:

? 如果 MC 模式和在匹配開始時清除和外部時鐘源被選擇,則內部計數器的行為如圖 1.28

所示。

? 如果 MC 模式和在匹配開始時清除和內部時鐘源被選擇,則內部計數器的行為如圖 1.29

所示。

? 如果 MC 模式和在匹配結束時清除被選擇,則內部計數器的行為如圖 1.30 所示。

? 如果選擇了 OPWFM 模式,則如圖 1.29 所示的內部計數器行為。內部計數器在匹配信

號的開始時清除,跳過下一個預定時鐘邊沿,然后在后續預定時鐘邊沿中增加。

- S32K3 系列 eMIOS 配置說明

3.1 版本說明

本次配套例程使用的開發環境為:S32 Design Studio for S32 Platform 3.5。

RTD 版本為:RTD 4.0.0。

3.2 RTD 配置詳解

PWM 的 RTD 配置有兩種方式:IP 層配置和 MCAL 層配置,下面這兩種配置方式進行

講解介紹:

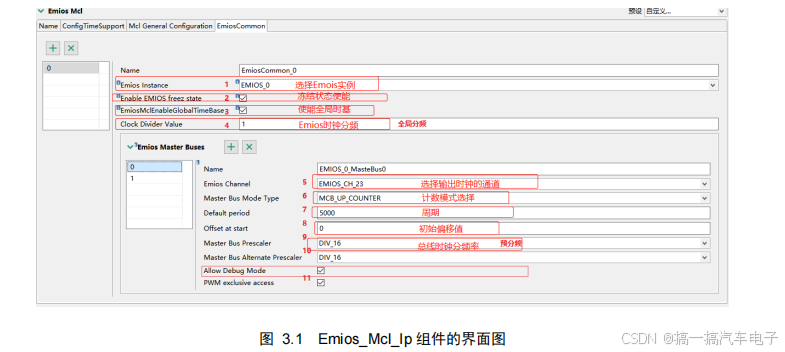

3.2.1 IP 層配置 - Emios_Mcl_Ip 組件

這個組件是控制通用的 eMIOS 和設置 eMIOS 為 MC 和 MCB 模式的組件,關于這個組

件的內容介紹如下,圖是 Emios_Mcl_Ip 組件的界面圖。

圖中 1-4 是 eMIOS 的總體參數設置,5-11 是對通道設置為 MC 和 MCB 模式進行設置,

介紹如下:

圖中 1 是選擇 eMIOS 的實例,有 EMIOS_0、EMIOS_1 和 EMIOS_2 三個可以選擇;

圖中 2 是使能 eMIOS 凍結狀態的選項;

圖中 3 是使能全局時基的選項,這是只有這個 eMIOS 組件才能進行設置的,其他組件

沒有這個選項;

圖中 4 是設置全局預分頻器;

圖中 5 是設置設置 MC 和 MCB 模式的通道

圖中 6 是設置通道的計數模式;

圖中 7 是設置通道的計數周期;

圖中 9 是設置通道預分頻器;

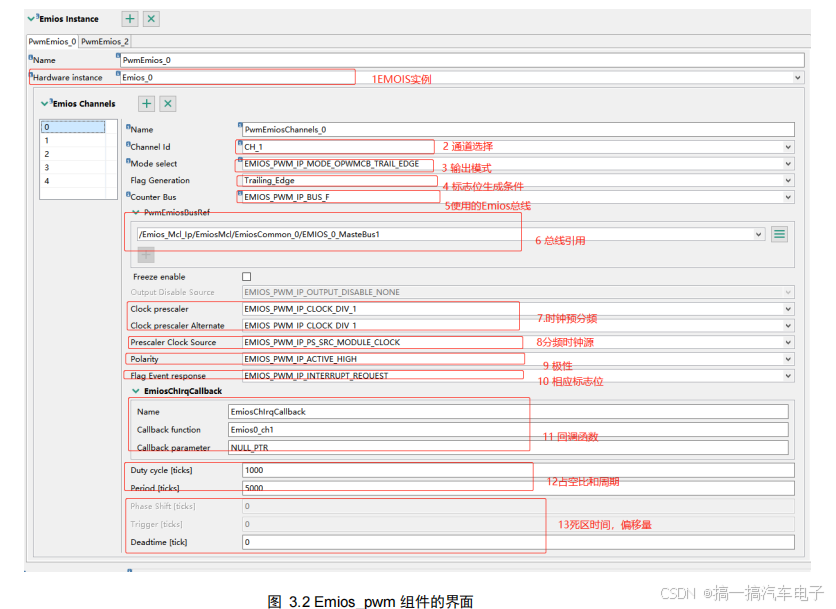

圖中 11 是對通道使能 debug 模式; - Emios_pwm_1 組件

這個組件是控制通道輸出 PWM 模式的組件,關于這個組件的內容介紹如下,圖中

Emios_pwm 組件的界面。

圖中 1 是設置 eMIOS 的通道選項;

圖中 3 是設置 PWM 的輸出模式,總共有 5 種模式可以進行選擇;

圖中 4 是選擇 Flag 生成的位置,可以選擇后邊沿觸發,也可以選擇前后邊沿都觸發;

圖中 5 是選擇計數器的總線,選擇內部總線可以不用去設置 MC 或 MCB 模式,但是選

擇其他的總線要去 Emios_Mcl_Ip 組件設置相應的通道。

圖中 6 是 MCL 模塊中配置的時鐘總線地址;

圖中 7 是設置通道時鐘分頻系數;

圖中 8 是選擇分頻的時鐘源;

圖中 9 是選擇通道的極性;

圖中 10 是選擇 Flag 事件的響應,可以無選擇無響應、中斷響應和 DMA 響應三種;

圖中 11 是設置中斷回調函數,在圖中 9 選擇中斷響應之后可以進行設置;

圖中 12 是設置占空比,周期值;

圖中 13 是分別是相移、觸發位置和死區時間的設置選項,在圖中 3 選擇不同的模式下,

就可以進行對應的設置。 - 例程程序解讀

4.1 IP 層例程:eMIOS 模塊

以 S32K344 例程為例。該例程配置了 PWM 的四種模式,分別是 OPWFMB、OPWMCB、

OPWMB 和 OPWMT 模式,其中 OPWMCB 和 OPWMT 的計數總線分別用 MC 模式通道和

MCB 模式通道作為計數總線。

eMIOS0 通道 1 和 eMIOS0 通道 6 配置為輸出 OPWMCB 模式,輸出為邊沿對齊,其中

eMIOS0 通道 1 輸出的 PWM 時鐘分頻系數設置為 1,eMIOS0 通道 6 輸出的 PWM 時鐘分頻

系數為 2;使用 PTB13 輸出 eMIOS0 通道 1 的 PWM 波形,使用 PTC10 輸出 eMIOS0 通道 6

的 PWM 波形, MC 向上向下計數模式作為計數總線

eMIOS0 通道 17 配置為輸出 OPWMB 模式,使用 PTA0 輸出 eMIOS0 通道 17 的 PWM

波形;

eMIOS0 通道 9 配置為輸出 OPWMT 模式,并設置中斷函數,使用 PTA1 輸出 eMIOS0

通道 9 的 PWM 波形;

eMIOS2 通道 0 配置為 OPWFMB 模式,不設置中斷,使用內部時鐘進行輸出 PWM 波

形,使用的是 PTD28 輸出 PWM 波形。

主函數的程序代碼如程序清單 4.1 所示。

程序清單 4.1

/* 時鐘初始化*/

Clock_Ip_Init(&Clock_Ip_aClockConfig[0]);

/* 所有 port 口初始化 /

Siul2_Port_Ip_Init(NUM_OF_CONFIGURED_PINS_PortContainer_0_BOARD_InitPeripherals,

g_pin_mux_InitConfigArr_PortContainer_0_BOARD_InitPeripherals);

/ 使能 EMIOS 中斷(建議在 RTD INT 模塊設置,減少代碼量)

- 根據 s32K3 RM 附件的中斷映射,使能 5 IRQ /

IntCtrl_Ip_Init(&IntCtrlConfig_0);

/ 初始化 EMIOS /

Emios_Mcl_Ip_Init(0, &Emios_Mcl_Ip_0_Config_BOARD_INITPERIPHERALS);

/ Emios_0 兩個 帶死區的 PWM /

Emios_Pwm_Ip_InitChannel(0, &Emios_Pwm_Ip_I0_Ch1);// PTB13 trail

Emios_Pwm_Ip_SetFlagRequest(0, EMIOS0_CH1, EMIOS_PWM_IP_INTERRUPT_REQUEST); // 設

置標志為中斷標志

Emios_Pwm_Ip_InitChannel(0, &Emios_Pwm_Ip_I0_Ch6);// PTC10 lead

//設置標志為中斷標志

Emios_Pwm_Ip_SetFlagRequest(0, EMIOS0_CH6, EMIOS_PWM_IP_INTERRUPT_REQUEST);

/ Emios_0 輸出另外 3 種 PWM*/

Emios_Pwm_Ip_InitChannel(0, &Emios_Pwm_Ip_I0_Ch3); // PTB0 DAOC

//設置標志為中斷標志

Emios_Pwm_Ip_SetFlagRequest(0 ,EMIOS0_CH3, EMIOS_PWM_IP_INTERRUPT_REQUEST);

Emios_Pwm_Ip_InitChannel(0, &Emios_Pwm_Ip_I0_Ch17);// PTA0 OPWMB

//設置標志為中斷標志

Emios_Pwm_Ip_SetFlagRequest(0, EMIOS0_CH17, EMIOS_PWM_IP_INTERRUPT_REQUEST);

Emios_Pwm_Ip_InitChannel(0, &Emios_Pwm_Ip_I0_Ch9); // PTA1 OPWMT

//設置標志為中斷標志

Emios_Pwm_Ip_SetFlagRequest(0, EMIOS0_CH9, EMIOS_PWM_IP_INTERRUPT_REQUEST);

/* Emios_3 一個 PWM - OPWFM 生成一個簡單單通道 PWM /

Emios_Pwm_Ip_InitChannel(2, &Emios_Pwm_Ip_I2_Ch0);// PTD23 OPWFMB

/ 回調函數如下 /

/ 設置trail 死區時間 */

void Emios0_ch1(void p)

{

uint8 time = 0;

(void)p;

time = Emios_Pwm_Ip_GetDeadTime(0,EMIOS0_CH1);

if(Emios_Pwm_Ip_GetDeadTime(0,EMIOS0_CH1) == 500)

{

Emios_Pwm_Ip_SetDeadTime(0,EMIOS0_CH1,100);

}

else

Emios_Pwm_Ip_SetDeadTime(0,EMIOS0_CH1,500);

}

/ 設置lead死區時間 */

void Emios0_ch6(void p)

{

uint8 time = 0;

(void)p;

time = Emios_Pwm_Ip_GetDeadTime(0,EMIOS0_CH6);

if(Emios_Pwm_Ip_GetDeadTime(0,EMIOS0_CH6) == 500)

{

Emios_Pwm_Ip_SetDeadTime(0,EMIOS0_CH6,100);

}

else

Emios_Pwm_Ip_SetDeadTime(0,EMIOS0_CH6,500);

}

/ 新配置 */

void Emios0_ch3(void p)

{

(void)p;

/ 設置新周期等 /

Emios_Pwm_Ip_SetDutyCycle(0,EMIOS0_CH3,3000);

}

/ 設置觸發值 */

void Emios0_ch9(void p)

{

uint8 partmemt = 0;

(void)p;

/ 查看觸發值 /

partmemt = Emios_Pwm_Ip_GetTriggerPlacement(0,EMIOS0_CH9);

}

/ 重新配置 */

void Emios0_ch17(void p)

{

(void)p;

/ 設置新周期 */

Emios_Pwm_Ip_SetDutyCycle(0,EMIOS0_CH17,2000);

}

詳解:動態內容與 SEO 的完美結合)

算法)

![[特殊字符] GitHub 熱門開源項目速覽(2025/09/09)](http://pic.xiahunao.cn/[特殊字符] GitHub 熱門開源項目速覽(2025/09/09))

)

)

![[玩轉GoLang] 5分鐘整合Gin / Gorm框架入門](http://pic.xiahunao.cn/[玩轉GoLang] 5分鐘整合Gin / Gorm框架入門)