們先來回想一件事,根據歐姆定律,阻抗是不是越低越好? 代表即使有很大的瞬時電流,瞬間的電壓降也不會超過某個極限!

理論上是! 可是這其實忽略了兩個關鍵的要素:

- PDN阻抗有諧振:諧振代表能量的快速轉換,即便這個諧振是屬于往下掉的串聯諧振,還是有可能引發能量的高度震蕩

- 電源波形有頻率成分:如果電源波形的頻率剛好跟諧振頻率對齊,那會引發PDN網絡有劇烈的噪聲震蕩

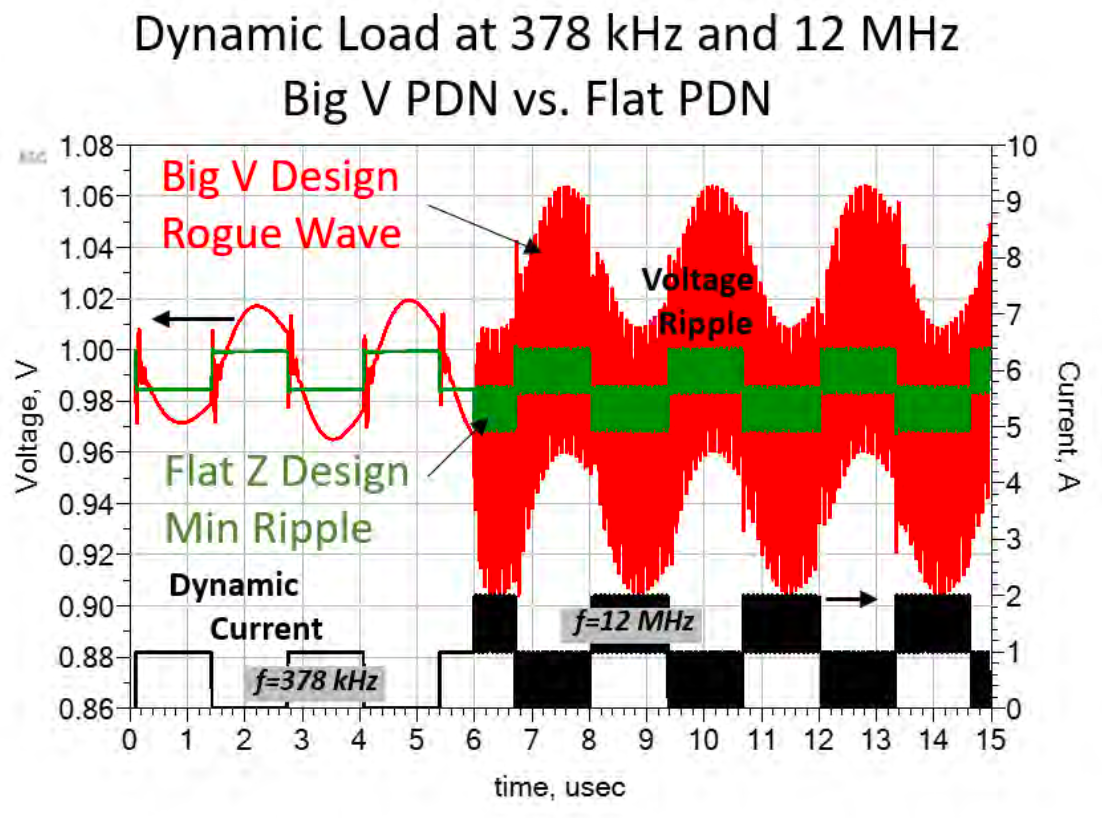

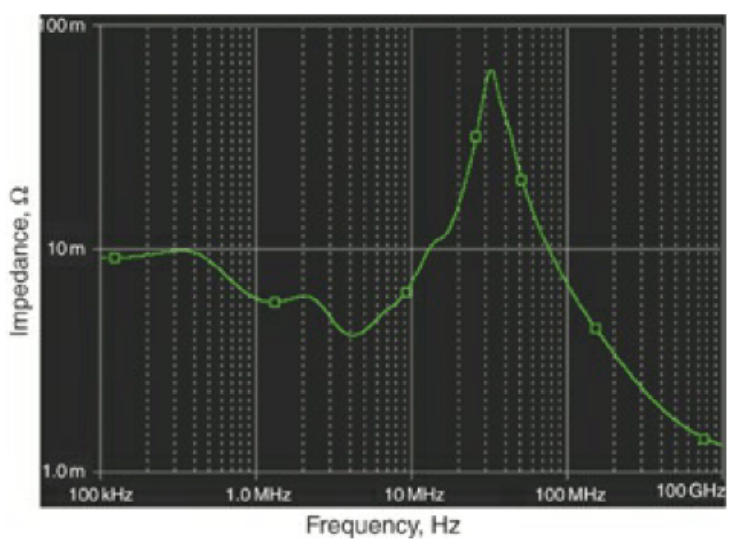

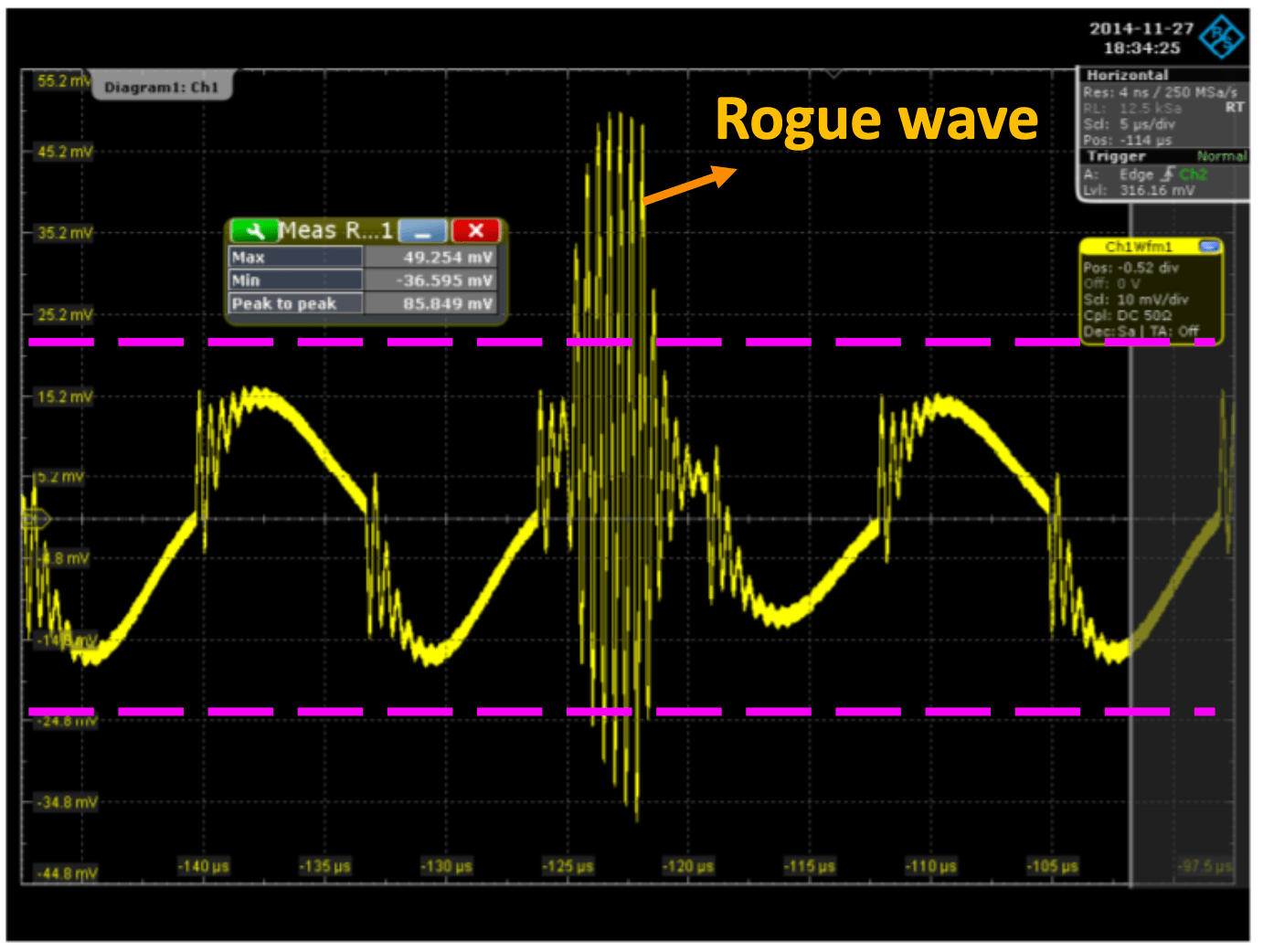

就如同下面這個案例所示,我們可以觀察到一個非常明顯的現象:一個串聯諧振確實將整體阻抗往下拉,乍看之下這似乎是個大多數設計者希望達到的的狀態,開心地很。 然而,當我們進一步測試并輸入一個步階響應(Step Response)作為電流源抽載后,結果令人意外,我們發現電壓產生了極為劇烈的震蕩現象。 在這個特定案例中,震蕩幅度高達100mV,雖然這個數值可能是比較夸張的例子,但它確實揭示了一個關鍵問題:這樣的結果是否已經徹底顛覆了“阻抗越低越好”這個在PI領域中普遍被接受的設計認知? 這個現象值得我們深入思考,重新審視我們對PDN設計的基本假設。

?

?

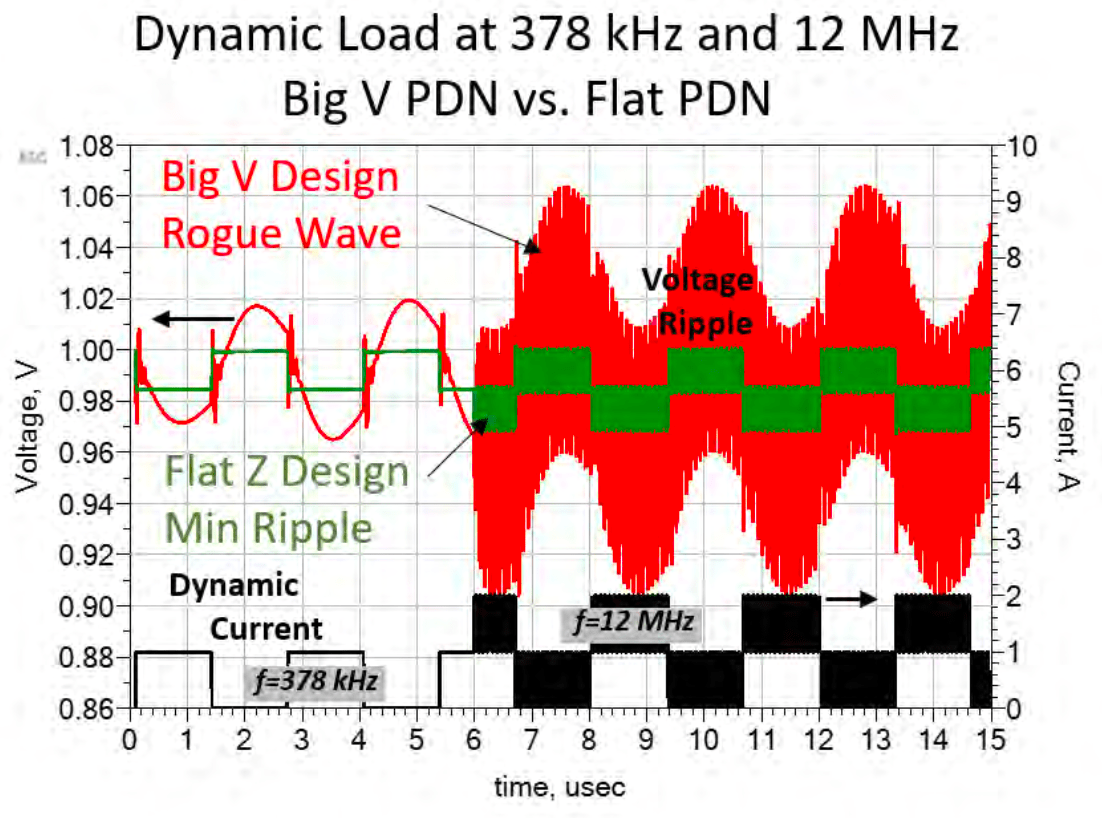

或是如果有在100MHz這個區域甚至更高的頻率有超過Target impedance的反諧振點,就很有可能引發所謂Rogue Wave的大海嘯,電壓波形會開始唱世界名曲,炸裂...

?

?

震蕩的萬惡起源 – 諧振

諧振(Resonance)是一種物理現象,指一個物理系統在受到周期性外部激勵時,若外部激勵的頻率與該系統的自然頻率(Natural Frequency)相匹配或非常接近,系統將會產生極其劇烈的響應,例如振幅的急劇增大 。 此一特定頻率被稱為諧振頻率(Resonant Frequency)。

以上這段是我問AI的,基本上大自然間各種結構都存在著諧振,也就是在這個頻率點被激發后,能量會大量爆發出來,產生噪聲、干擾,影響可以很巨大!

在電路板中,這些諧振大多數由寄生電容與寄生電感造成,電容是儲存電能的元器件,電感則是用來儲存磁能,當這兩者在某一頻率產生諧振時,電容的電能會轉換成磁能丟給電感,電感的磁能則會轉化成電能丟給電容,如果有人在這個頻率點打破這個交換的平衡,則會引爆巨大的能量。

在PI領域中,諧振我們又可以將其分成這兩種:

- 串聯諧振

- 并聯諧振

有何差異呢?

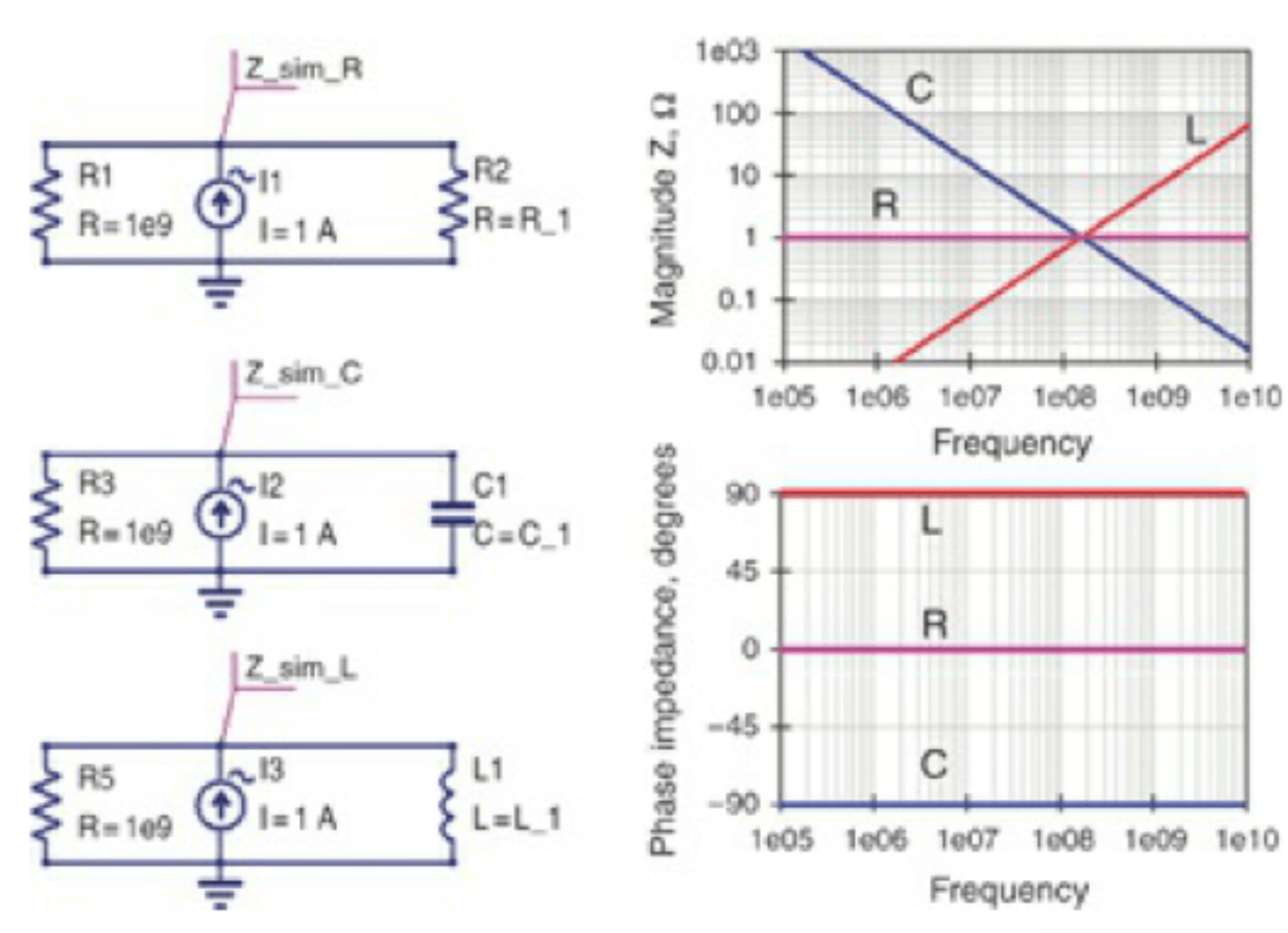

電容與電感

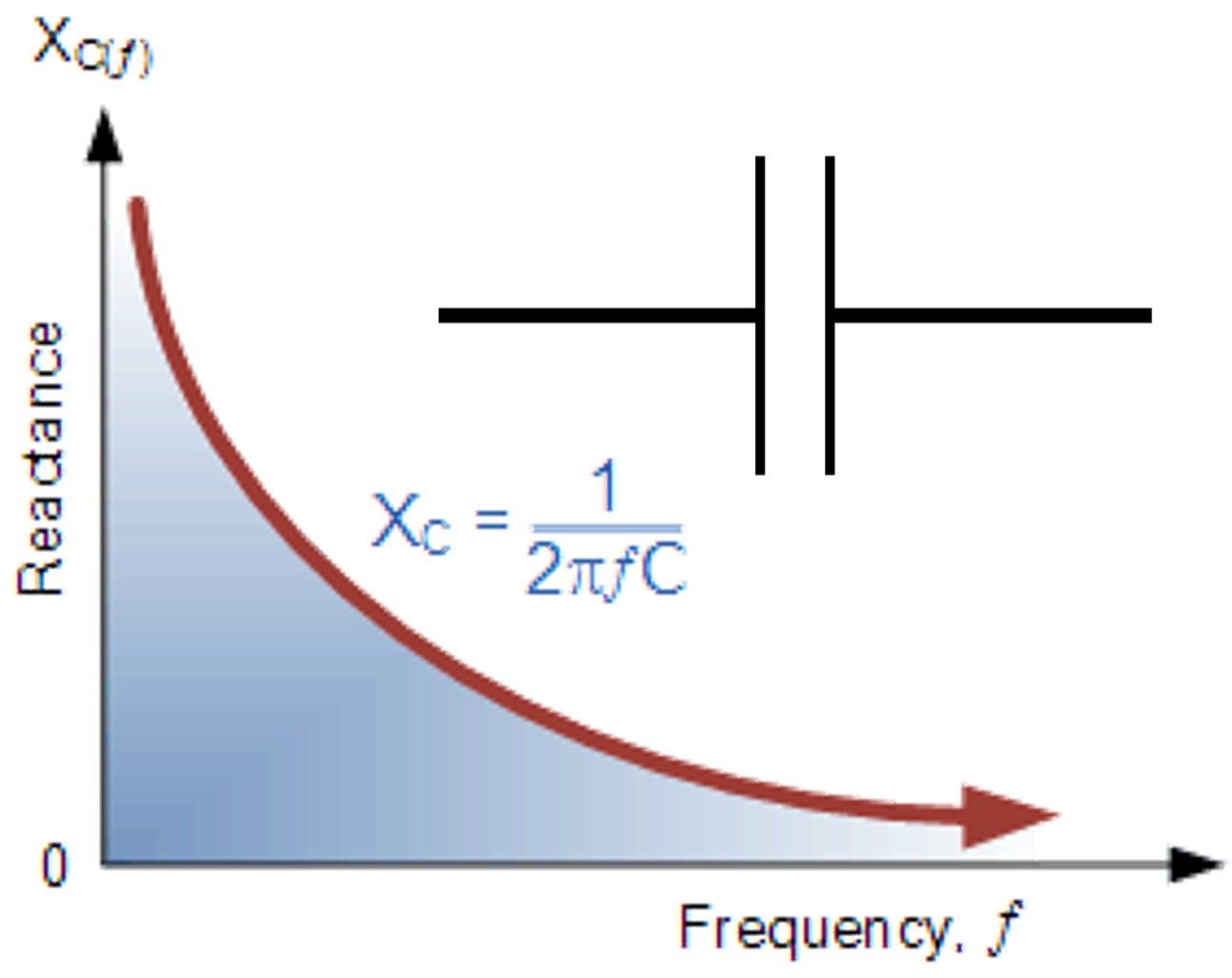

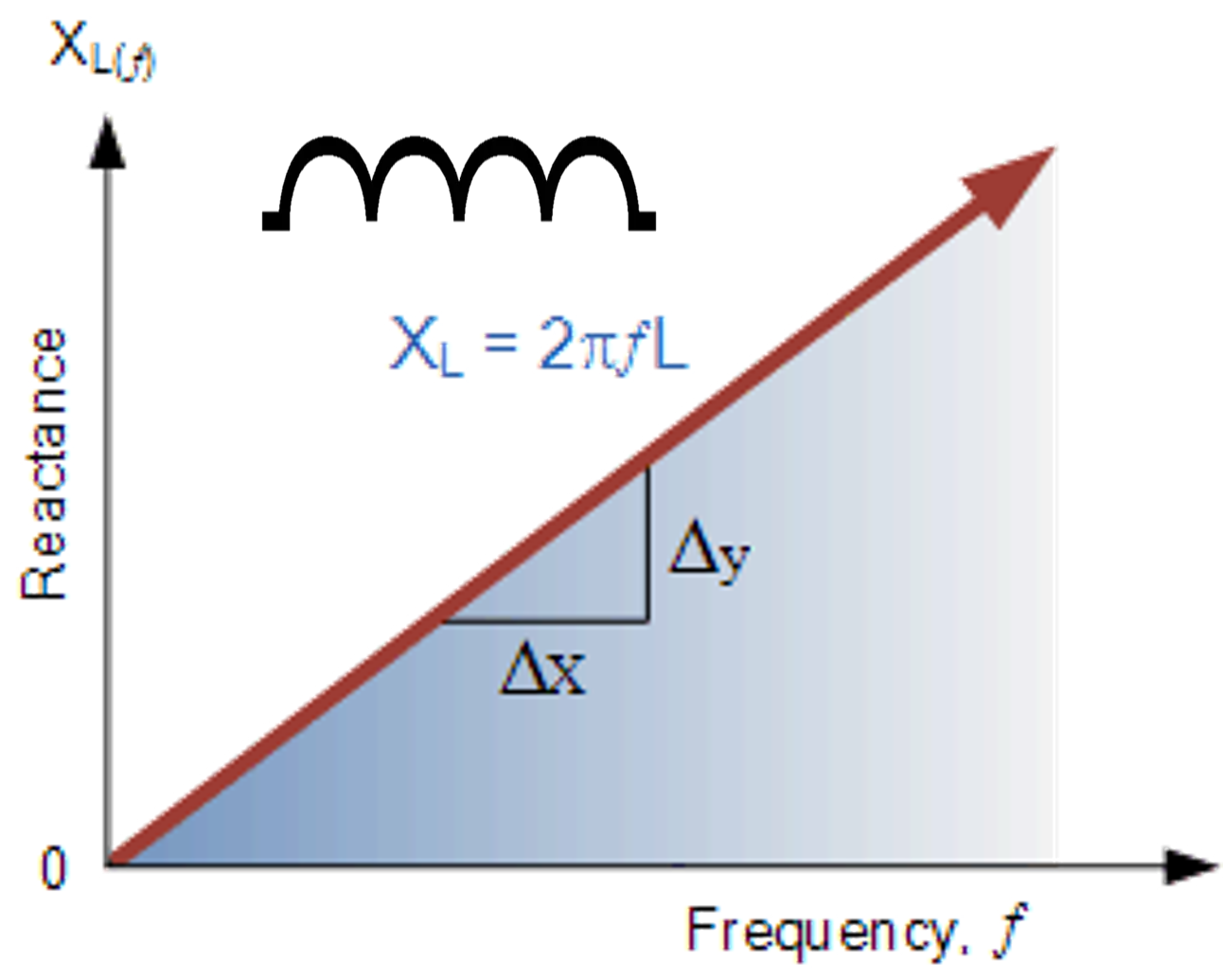

首先,我們先來看電容與電感這兩個基本元器件的阻抗隨頻率變化的關系。

電容的阻抗隨頻率變高會降低,而電感的阻抗會隨著頻率變高而變大。

?

?

?

這邊說的是理想的電容與電感,如果是現實中我們在使用的電容器件如MLCC(Multi-Layered Ceramic Capacitor)、Film Capacitor、Polymer等等; 而電感器件,像是Choke或是Ferrite bead等等都會有寄生的雜散效應,所以阻抗曲線就不是完全符合這條曲線。

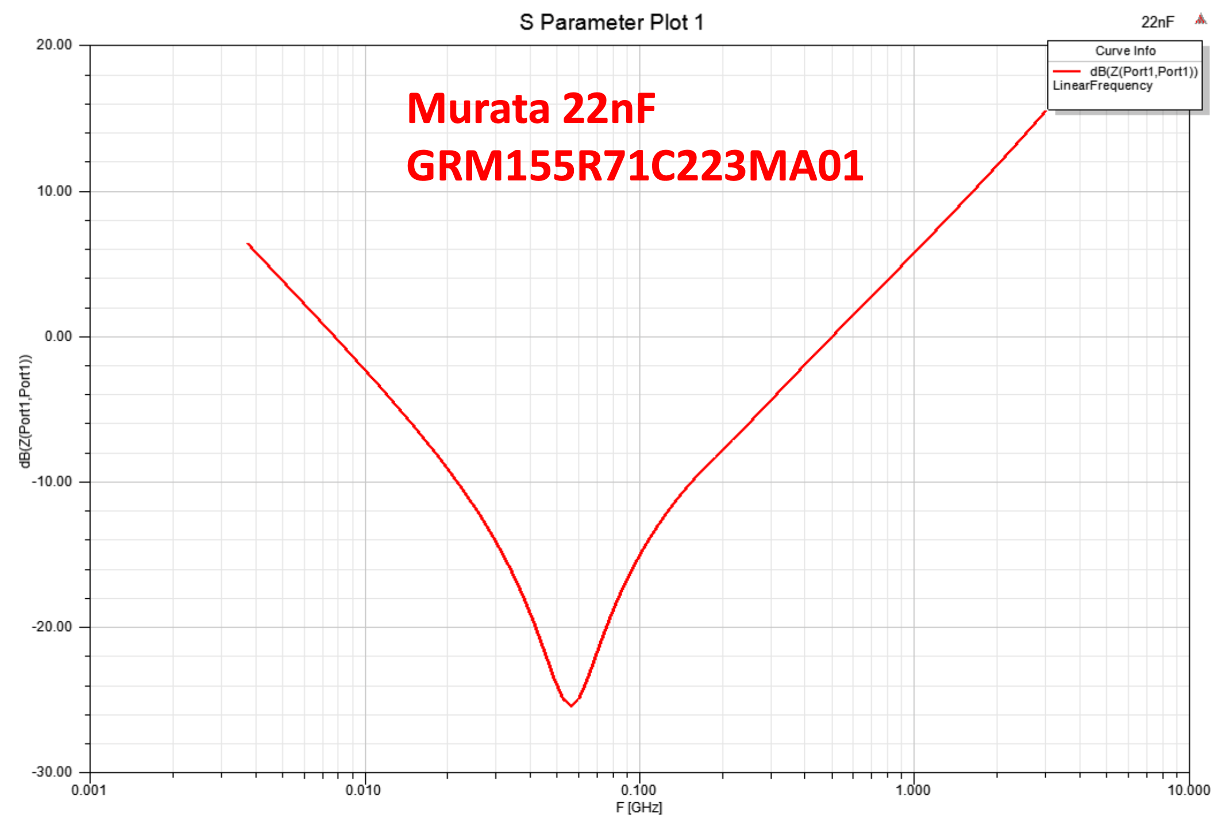

像是這顆Murata的22nF電容,就會有串聯諧振點,過了這個諧振點,電容器件就會轉換成電感特性,也就是說... 電容某種程度上其實可以當做電感用... 只是... 麥阿捏啦!

?

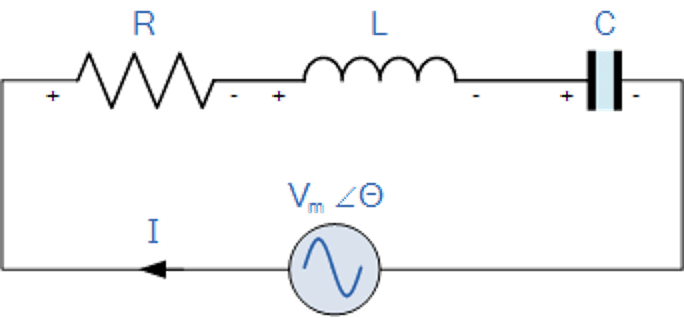

串聯諧振(Series Resonance)

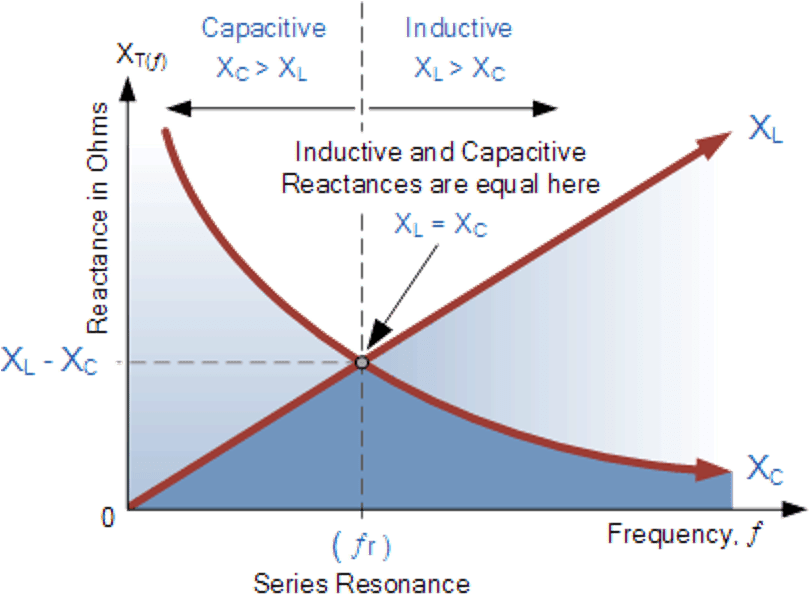

各位可以先記得,諧振產生的頻率點,就是電容抗跟電感抗兩者相交叉的那個點。

也就是電感抗=電容抗:

XL=XCXL?=XC?

而一個RLC串聯電路的系統阻抗可以寫成:

?

ZRLC=RDC+ZL+ZCZRLC?=RDC?+ZL?+ZC?

在諧振點時,電路的總電抗為0(XL=-XC),代表整個電路只剩下RDC。 對,沒錯,電感跟電容在諧振頻率上會消失。

基本邏輯是這樣,在串聯電路上低頻的表現由開路電路來主導,而電容低頻屬于高阻抗(開路Open),所以可以看到低頻時阻抗曲線在左上角。 而隨著頻率越來越高,電容抗會下降,電感抗會跑出來,兩條曲線會交叉在一起,這個就是諧振頻,這是整個電路剩下電阻。 再往更高頻走,電容阻抗持續下降,電感阻抗繼續攀升,就會變成整個阻抗曲線像個V字型!

?

串聯諧振會有V字體的阻抗曲線:

?

這個頻率點可以通過以下公式計算:

f=12πLCf=2πLC?1?

也就是說,當電感與電容越大,諧振頻就越低; 反之,這兩者變小時,諧振頻就越高。

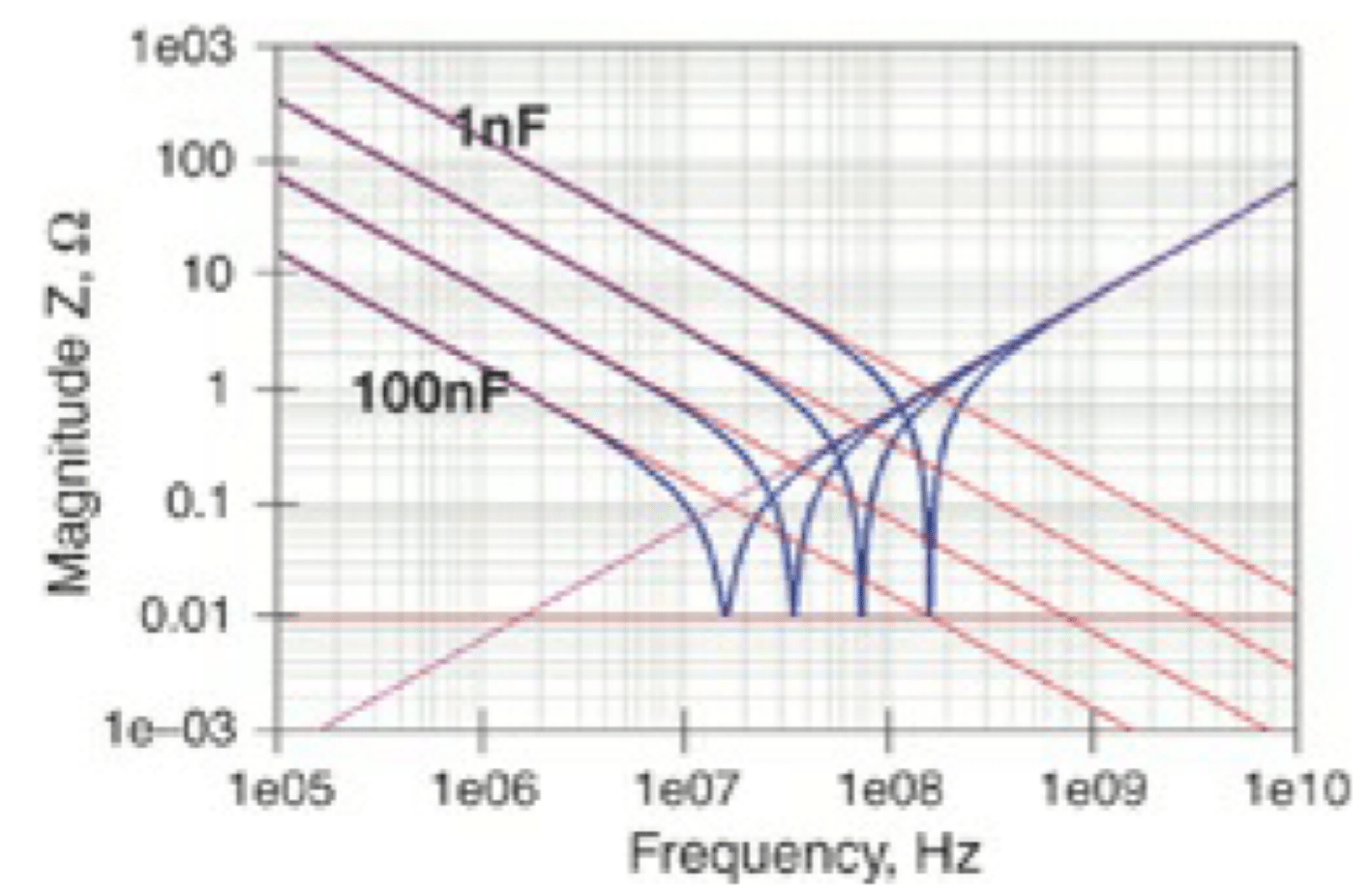

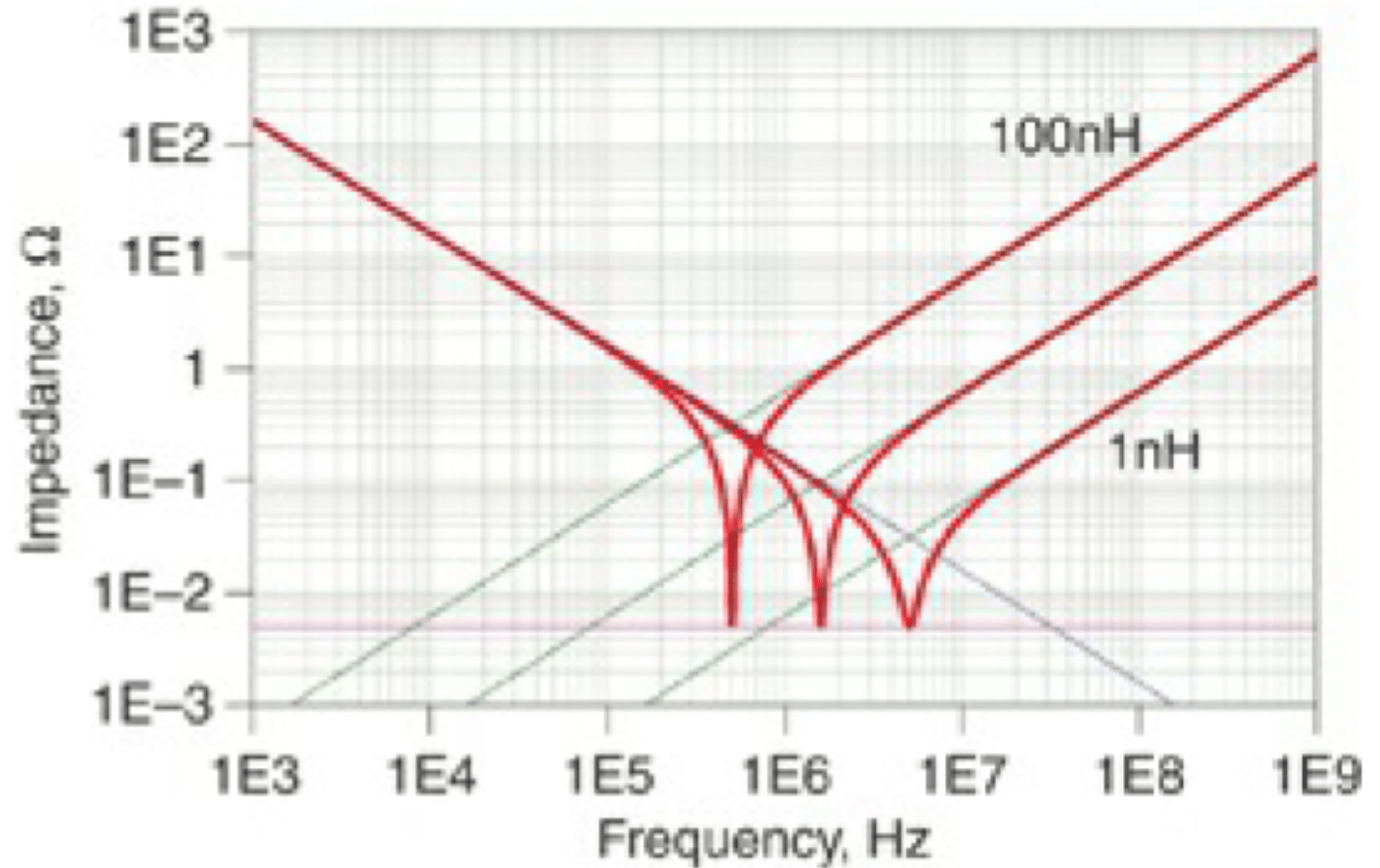

我們可以藉由調整電容與電感來看阻抗曲線的變化,當電容變大時(1nF → 100nF),低頻阻抗變小,諧振頻跑到低頻,高頻阻抗不變。

?

而當電感變大時(1nH → 100nH),低頻阻抗不變,高頻阻抗變大,諧振頻往低頻跑。

?

通常這種諧振的代表就是電容器,因為可以串聯諧振可以拉低整個電源阻抗,所以我們才會使用MLCC這類型的電容來解決阻抗問題。

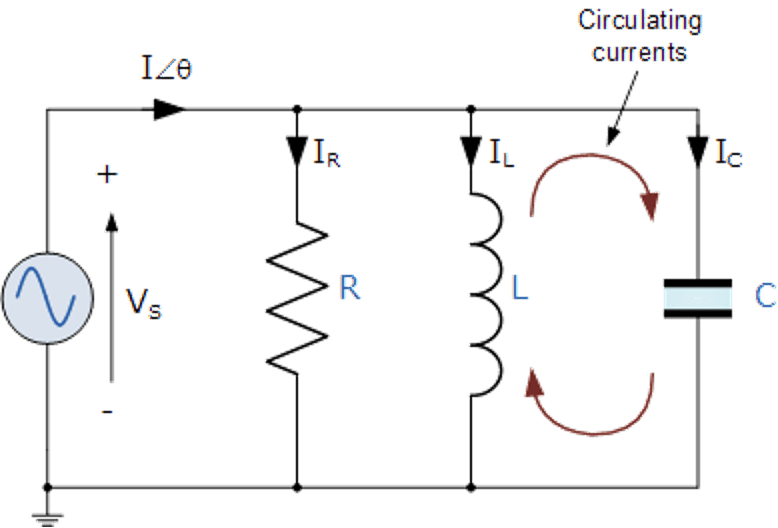

并聯諧振(Parallel Resonance)

當RLC并聯時,電路可以畫成:

?

系統阻抗可以用導納Y表示:

Y=1R+1jwL+jwCY=R1?+jwL1?+jwC

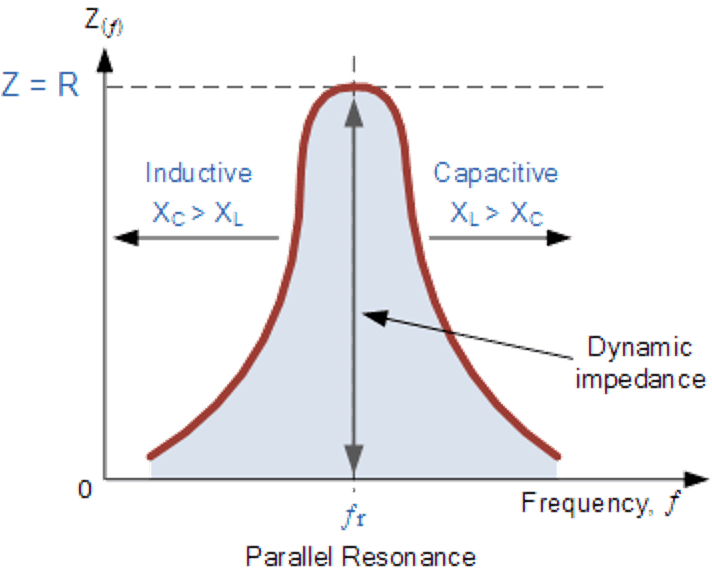

低頻的阻抗由電感主導,阻抗隨著頻率變大而增加; 當電容抗與電感抗相同時,這個頻率點為諧振點,為高阻抗。 在更高頻,阻抗又再度被電容在高頻時的低阻抗給拉下來,呈現一個倒V字型:

?

諧振頻率點的計算與串聯諧振相同:

f=12πLCf=2πLC?1?

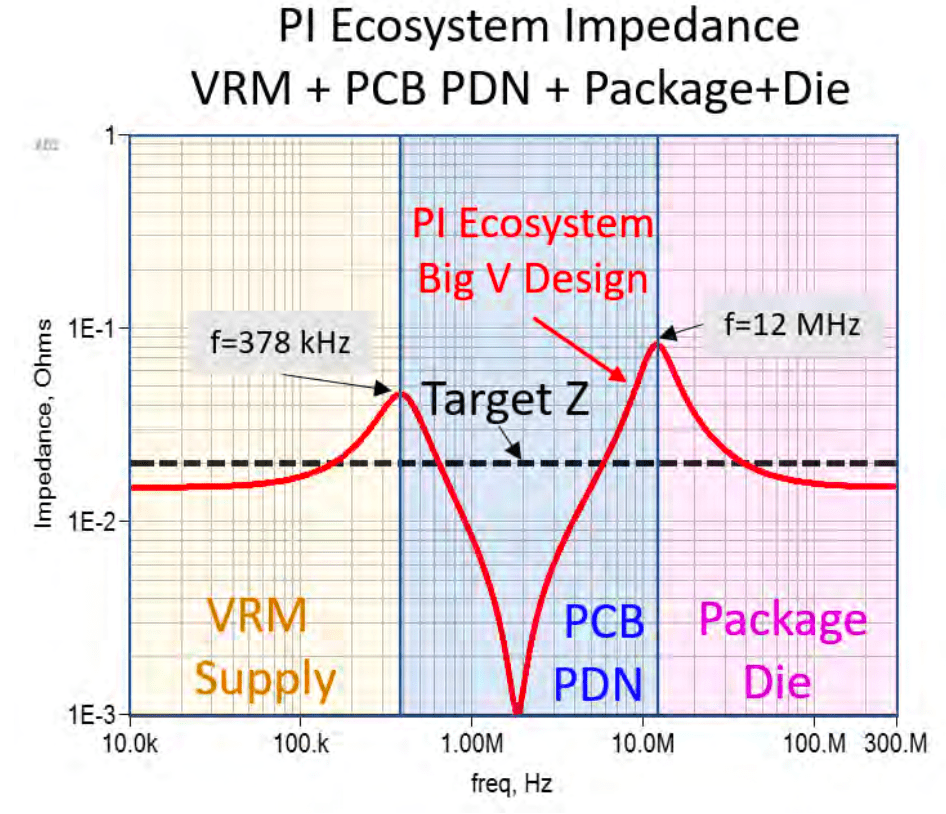

這類型的阻抗,通常發生在兩個對象交接處,例如:

- VRM與PCB MLCC合成的效應

- Package與Silicon Die合成時的結果

尤其是Package與Silicon Die,由于這個阻抗會發生在較高頻處,通常伴隨而來的Noise ripple也會特別大。

可以看到在378KHz與12MHz都有并聯高阻抗諧振,12MHz的電流源造成的Ripple會異常地大。

?

?

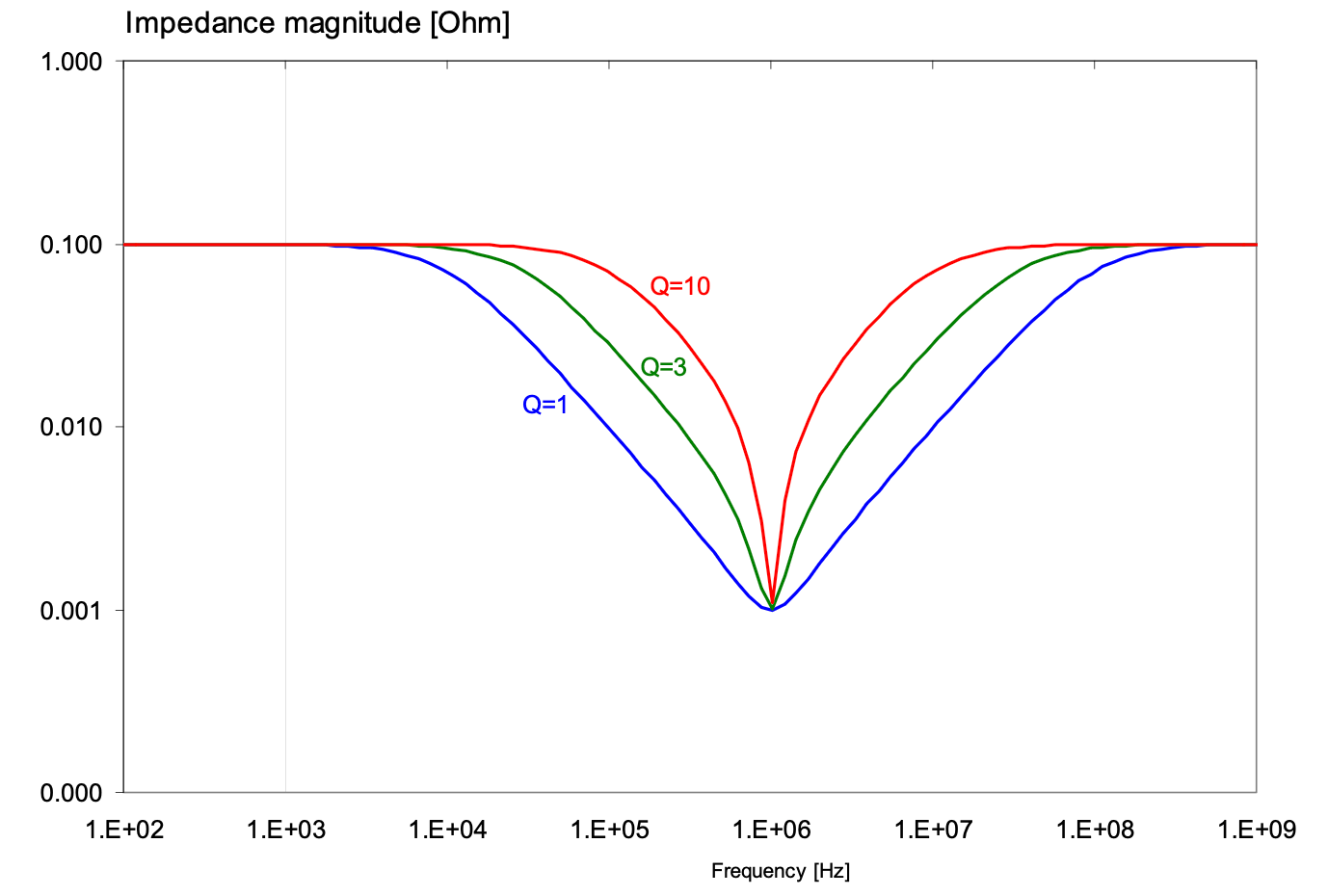

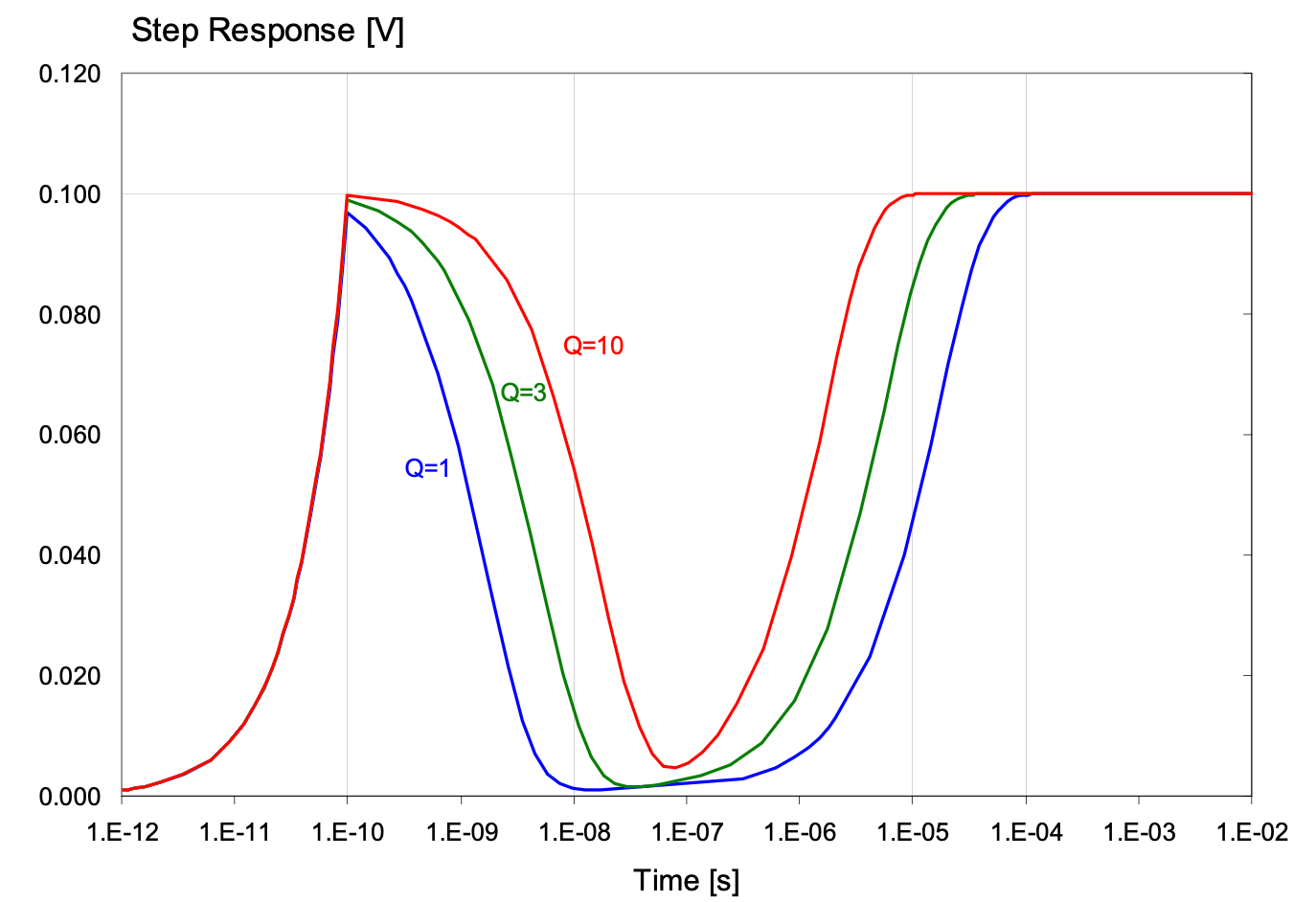

質量因素 Q-Factor

講到諧振就一定要講到Q值。

Q值的最根本定義是,在一個振盪周期內,諧振器中儲存的總能量與其消耗的能量之比,再乘以2π。 其數學表達式有兩種,第一種是原始定義:

Q=2πEstoredEdissipated/cycleQ=2πEdissipated/cycle?Estored??

第二種則是透過諧振頻率與3dB帶寬的比值:

Q=frBWQ=BWfr??

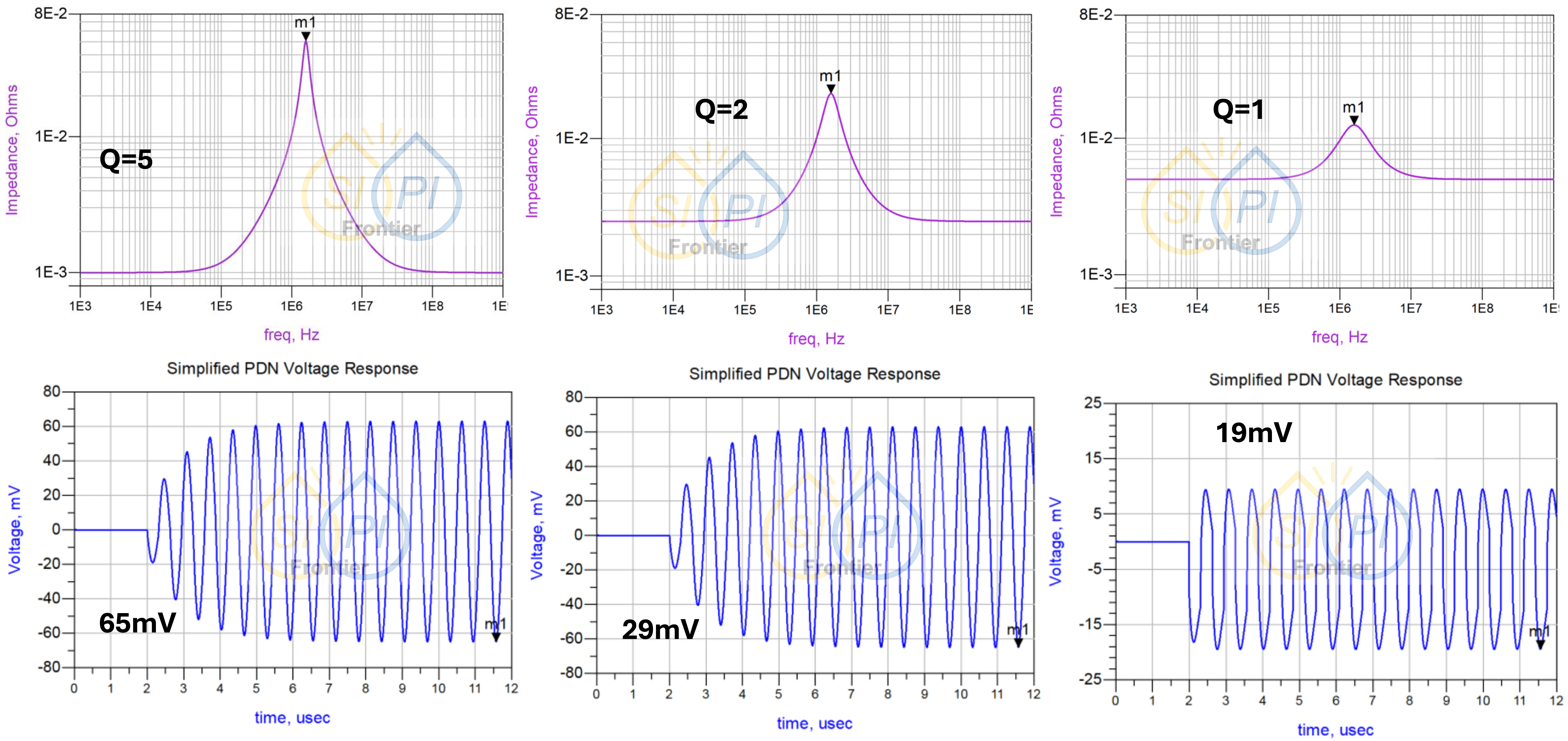

從這個定義可以看出,高Q值意味著諧振器是一個高效的、低損耗的能量儲存系統。 But… 對于PI而言不是一個好系統... 因為對于PI而言,我們要的是一個就算有個電流源的頻率剛好打到諧振頻率,就算真的有一個可能性的電壓震蕩,這個震蕩的能量也可以被迅速消散。 對于高Q值電路而言,阻抗峰值高且尖銳,能量儲存較大,沒有足夠的電阻可以消散能量,一被激發就難以收拾。

所以我們會希望PI設計者可以盡量朝低Q值電路去做設計,代表電阻較大,吃掉這些可能爆發的能量!

從這些結果可以看出,Q值越低,Ripple越小,代表PI設計更好!

?

?

?

)

的花店系統)

?)

)