目錄

- 1、前言

- 工程概述

- 免責聲明

- 2、相關方案推薦

- 我已有的所有工程源碼總目錄----方便你快速找到自己喜歡的項目

- 國產安路FPGA相關方案推薦

- 3、設計思路框架

- 工程設計原理框圖

- 輸入Sensor之-->GC0308攝像頭

- 輸入Sensor之-->OV7725攝像頭

- 輸入Sensor之-->OV5640攝像頭

- 輸入Sensor之-->AR0135攝像頭

- 輸入Sensor之-->ADV7611芯片解碼的HDMI

- FDMA圖像緩存

- HDMI視頻輸出架構

- 工程源碼架構

- 4、TD工程源碼1詳解:GC0308輸入版本

- 5、TD工程源碼2詳解:OV7725輸入版本

- 6、TD工程源碼3詳解:OV5640輸入版本

- 7、TD工程源碼4詳解:AR0135輸入版本

- 8、TD工程源碼5詳解:HDMI輸入版本

- 9、上板調試驗證并演示

- 準備工作

- 國產安路FPGA視頻采集效果演示

- 10、工程源碼

國產安路FPGA實現圖像視頻采集轉HDMI輸出,提供5套TD工程源碼和技術支持

1、前言

國產FPGA現狀:

“茍利國家生死以,豈因禍福避趨之!”大洋彼岸的我優秀地下檔員,敏銳地洞察到祖國的短板在于先進制程半導體的制造領域,于是本著為中華民族偉大復興的中國夢貢獻綿薄之力的初心,懂先生站在高略高度和長遠角度謀劃,寧愿背當代一世之罵名也要為祖國千秋萬世謀,2018年7月,懂先生正式打響毛衣戰,隨后又使出恰勃紙戰術,旨在為祖國先進制程半導體領域做出自主可控的戰略推動;2019年初我剛出道時,還是Xilinx遙遙領先的時代(現在貌似也是),那時的國產FPGA還處于黑鐵段位;然而才短短7年,如今的國產FPGA屬于百家爭鳴、百花齊放、八仙過海、神仙打架、方興未艾、得隴望蜀、友商都是XX的喜極而泣之局面,此情此景,不得不吟唱老人家的詩句:魏武揮鞭,東臨碣石有遺篇,蕭瑟秋風今又是,換了人間。。。

目前對于國產FPGA優勢有以下幾點:

1:性價比高,與同級別國外大廠芯片相比,價格相差幾倍甚至十幾倍;

2:自主可控,國產FPGA擁有完整自主知識產權的產業鏈,從芯片到相關EDA工具;

3:響應迅速,FAE技術支持比較到位,及時解決開發過程中遇到的問題,畢竟中文數據手冊;

4:采購方便,產業鏈自主可控,采購便捷;

工程概述

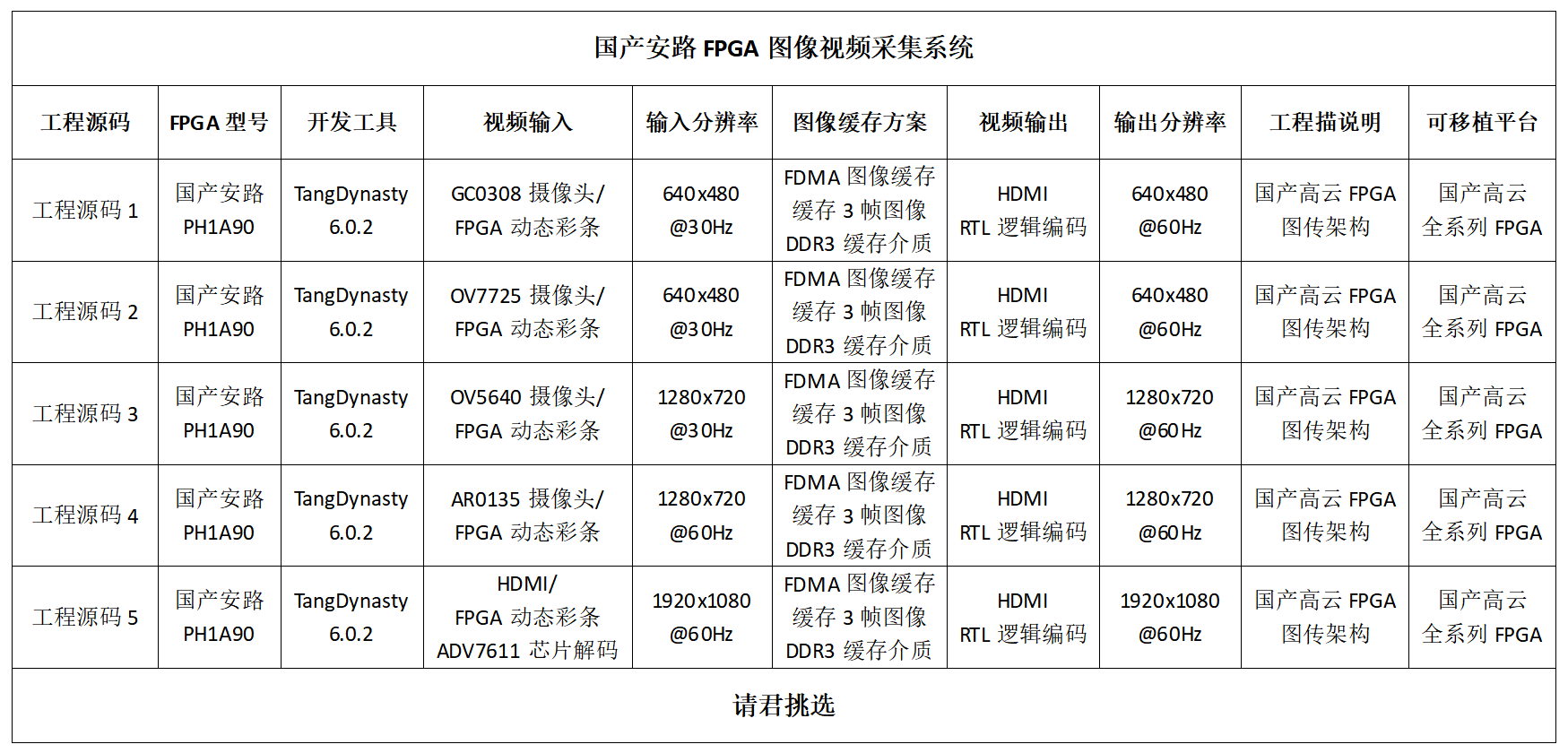

本文使用國產安路的PH1系列FPGA做基礎的圖像視頻采集系統;視頻輸入源有多種,一種是板載的HDMI輸入接口,另一種是傳統攝像頭,包括OV7725、OV5640和AR0135;如果你的FPGA開發板沒有視頻輸入接口,或者你的手里沒有攝像頭時,可以使用FPGA邏輯實現的動態彩條模擬輸入視頻,代碼里通過parametr參數選擇視頻源,默認不使用動態彩條;FPGA首先對攝像頭進行i2c初始化配置,然后采集攝像頭視頻;然后視頻送入本博主常用的FDMA圖像緩存架構實現視頻3幀緩存功能,本設計使用DDR3作為緩存介質;然后Native視頻時序控制圖像緩存架構從DDR3中讀取視頻,并做Native視頻時序同步,輸出RGB888視頻;然后視頻送入安路官方提供的RGB轉HDMI IP實現RGB轉HDMI功能;最后視頻通過板載HDMI輸出接口送顯示器顯示即可;針對市場主流需求,本設計提供5套PDS工程源碼,具體如下:

現對上述3套工程源碼做如下解釋,方便讀者理解:

工程源碼1

開發板FPGA型號為國產安路–PH1A90SBG484-3;輸入視頻為GC0308攝像頭或者動態彩條,默認使用GC0308;FPGA首先使用純Verilog實現的i2c總線對攝像頭進行初始化配置,分辨率配置為640x480@30Hz;然后采集輸入視頻,將輸入的兩個時鐘傳輸一個RGB565像素的視頻采集為一個時鐘傳輸一個RGB888像素的視頻;然后視頻送入本博主常用的FDMA圖像緩存架構實現視頻3幀緩存功能,本設計使用DDR3作為緩存介質;然后Native視頻時序控制圖像緩存架構從DDR3中讀取視頻,并做Native視頻時序同步,輸出RGB888視頻,輸出分辨率為640x480@60Hz,然后視頻送入安路官方提供的RGB轉HDMI IP實現RGB轉HDMI功能;最后視頻通過板載HDMI輸出接口送顯示器顯示即可;該工程適用于國產安路FPGA實現圖像視頻采集系統應用;

工程源碼2

開發板FPGA型號為國產安路–PH1A90SBG484-3;輸入視頻為OV7725攝像頭或者動態彩條,默認使用OV7725;FPGA首先使用純Verilog實現的i2c總線對攝像頭進行初始化配置,分辨率配置為640x480@30Hz;然后采集輸入視頻,將輸入的兩個時鐘傳輸一個RGB565像素的視頻采集為一個時鐘傳輸一個RGB888像素的視頻;然后視頻送入本博主常用的FDMA圖像緩存架構實現視頻3幀緩存功能,本設計使用DDR3作為緩存介質;然后Native視頻時序控制圖像緩存架構從DDR3中讀取視頻,并做Native視頻時序同步,輸出RGB888視頻,輸出分辨率為640x480@60Hz,然后視頻送入安路官方提供的RGB轉HDMI IP實現RGB轉HDMI功能;最后視頻通過板載HDMI輸出接口送顯示器顯示即可;該工程適用于國產安路FPGA實現圖像視頻采集系統應用;

工程源碼3

開發板FPGA型號為國產安路–PH1A90SBG484-3;輸入視頻為OV5640攝像頭或者動態彩條,默認使用OV5640;FPGA首先使用純Verilog實現的i2c總線對攝像頭進行初始化配置,分辨率配置為1280x720@30Hz;然后采集輸入視頻,將輸入的兩個時鐘傳輸一個RGB565像素的視頻采集為一個時鐘傳輸一個RGB888像素的視頻;然后視頻送入本博主常用的FDMA圖像緩存架構實現視頻3幀緩存功能,本設計使用DDR3作為緩存介質;然后Native視頻時序控制圖像緩存架構從DDR3中讀取視頻,并做Native視頻時序同步,輸出RGB888視頻,輸出分辨率為1280x720@60Hz,然后視頻送入安路官方提供的RGB轉HDMI IP實現RGB轉HDMI功能;最后視頻通過板載HDMI輸出接口送顯示器顯示即可;該工程適用于國產安路FPGA實現圖像視頻采集系統應用;

工程源碼4

開發板FPGA型號為國產安路–PH1A90SBG484-3;輸入視頻為AR0135全局曝光工業相機或者動態彩條,默認使用AR0135;FPGA首先使用純Verilog實現的i2c總線對攝像頭進行初始化配置,分辨率配置為1280x720@60Hz;然后采集輸入視頻,將輸入的兩個時鐘傳輸一個RGB565像素的視頻采集為一個時鐘傳輸一個RGB888像素的視頻;然后視頻送入本博主常用的FDMA圖像緩存架構實現視頻3幀緩存功能,本設計使用DDR3作為緩存介質;然后Native視頻時序控制圖像緩存架構從DDR3中讀取視頻,并做Native視頻時序同步,輸出RGB888視頻,輸出分辨率為1280x720@60Hz,然后視頻送入安路官方提供的RGB轉HDMI IP實現RGB轉HDMI功能;最后視頻通過板載HDMI輸出接口送顯示器顯示即可;該工程適用于國產安路FPGA實現圖像視頻采集系統應用;

工程源碼5

開發板FPGA型號為國產安路–PH1A90SBG484-3;輸入視頻為HDMI視頻,用筆記本電腦模擬,筆記本電腦通過HDMI線連接FPGA開發板的HDMI輸入接口,板載的ADV7611芯片實現HDMI視頻解碼,FPGA使用純Verilog實現的i2c總線對ADV7611進行初始化配置,分辨率配置為1920x1080@60Hz,輸出RGB888視頻給FPGA;然后視頻送入本博主常用的FDMA圖像緩存架構實現視頻3幀緩存功能,本設計使用DDR3作為緩存介質;然后Native視頻時序控制圖像緩存架構從DDR3中讀取視頻,并做Native視頻時序同步,輸出RGB888視頻,輸出分辨率為1920x1080@60Hz,然后視頻送入安路官方提供的RGB轉HDMI IP實現RGB轉HDMI功能;最后視頻通過板載HDMI輸出接口送顯示器顯示即可;該工程適用于國產安路FPGA實現圖像視頻采集系統應用;

本博客描述了國產安路FPGA實現圖像視頻采集系統的設計方案,工程代碼可綜合編譯上板調試,可直接項目移植,適用于在校學生、研究生項目開發,也適用于在職工程師做學習提升,可應用于醫療、軍工等行業的高速接口或圖像處理領域;

提供完整的、跑通的工程源碼和技術支持;

工程源碼和技術支持的獲取方式放在了文章末尾,請耐心看到最后;

免責聲明

本工程及其源碼即有自己寫的一部分,也有網絡公開渠道獲取的一部分(包括CSDN、Xilinx官網、Altera官網等等),若大佬們覺得有所冒犯,請私信批評教育;基于此,本工程及其源碼僅限于讀者或粉絲個人學習和研究,禁止用于商業用途,若由于讀者或粉絲自身原因用于商業用途所導致的法律問題,與本博客及博主無關,請謹慎使用。。。

2、相關方案推薦

我已有的所有工程源碼總目錄----方便你快速找到自己喜歡的項目

其實一直有朋友反饋,說我的博客文章太多了,亂花漸欲迷人,自己看得一頭霧水,不方便快速定位找到自己想要的項目,所以本博文置頂,列出我目前已有的所有項目,并給出總目錄,每個項目的文章鏈接,當然,本博文實時更新。。。以下是博客地址:

點擊直接前往

國產安路FPGA相關方案推薦

鑒于國產FPGA的優異表現和市場需求,我專門開設了一個人國產安路FPGA專欄,里面收錄了基于國產安路FPGA的圖像處理、UDP網絡通信、GT高速接口、PCIE等博客,感興趣的可以去看看,博客地址:

點擊直接前往

3、設計思路框架

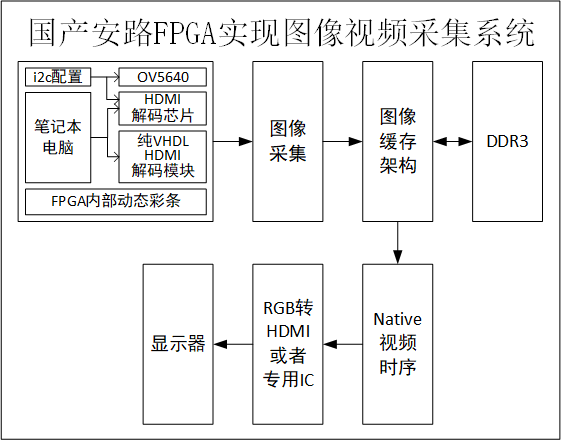

工程設計原理框圖

工程設計原理框圖如下:

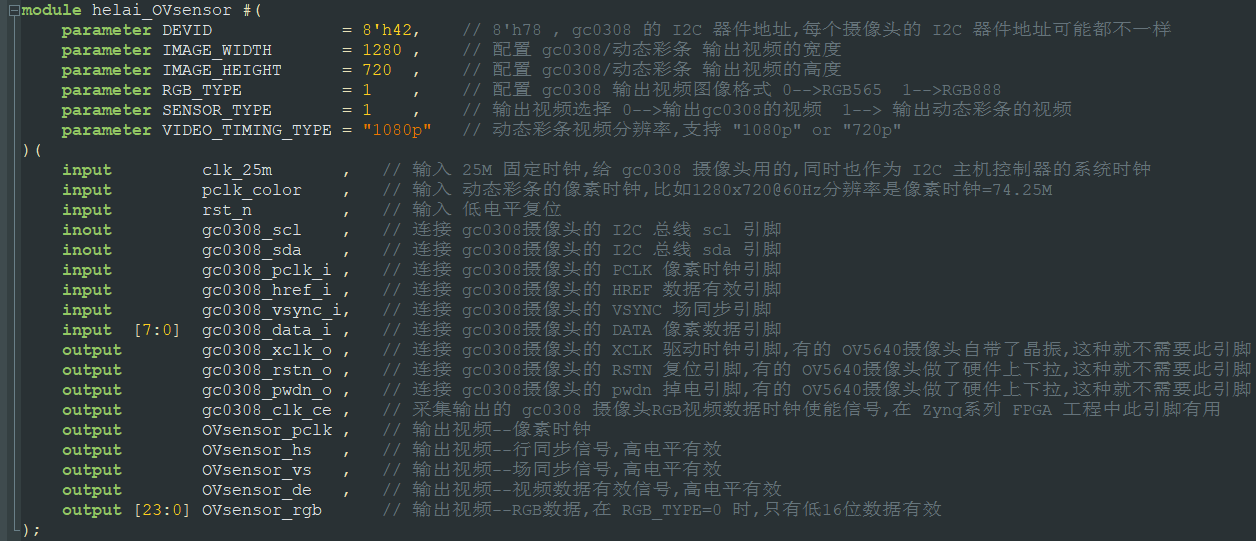

輸入Sensor之–>GC0308攝像頭

輸入Sensor是本工程的輸入設備,其一為GC0308攝像頭,此外本博主在工程中還設計了動態彩條模塊,彩條由FPGA內部邏輯產生,且是動態移動的,完全可模擬Sensor,輸入源選擇Sensor還是彩條,通過Sensor模塊的頂層參數配置,默認選擇Sensor輸入;Sensor模塊如下:

SENSOR_TYPE=0;則輸出GC0308攝像頭采集的視頻;

SENSOR_TYPE=1;則輸出動態彩條的視頻;

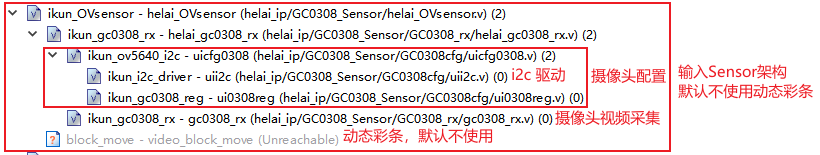

GC0308攝像頭需要i2c初始化配置,本設計配置為640x480@30Hz分辨率,本設計提供純verilog代碼實現的i2c模塊實現配置功能;此外,GC0308攝像頭還需要圖像采集模塊實現兩個時鐘輸出一個RGB565的視頻轉換為一個時鐘輸出一個RGB888視頻,本設計提供純verilog代碼實現的圖像采集模塊實現配置功能;動態彩條則由FPGA內部邏輯實現,由純verilog代碼編寫;將GC0308攝像頭配置采集和動態彩條進行代碼封裝,形成helai_OVsensor.v的頂層模塊,整個模塊代碼架構如下:

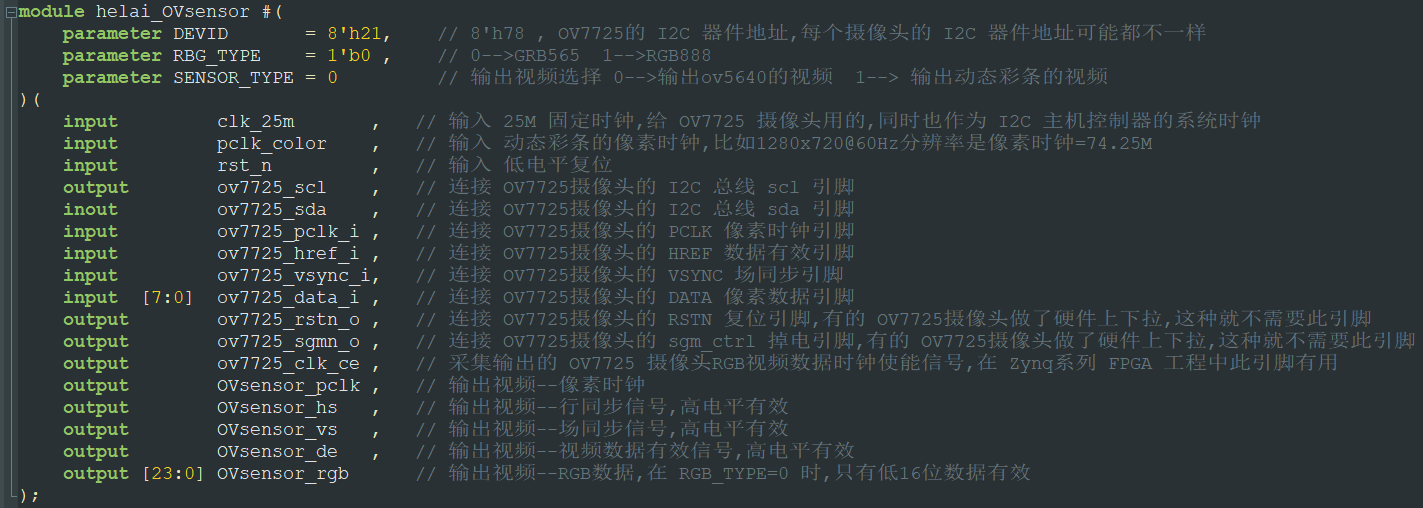

輸入Sensor之–>OV7725攝像頭

輸入Sensor是本工程的輸入設備,其一為OV7725攝像頭,此外本博主在工程中還設計了動態彩條模塊,彩條由FPGA內部邏輯產生,且是動態移動的,完全可模擬Sensor,輸入源選擇Sensor還是彩條,通過Sensor模塊的頂層參數配置,默認選擇Sensor輸入;Sensor模塊如下:

SENSOR_TYPE=0;則輸出OV7725攝像頭采集的視頻;

SENSOR_TYPE=1;則輸出動態彩條的視頻;

OV7725攝像頭需要i2c初始化配置,本設計配置為640x480@60Hz分辨率,本設計提供純verilog代碼實現的i2c模塊實現配置功能;此外,OV7725攝像頭還需要圖像采集模塊實現兩個時鐘輸出一個RGB565的視頻轉換為一個時鐘輸出一個RGB888視頻,本設計提供純verilog代碼實現的圖像采集模塊實現配置功能;動態彩條則由FPGA內部邏輯實現,由純verilog代碼編寫;將OV7725攝像頭配置采集和動態彩條進行代碼封裝,形成helai_OVsensor.v的頂層模塊,整個模塊代碼架構如下:

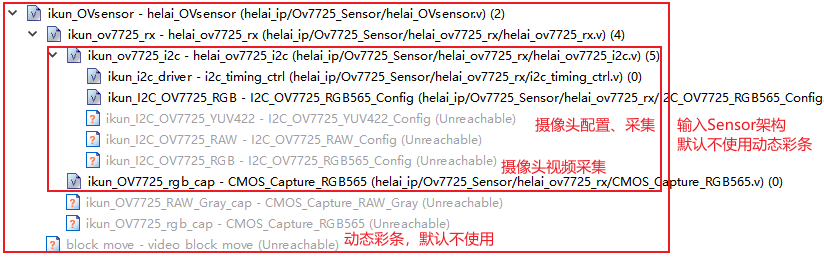

輸入Sensor之–>OV5640攝像頭

輸入Sensor是本工程的輸入設備,其一為OV5640攝像頭,此外本博主在工程中還設計了動態彩條模塊,彩條由FPGA內部邏輯產生,且是動態移動的,完全可模擬Sensor,輸入源選擇Sensor還是彩條,通過Sensor模塊的頂層參數配置,默認選擇Sensor輸入;Sensor模塊如下:

SENSOR_TYPE=0;則輸出OV5640攝像頭采集的視頻;

SENSOR_TYPE=1;則輸出動態彩條的視頻;

OV5640攝像頭需要i2c初始化配置,本設計配置為1280x720@30Hz分辨率,本設計提供純verilog代碼實現的i2c模塊實現配置功能;此外,OV5640攝像頭還需要圖像采集模塊實現兩個時鐘輸出一個RGB565的視頻轉換為一個時鐘輸出一個RGB888視頻,本設計提供純verilog代碼實現的圖像采集模塊實現配置功能;動態彩條則由FPGA內部邏輯實現,由純verilog代碼編寫;將OV5640攝像頭配置采集和動態彩條進行代碼封裝,形成helai_OVsensor.v的頂層模塊,整個模塊代碼架構如下:

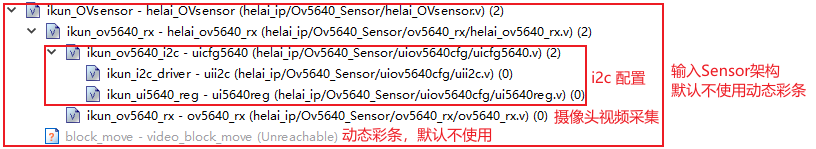

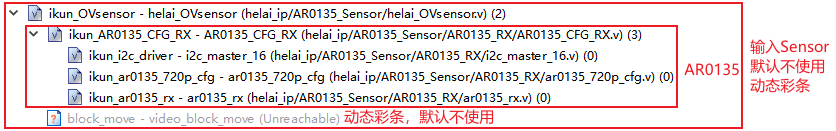

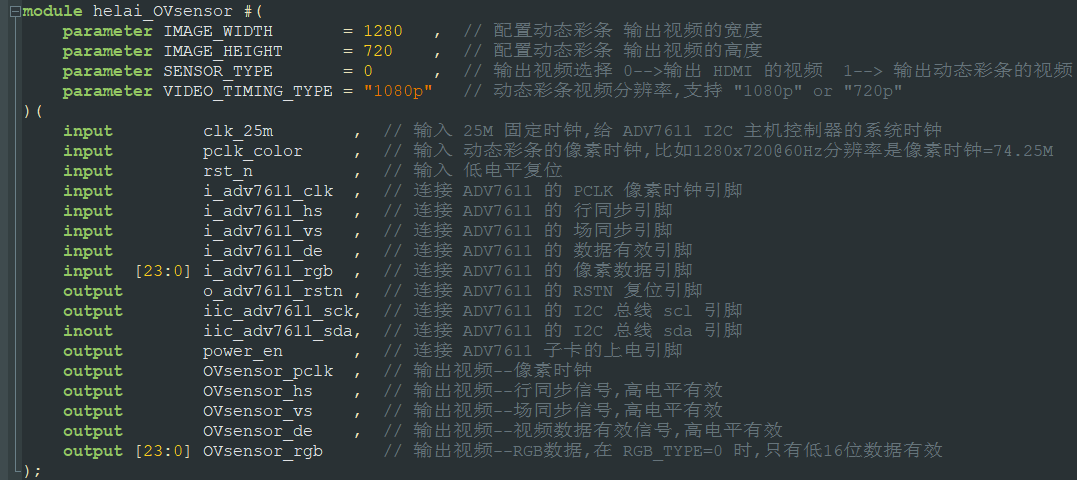

輸入Sensor之–>AR0135攝像頭

輸入Sensor是本工程的輸入設備,其一為AR0135攝像頭,此外本博主在工程中還設計了動態彩條模塊,彩條由FPGA內部邏輯產生,且是動態移動的,完全可模擬Sensor,輸入源選擇Sensor還是彩條,通過Sensor模塊的頂層參數配置,默認選擇Sensor輸入;Sensor模塊如下:

SENSOR_TYPE=0;則輸出OV5640攝像頭采集的視頻;

SENSOR_TYPE=1;則輸出動態彩條的視頻;

AR0135攝像頭需要i2c初始化配置,本設計配置為1280x720@60Hz分辨率,本設計提供純verilog代碼實現的i2c模塊實現配置功能;動態彩條則由FPGA內部邏輯實現,由純verilog代碼編寫;將AR0135攝像頭配置采集和動態彩條進行代碼封裝,形成helai_OVsensor.v的頂層模塊,整個模塊代碼架構如下:

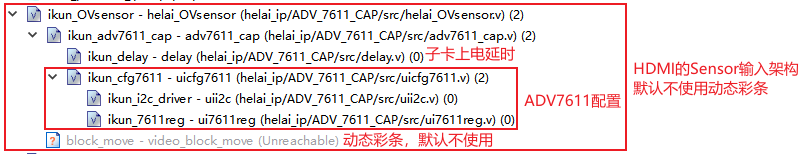

輸入Sensor之–>ADV7611芯片解碼的HDMI

輸入Sensor是本工程的輸入設備,其一為板載的HDMI輸入接口;輸入源為板載的HDMI輸入接口或動態彩條,分辨率為1920x1080@60Hz,使用筆記本電腦接入HDMI輸入接口,以模擬輸入Sensor;HDMI解碼方案為芯片解碼,使用ADV7611,可將輸入的HDMI視頻解碼為RGB888視頻;FPGA純verilog實現的i2c配置模塊完成對ADV7611芯片的配置,分辨率配置為1920x1080@60Hz;可以通過Sensor模塊的頂層參數配置,默認選擇Sensor輸入;Sensor模塊如下:

SENSOR_TYPE=0;則輸出HDMI接口采集的視頻;

SENSOR_TYPE=1;則輸出動態彩條的視頻;

整個模塊代碼架構如下:

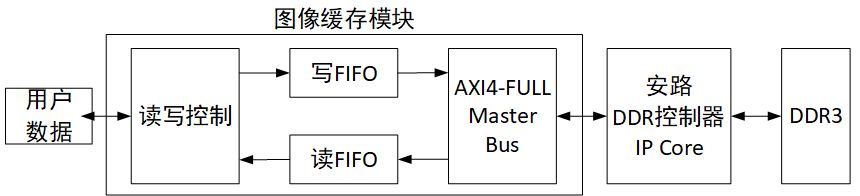

FDMA圖像緩存

FDMA圖像緩存架構實現的功能是將輸入視頻緩存到板載DDR3中再讀出送后續模塊,目的是實現視頻同步輸出,實現輸入視頻到輸出視頻的跨時鐘域問題,更好的呈現顯示效果;由于調用了安路官方的MIG IP核作為DDR控制器,所以FDMA圖像緩存架構就是實現用戶數據到MIG的橋接作用;架構如下:

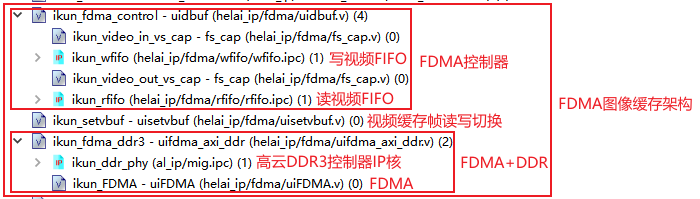

FDMA圖像緩存架構由FDMA控制器+FDMA組成;FDMA實際上就是一個AXI4-FULL總線主設備,與MIG對接,MIG配置為AXI4-FULL接口;FDMA控制器實際上就是一個視頻讀寫邏輯,以寫視頻為例,假設一幀圖像的大小為M×N,其中M代表圖像寬度,N代表圖像高度;FDMA控制器每次寫入一行視頻數據,即每次向DDR3中寫入M個像素,寫N次即可完成1幀圖像的緩存,讀視頻與之一樣;同時調用兩個FIFO實現輸入輸出視頻的跨時鐘域處理,使得用戶可以AXI4內部代碼,以簡單地像使用FIFO那樣操作AXI總線,從而達到讀寫DDR的目的,進而實現視頻緩存;本設計圖像緩存方式為3幀緩存;圖像緩存模塊代碼架構如下:

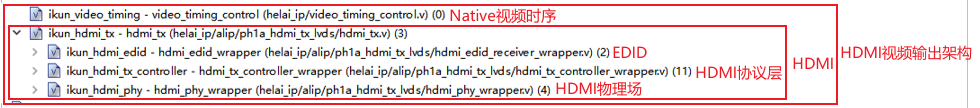

HDMI視頻輸出架構

緩存圖像從DDR3讀出后經過Native時序生成模塊輸出標準的VGA時序視頻,然后經過純verilog顯示的RGB轉HDMI模塊輸出HDMI差分視頻;最后送顯示器顯示即可;代碼例化如下:

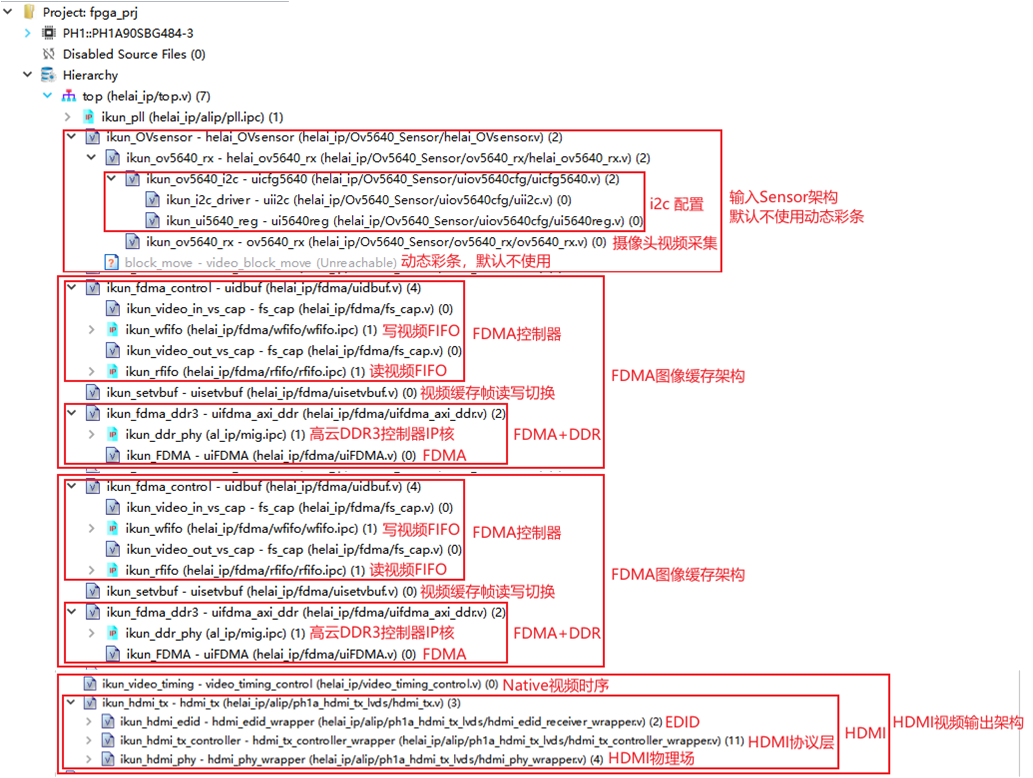

工程源碼架構

以工程3為例,工程源碼架構如下:

4、TD工程源碼1詳解:GC0308輸入版本

開發板FPGA型號:國產安路–PH1A90SBG484-3;

開發環境:TangDynasty 6.0.2;

輸入:GC0308攝像頭或FPGA內部動態彩條,分辨率640x480@30Hz;

輸出:HDMI,RTL編碼,分辨率640x480@60Hz;

圖像緩存方案:FDMA圖像緩存,3幀緩存;

工程源碼架構請參考前面第3章節中的《工程源碼架構》小節;

工程作用:此工程目的是讓讀者掌握國產安路FPGA實現圖像視頻采集系統的設計能力,以便能夠移植和設計自己的項目;

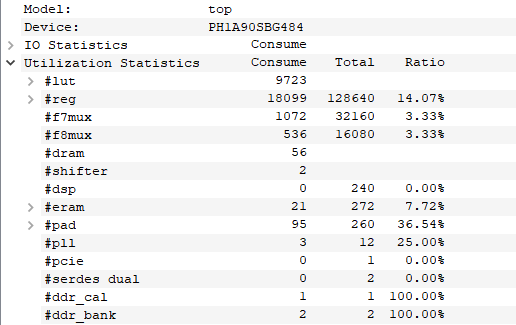

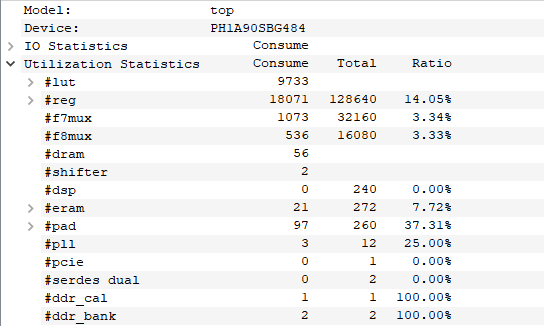

工程的資源消耗和功耗如下:

5、TD工程源碼2詳解:OV7725輸入版本

開發板FPGA型號:國產安路–PH1A90SBG484-3;

開發環境:TangDynasty 6.0.2;

輸入:OV7725攝像頭或FPGA內部動態彩條,分辨率640x480@30Hz;

輸出:HDMI,RTL編碼,分辨率640x480@60Hz;

圖像緩存方案:FDMA圖像緩存,3幀緩存;

工程源碼架構請參考前面第3章節中的《工程源碼架構》小節;

工程作用:此工程目的是讓讀者掌握國產安路FPGA實現圖像視頻采集系統的設計能力,以便能夠移植和設計自己的項目;

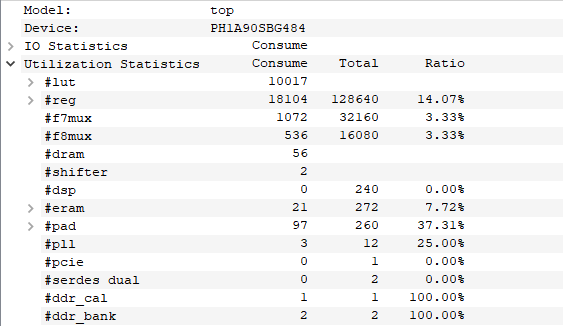

工程的資源消耗和功耗如下:

6、TD工程源碼3詳解:OV5640輸入版本

開發板FPGA型號:國產安路–PH1A90SBG484-3;

開發環境:TangDynasty 6.0.2;

輸入:OV5640攝像頭或FPGA內部動態彩條,分辨率1280x720@30Hz;

輸出:HDMI,RTL編碼,分辨率1280x720@60Hz;

圖像緩存方案:FDMA圖像緩存,3幀緩存;

工程源碼架構請參考前面第3章節中的《工程源碼架構》小節;

工程作用:此工程目的是讓讀者掌握國產安路FPGA實現圖像視頻采集系統的設計能力,以便能夠移植和設計自己的項目;

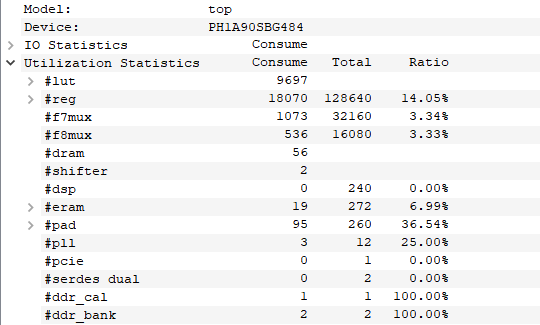

工程的資源消耗和功耗如下:

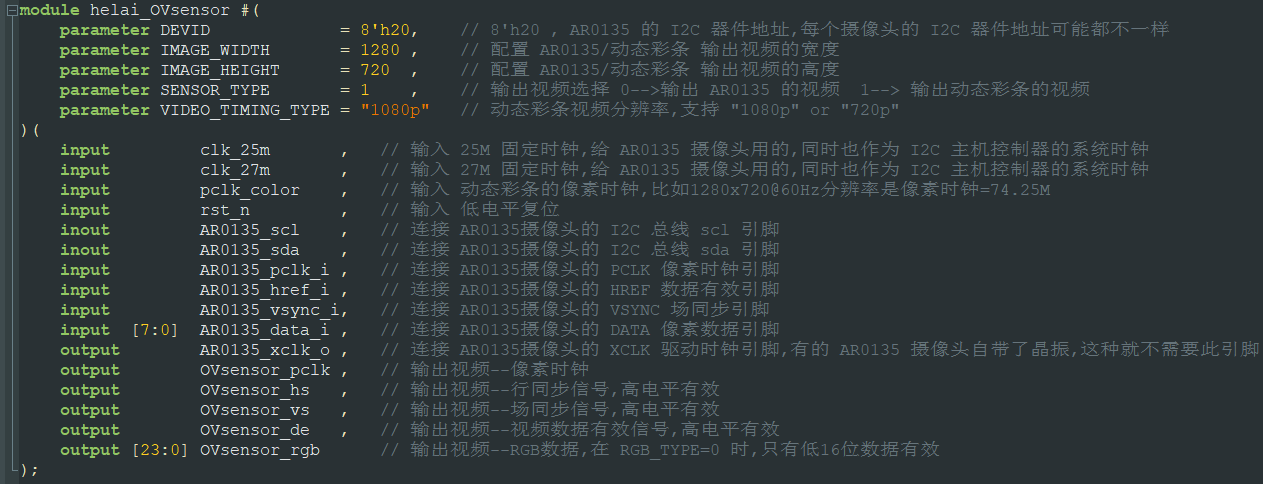

7、TD工程源碼4詳解:AR0135輸入版本

開發板FPGA型號:國產安路–PH1A90SBG484-3;

開發環境:TangDynasty 6.0.2;

輸入:AR0135攝像頭或FPGA內部動態彩條,分辨率1280x720@60Hz;

輸出:HDMI,RTL編碼,分辨率1280x720@60Hz;

圖像緩存方案:FDMA圖像緩存,3幀緩存;

工程源碼架構請參考前面第3章節中的《工程源碼架構》小節;

工程作用:此工程目的是讓讀者掌握國產安路FPGA實現圖像視頻采集系統的設計能力,以便能夠移植和設計自己的項目;

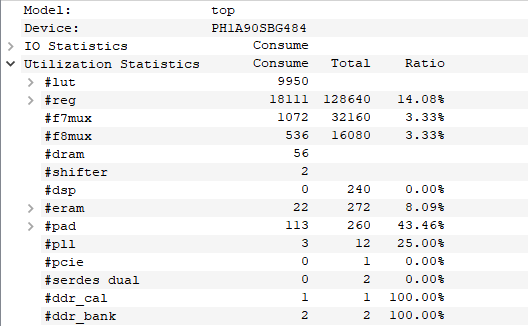

工程的資源消耗和功耗如下:

8、TD工程源碼5詳解:HDMI輸入版本

開發板FPGA型號:國產安路–PH1A90SBG484-3;

開發環境:TangDynasty 6.0.2;

輸入:HDMI或者FPGA內部動態彩條,ADV7611芯片解碼方案,分辨率1920x1080@60Hz,筆記本電腦模擬輸入源;

輸出:HDMI,RTL編碼,分辨率1920x1080@60Hz;

圖像緩存方案:FDMA圖像緩存,3幀緩存;

工程源碼架構請參考前面第3章節中的《工程源碼架構》小節;

工程作用:此工程目的是讓讀者掌握國產安路FPGA實現圖像視頻采集系統的設計能力,以便能夠移植和設計自己的項目;

工程的資源消耗和功耗如下:

9、上板調試驗證并演示

準備工作

你需要有以下裝備才能移植并測試該工程代碼:

1:FPGA開發板;

2:OV7725或OV5640攝像頭或筆記本電腦,沒有則請使用FPGA內部生成的彩條;

3:HDMI傳輸線;

4:HDMI顯示,要求分辨率支持1920x1080;

國產安路FPGA視頻采集效果演示

國產安路FPGA視頻采集效果演示如下:

安路-圖像采集

10、工程源碼

工程源碼如下:

)

:Python腳本中使?PaddleOCR)