現在數字經濟發展地相當快速,像Cloud、現在火紅的AI、大數據這些新技術都需要在數據中心里運行更多運算,伴隨而來的是更快的數據傳輸速度的需求。 在數據中心,有很多條數據傳輸路徑,舉例 :

- Server 和Storage之間(通過PCIe)

- CPU和各種適配器之間(通過PCIe)

- GPU跟GPU組成的Cluster (透過NVLink或Ethernet)

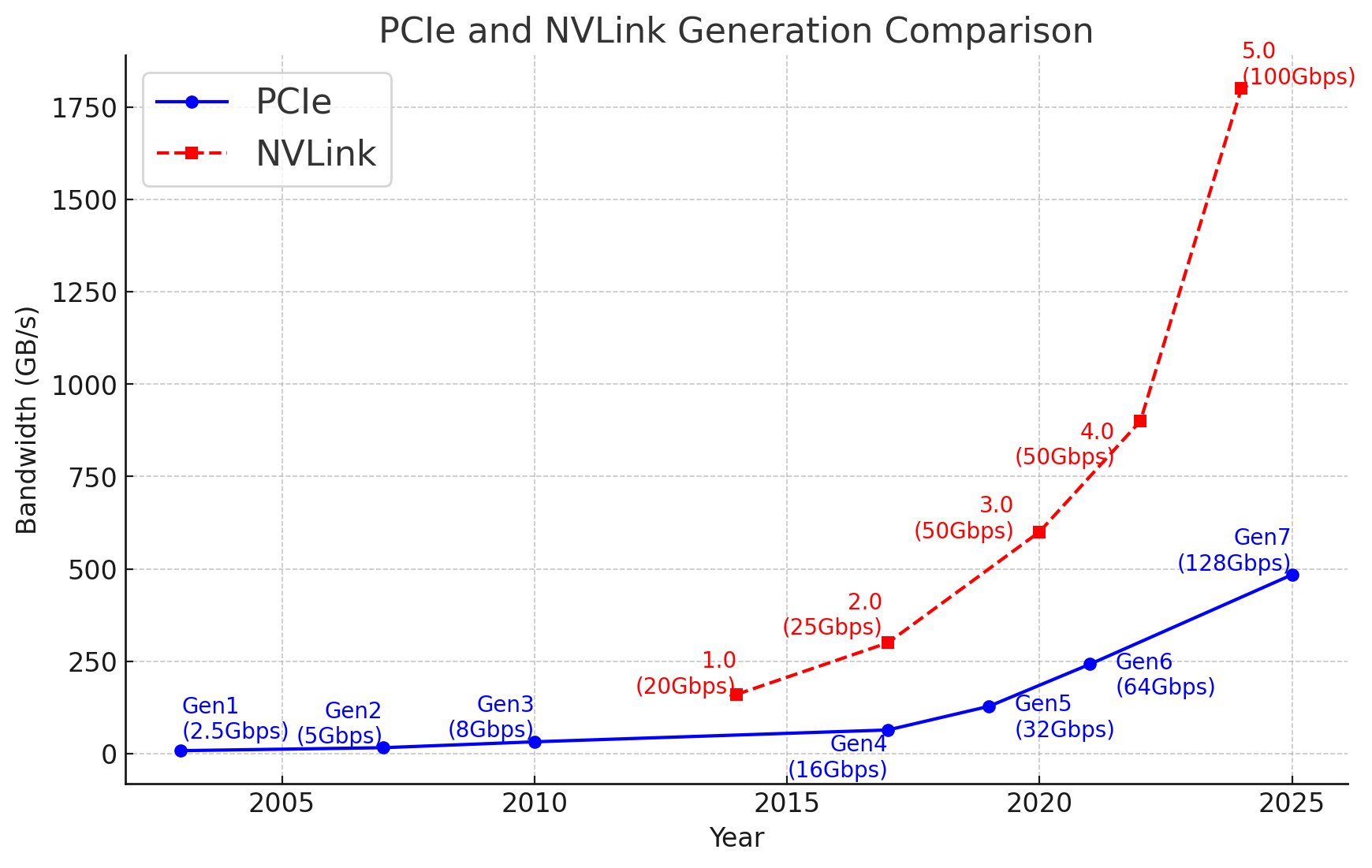

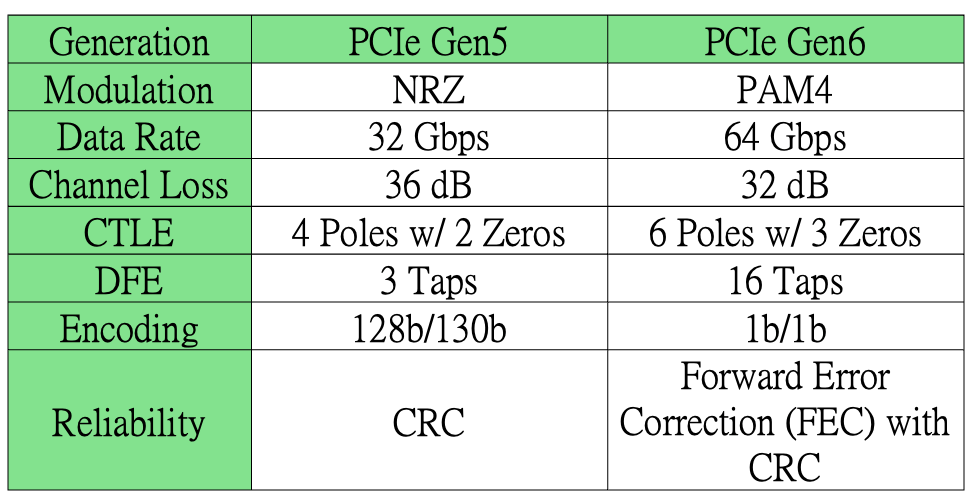

相當多樣的數據傳輸拓樸不停交換大量數據,以應付即時運算和龐大的數據讀寫需求。 所以,硬件接口技術也必須不斷升級,否則整個系統就會被數據傳輸帶寬給卡住。 在傳統服務器領域,一直都是PCIe當作主要高速傳輸媒介,靠著將每個Lane的Data Rate提高,進而提升整體帶寬。 但到了PCIe Gen6這一關,單靠傳統的NRZ編碼技術已經遇到相當大的瓶頸。

P.S. 由于PCIe的演進太慢,帶寬太差,因此nVIDIA自行研發NVLink(已經要邁向200G-PAM4)將自己的芯片構建成的系統達到另一個層次,這其實是Ethernet網絡的領域,咱們再另外說明! 這也是為什么會有UALink的緣故!

?

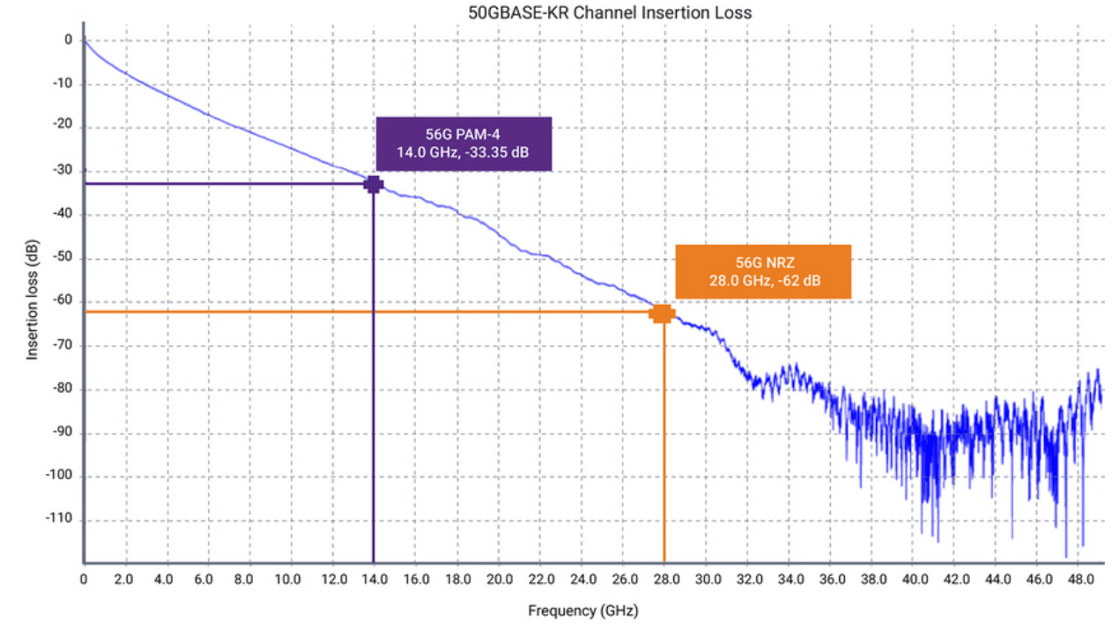

為什么說Gen6會有瓶頸? 主要原因在于SI的綜合考量。 Gen6的Data Rate是64Gbps,相較Gen5的32Gbps多了一倍,如果利用NRZ編碼技術,最高的Clock頻率高達32GHz(或者可以說Nyquist Frequency),這使得我們在關注的損耗帶寬不好實現。 如圖片說明,56Gbps-NRZ的通道損耗在28GHz高達62dB,現今等化器(Equalizer, EQ)技術可無法到達這一水平。 而PAM4的訊號調變方式將帶寬再多降低一倍至14GHz,相同通道的損耗可以變小為33dB,對EQ來講相當友善!

?

為什么 PCIe Gen6 使用 PAM4 ?

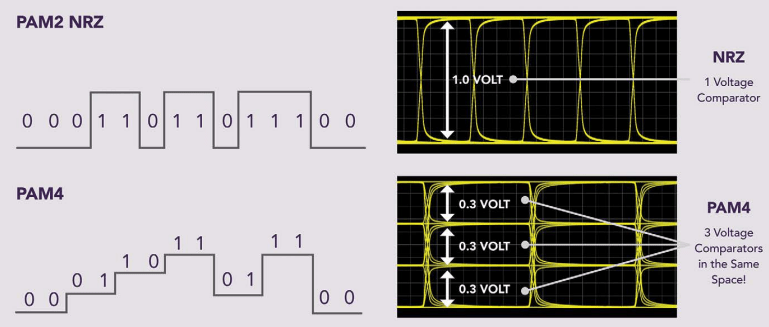

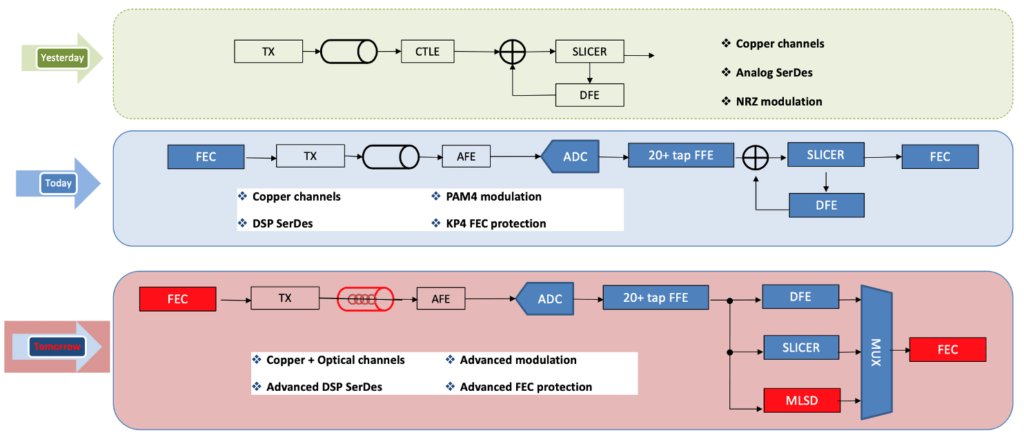

傳統通道調變技術是NRZ (或稱作PAM2),只有兩個電壓階層,每個符號(Symbol)僅能承載 1 bit 資訊,若硬要單靠NRZ再將符號速率倍增,就必須在更高的頻段運作,帶來嚴重的高頻損耗,同時需要在材料和走線技術上付出極高成本才能維持良好的訊號質量。

PAM4技術正好滿足了這個「有限帶寬中實現高數據密度」的需求。 PAM4 在同樣的數據傳輸速度下,把信號幅度劃分成四個等級,因而在一個符號間隔中能傳遞 2 bit 的信息。 換句話說,相同速度下PAM4可以傳遞兩倍于NRZ的數據,有效帶寬自然可以再往下降。

?

除了在速率與帶寬之間取得較好的平衡,PAM4 另一個優勢在于整個高速領域已經累積了相當多的應用經驗。 在Ethernet領域,56G和112G SerDes已采用PAM4調變,所以芯片IP、量測設備和高速布線技術已相當成熟,也讓業界對PAM4的噪聲模型、EQ、FFE/DFE都有了深厚的研究。 所以PCIe采用PAM4,也就能承接這些既有的技術成果與生態系統,減少從零開始摸索的風險與成本。

PCIe Gen6 PCB Material Selection from SI View

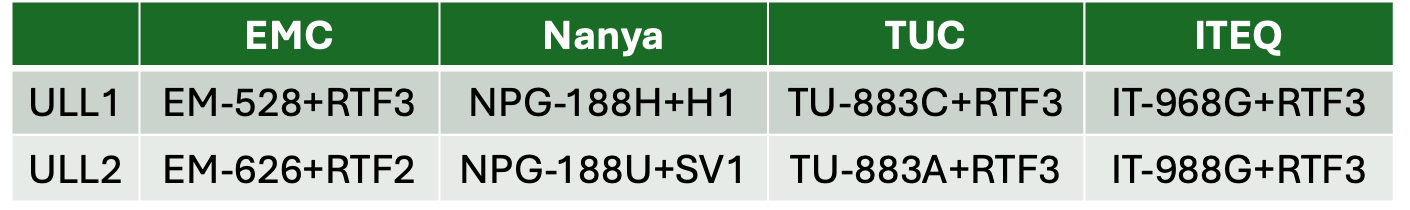

有別于PCIe Gen5的36dB,PCIe Gen6的Channel loss budget為32dB。 Intel的文件里有提到,從Gen5的Birch Stream升級到Gen6的Oak Stream會需要將CCL材料的等級從ULL1(0.96dB/inch)提升到ULL2(0.85dB/inch),從臺灣的CCL供應鏈來看,臺光電推出高性價比的EM626搶攻市場,臺曜與聯茂各有相關解決方案。 其中南亞較晚切入中高階領域,剛進來就推出極高性價比的NPG-188U,據說已經有許多ODM導入使用中。

?

?

PAM4’s Challenge

然而事情總是一體兩面,PAM4也是帶來相當多的挑戰:

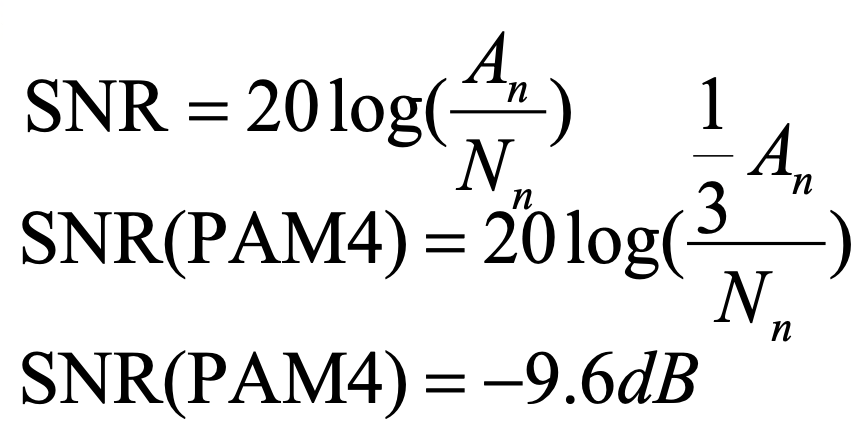

- 較差的SNR(Signal-to-Noise Ratio): 由于原先的振幅范圍內要多塞進兩個電壓準位,所以有別于NRZ眼圖的一顆眼睛,PAM4眼睛會有三顆,振幅縮小1/3,也就是說天生的SNR就比NRZ調變少了9.6dB。

?

- 抗噪聲能力差:由于天生少了9.6dB的SNR,使其對于噪聲較為敏感,一般對于NRZ的Power-Sum Crosstalk要求是-30dB,而PAM4我們會盡量要求在-45dB。

- EQ設計更復雜:由于天生較低的SNR,導致Receiver需要用更強的EQ補償信號,設計者與測試單位需要更多地理解這些EQ的任務。

?

- FEC(Forward Error Correction):可以針對誤碼進行偵錯并糾錯,不過系統延遲會上升。

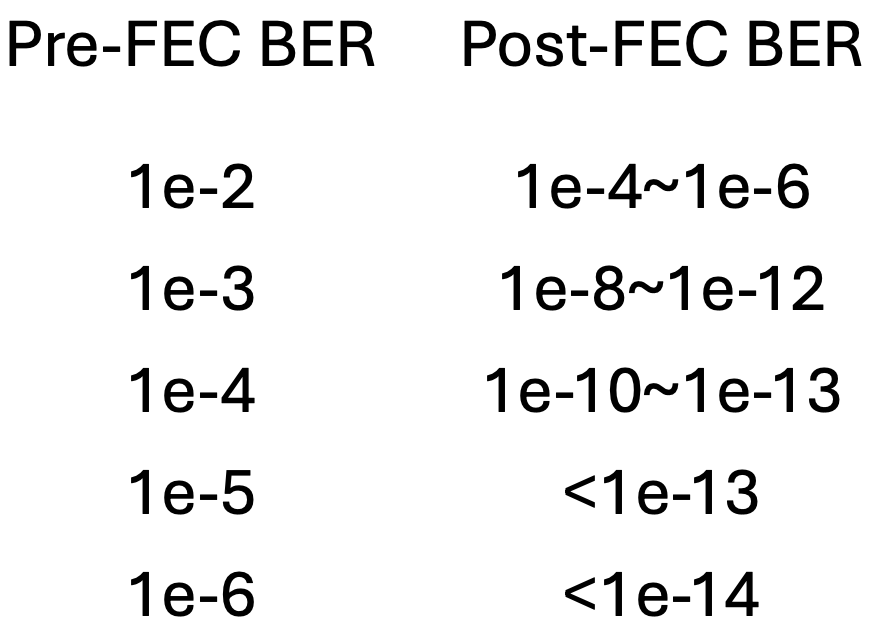

- NRZ的BER要求是小于1e-12,但是PAM4的Pre-FEC BER(或稱作Raw BER)則是1e-5左右,透過FEC的糾錯可以將Post-FEC BER降低至1e-12以下。

?

- 較大的功耗:由于引入比較多的EQ,且使用了FEC,這些新導入的技術會大大地提升整個系統功耗,使得電源完整性與PCB板溫的議題浮上臺面。 (P.S.這也是為什么Linear Pluggable Optics, LPO被提出來的主要原因)

- 測試設備升級:PAM4不再是一個單一眼圖,而是三個「眼」需要同時觀測與評估,量測示波器與 BERT必須支持更高帶寬與更細膩的分析功能。

PAM4的確是可以將設計的有效帶寬降低,在PCB材料的選擇上保持更多彈性,不過設計者得面臨更高層次的 SI/PI考量、電路設計復雜度,以及測試驗證的高門檻。 在臺灣,由于設計Ethernet的人跟PCIe的人比較不會overlap,所以目前設計PCIe的人初期可能會比較辛苦,但將設計面向放寬,多留些Margin,一定可以輕松征服PAM4!

?

)

2022 版安裝與下載教程)

Java/python/JavaScript/C/C++/GO最佳實現)

:深入剖析電子商務商業模式)