?名詞解釋:

ADC:?Analog-to-Digital

SAR:Successive Approximation Register

? ? ? ? 本文將介紹ADC的概念、相關函數以及STM32CubeMX生成ADC的配置函數。針對于ADC實踐:單通道采集芯片內部溫度傳感器(ADC1_ch16);利用軟件觸發單次觸發多通道DMA ADC采集;利用定時器單次/連續觸發多通道DMA ADC采集。

1.?什么是ADC?

1.1?ADC概念

1.1.0 ADC采集方法-逐次逼近寄存器型ADC

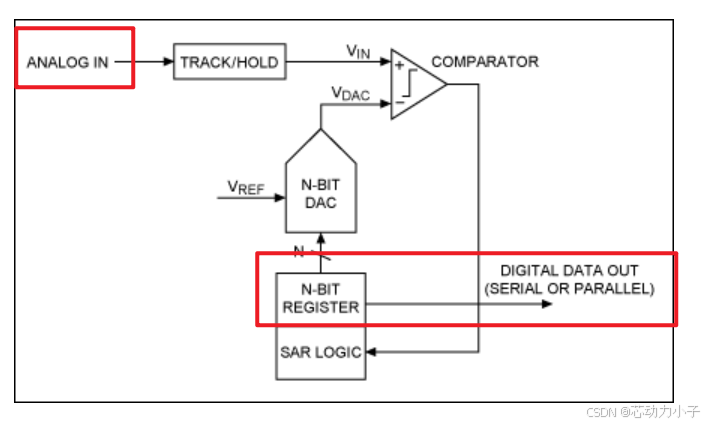

????????通過 “逐位試探比較” 的方式,從最高位(MSB)到最低位(LSB)依次確定每一位的二進制值,最終生成與輸入模擬信號對應的數字代碼。其結構框圖如下:

????????

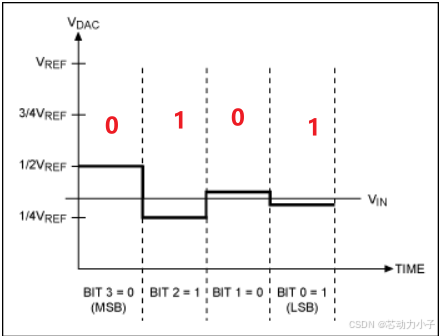

????????一個4位轉換示例,y軸(和圖中的粗線)表示DAC的輸出電壓。本例中,第一次比較表明VIN?< VDAC。所以,位3置為0。然后DAC被置為0b0100,并執行第二次比較。由于VIN?> VDAC,位2保持為1。DAC置為0b0110,執行第三次比較。根據比較結果,位1置0,DAC又設置為0b0101,執行最后一次比較。最后,由于VIN?> VDAC,位0確定為1。

????????

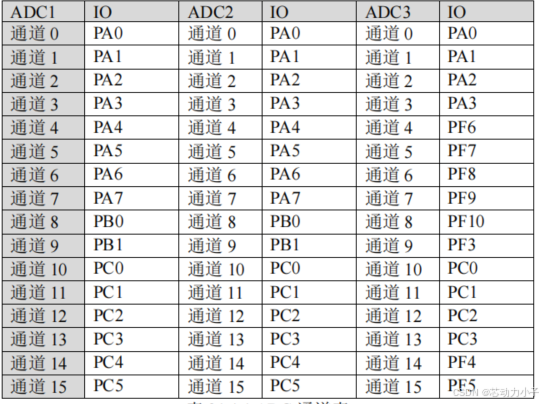

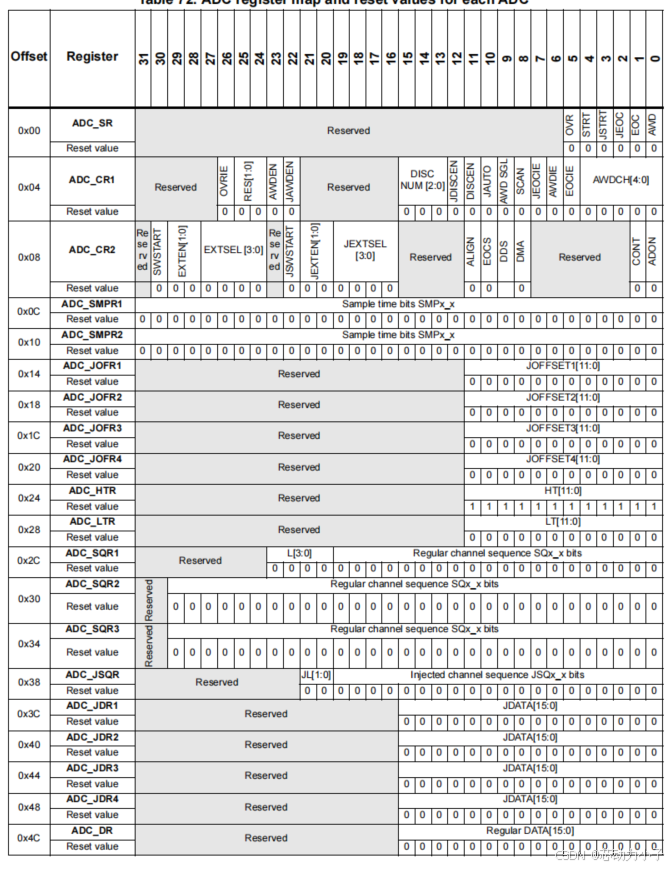

1.1.1 ADC功能

????????STM32的ADC(Analog-to-Digital Converter)是一個 ?12位逐次逼近型(SAR)模數轉換器,支持多通道、多模式信號采集,

- 分辨率?:可配置為12位、10位、8位或6位(通過犧牲分辨率提升轉換速度)。

- ?輸入通道?:最多19個復用通道,包括:

- ?16個外部引腳?(如溫度、電壓、電流傳感器輸入)。

- ?2個內部信號源?(內部溫度傳感器、內部參考電壓)。

- ?VBAT通道?:直接測量電池電壓(需特定型號支持)。

- ?轉換模式?:單次、連續、掃描、不連續采樣模式。

- ?數據存儲?:16位數據寄存器,支持左對齊或右對齊格式。

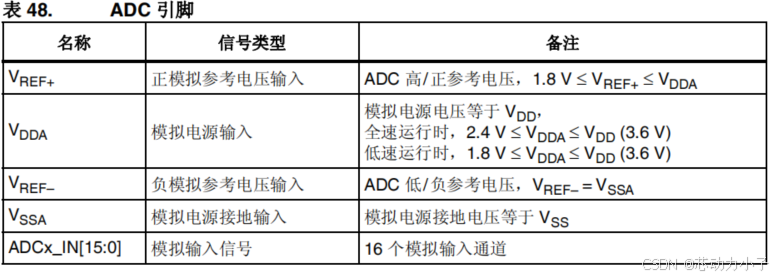

- ADC 電源要求:全速運行時為 2.4 V 到 3.6 V ,慢速運行時為 1.8 V

- ADC 輸入范圍: V REF- ? <=? VIN? <=?VREF+

- ?模擬看門狗(Analog Watchdog, AWD)??:監測輸入電壓是否超出用戶設定的閾值范圍,觸發中斷或事件

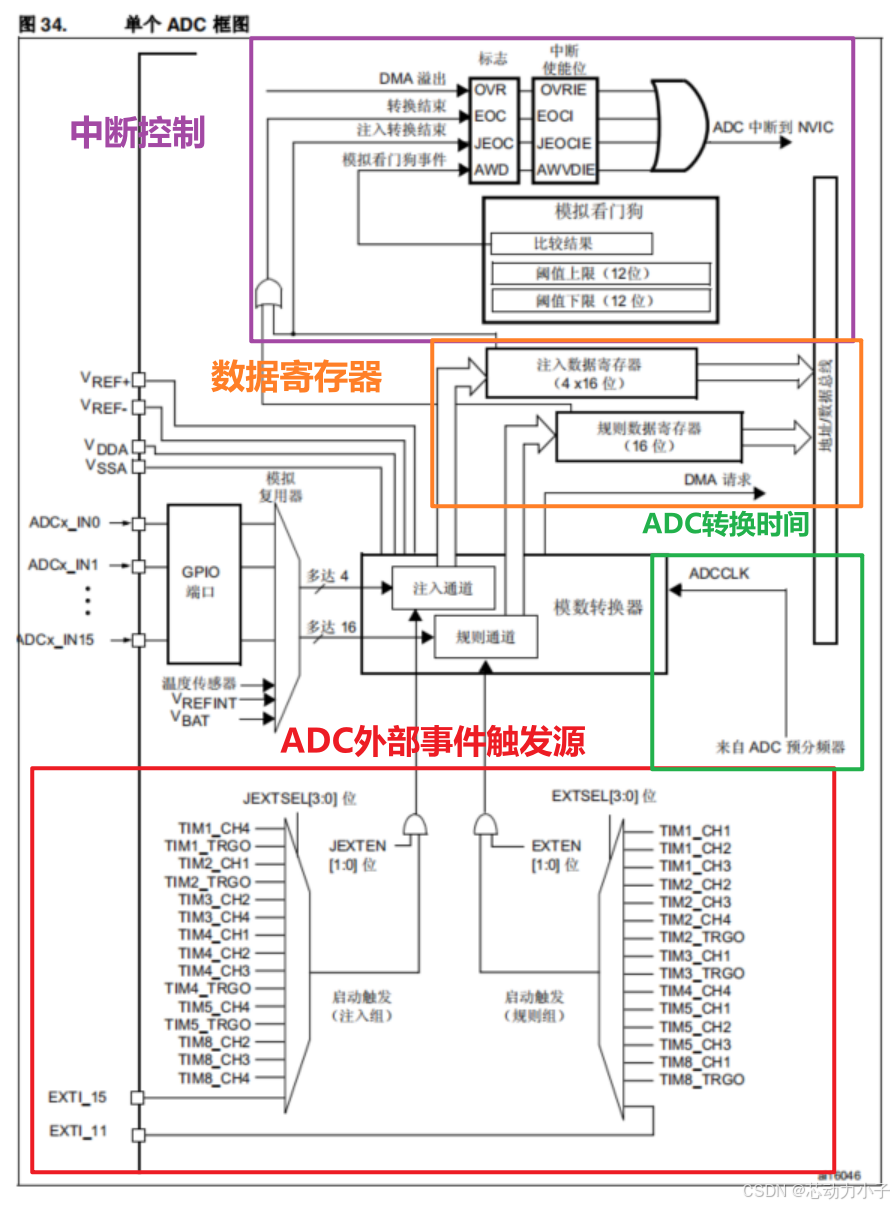

1.1.2 ADC框圖

????????

????????

????????

1.2 ADC功能介紹

1.2.1 ADC開關控制、時鐘選擇、ADC通道選擇

1.?ADC開關控制

ADC_CR2.ADON?(A/D Converter ON / OFF):(0為禁止ADC;1為使能ADC)

ADC_CR2.SWSTART(Start conversion of regular channels):開始轉換規則通道(1為開始轉換)

ADC_CR2.JSWSTART(Start conversion of injected channels):開始轉換注入通道(1為開始轉換)

2.?ADC時鐘選擇

- 模擬電路時鐘(ADCCLK)-?所有 ADC 共用

· 驅動ADC的模擬電路部分,包括采樣保持電路(Sample&Hold)和SARADC。

·RCC_CFGR中的ADCPRE位,設置ADC分頻系數。 - 數字接口時鐘

· 等效時鐘?:直接使用APB2總線時鐘(f_{PCLK2}),無分頻。

· ?使能控制?:通過RCC_APB2ENR寄存器為每個ADC獨立使能/禁用數字接口時鐘。

__HAL_RCC_ADC1_CLK_ENABLE(); ? // 使能ADC1數字接口時鐘

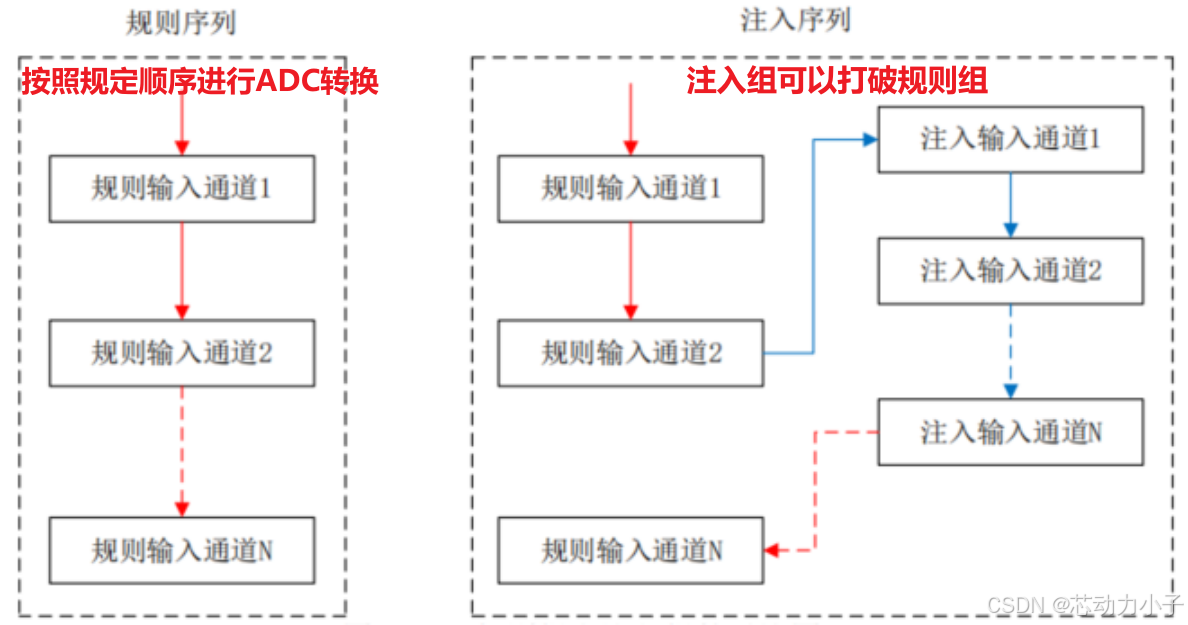

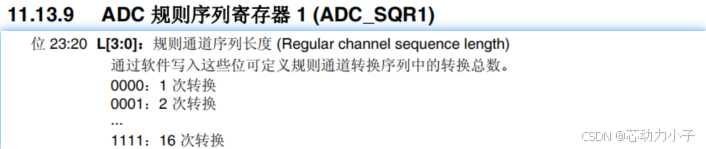

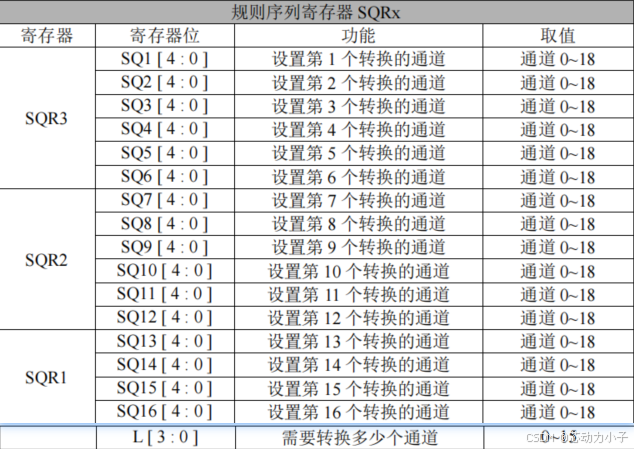

3.?ADC通道選擇(分為規則轉換和注入轉換)

????????

????????

? ? ? ? 下圖為正點原子總結的規則組與寄存器對應表

????????

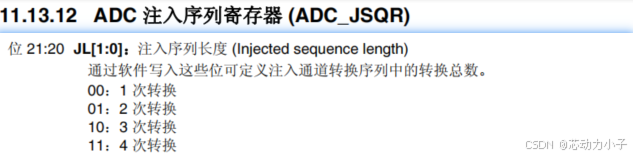

????????下圖為正點原子總結的注入組與寄存器對應表

????????

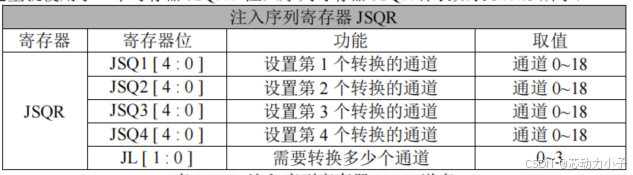

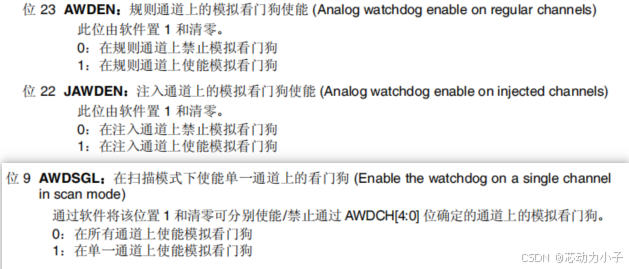

1.2.2 模擬看門狗

- 發生模擬看門狗標志

ADC_SR.AWD - 模擬看門狗中斷使能

ADC_CR1.AWDIE - 模擬看門狗保護區域

- 閾值上下限設置(V = VREF*HTR(LTR)/4096)

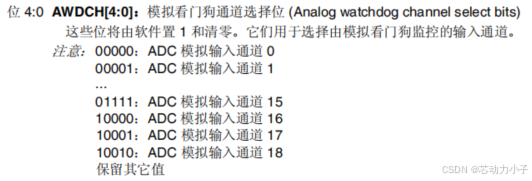

ADC_HTR 與 ADC_LTR - 模擬看門狗通道選擇(ADC_CR1.AWDCH[4:0])

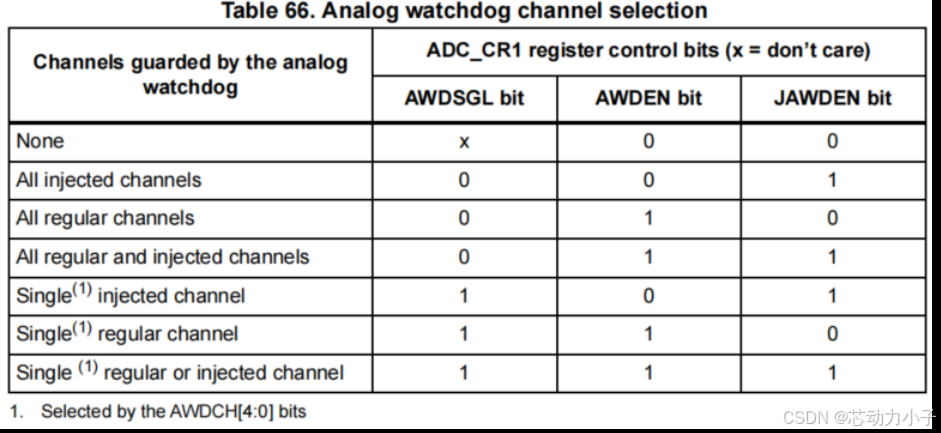

1.2.3 單次轉換模式、連續轉換模式(ADC_CR2.CONT)

????????ADC_CR2.CONT:0為單次轉換模式;1為連續轉換模式

????????

1. 單次轉換觸發方式

????????● 將 ADC_CR2 寄存器中的 SWSTART 位置 1(僅適用于規則通道)

????????● 將 JSWSTART 位置 1(適用于注入通道)

????????● 外部觸發(適用于規則通道或注入通道)

2. 單次轉換流程

- 規則通道轉換完成?:

- ?數據存儲?:結果存入

ADC_DR(16位數據寄存器)。 - ?標志位?:

EOC=1(轉換結束標志)。 - ?中斷觸發?:若

EOCIE=1,產生中斷通知CPU讀取數據。 - ?ADC狀態?:自動停止,等待下次觸發。

- ?數據存儲?:結果存入

- ?注入通道轉換完成?:

- ?數據存儲?:結果存入

ADC_JDR1(注入數據寄存器)。 - ?標志位?:

JEOC=1(注入轉換結束標志)。 - ?中斷觸發?:若

JEOCIE=1,產生中斷。 - ?ADC狀態?:自動停止。

- ?數據存儲?:結果存入

3. 連續轉換觸發方式

- 規則通道?:

- ?軟件觸發?:置位

ADC_CR2.SWSTART=1。 - ?外部觸發?:配置外部觸發源(如PWM同步信號)。

- ?軟件觸發?:置位

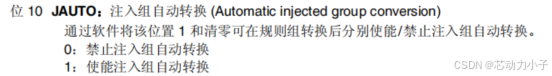

- ?注入通道限制?:

- ?默認禁止連續轉換?:注入通道無法獨立啟動連續轉換。

- ?唯一例外?:若使能自動注入(

JAUTO=1),注入通道可在規則通道組之后 ?自動插入轉換。

4. 連續轉換觸發方式

● 規則通道組轉換完成?:

- ?數據存儲?:最新結果覆蓋

ADC_DR寄存器。 - ?標志位?:

EOC=1(每次轉換結束均置位)。 - ?中斷觸發?:若

EOCIE=1,每次轉換均觸發中斷。 - ?ADC狀態?:立即啟動下一輪轉換,無需外部觸發

● ?自動注入模式(JAUTO=1)?

- ?功能?:在規則通道組轉換完成后,自動插入注入通道轉換。

- ?流程?:

- 規則通道組轉換完成 → 觸發注入通道轉換。

- 注入通道結果存入

ADC_JDR1,JEOC=1。 - 中斷觸發:若

JEOCIE=1,通知CPU處理注入數據。 - ADC繼續下一輪規則通道轉換。

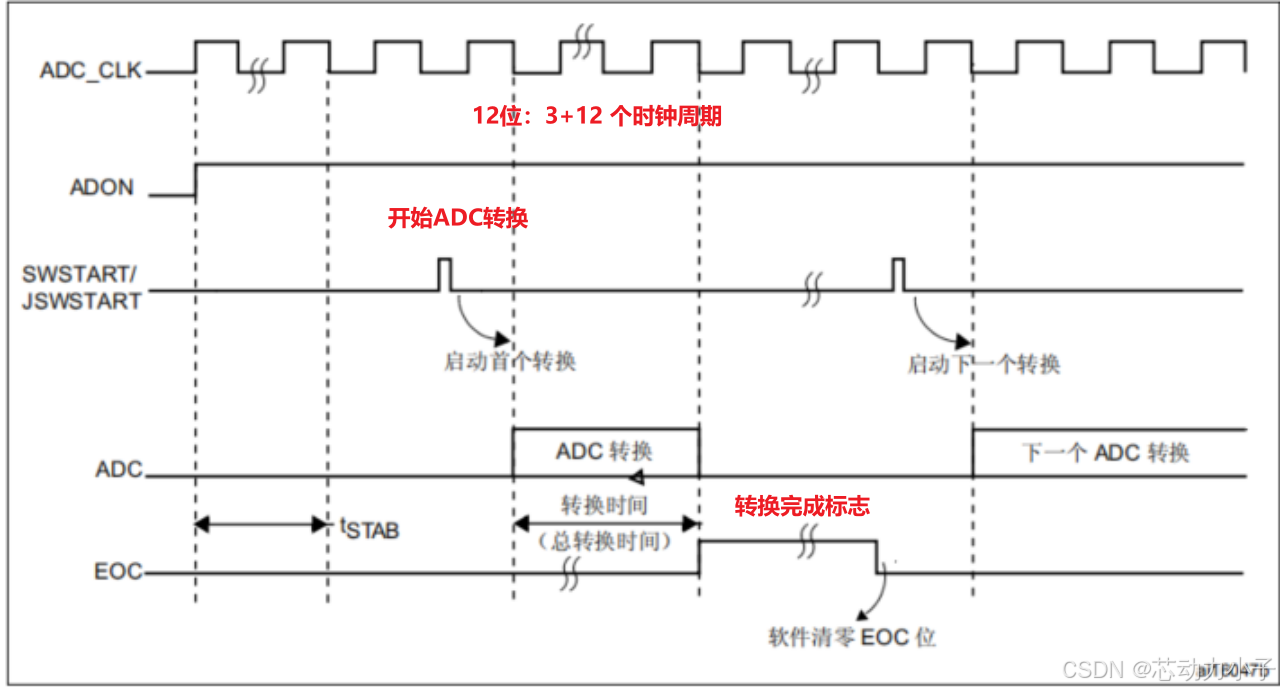

1.2.4 掃描模式、注入通道管理

1. 掃描模式

????????● ADC_CR1.SCAN 置1-選擇掃描模式;

????????● 如果將 CONT 位置 1,規則通道轉換不會在組中最后一個所選通道處停止,而是再次從第一個所選通道繼續轉換。

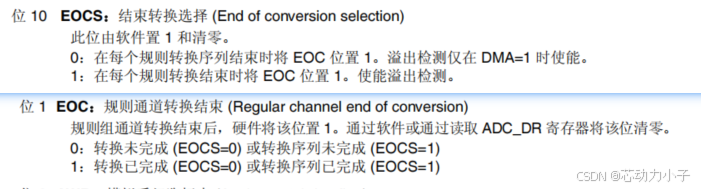

????????●?ADC_SR.EOC:規則通道轉換結束 (Regular channel end of conversion)

????????????????0:轉換未完成 (EOCS=0) 或轉換序列未完成 (EOCS=1)

????????????????1:轉換已完成 (EOCS=0) 或轉換序列已完成 (EOCS=1)

????????●?ADC_CR2.EOCS:結束轉換選擇 (End of conversion selection)

????????????????0:在每個規則組轉換序列結束時將 EOC 位置 1。溢出檢測僅在 DMA=1 時使能。

????????????????1:在每個規則通道轉換結束時將 EOC 位置 1。使能溢出檢測。

2. 注入通道管理(ADC_CR1.JAUTO)

????????

●?觸發注入-配置條件

- ?JAUTO位清零?:

ADC_CR1.JAUTO=0(禁用自動注入)。 - ?觸發源選擇?:

- ?外部觸發?:通過

ADC_CR2.JEXTSEL選擇觸發源(如定時器、外部引腳)。 - ?軟件觸發?:置位

ADC_CR2.JSWSTART=1。

- ?外部觸發?:通過

●?觸發注入-工作流程

- 啟動規則通道組轉換?:

- 外部觸發或軟件觸發規則組轉換(如定時器觸發)。

- ?觸發注入事件?:

- 在規則組轉換期間,若檢測到注入觸發信號:

- ?復位當前規則轉換?:立即停止當前規則通道的轉換。

- ?執行注入組轉換?:以單次掃描模式完成注入通道組的轉換。

- 在規則組轉換期間,若檢測到注入觸發信號:

- ?恢復規則轉換?:

- 注入組完成后,從被中斷的規則通道繼續轉換。

●?自動注入-配置條件

- ?JAUTO位置1?:

ADC_CR1.JAUTO=1(啟用自動注入)。 - ?禁用注入觸發?:必須關閉外部觸發(

ADC_CR2.JEXTEN=0)。 - ?連續模式支持?:

- 若

ADC_CR2.CONT=1,規則組和注入組將循環轉換。

- 若

●?自動注入-工作流程

- 規則組轉換完成?:

- 規則組轉換結束后,自動啟動注入組轉換。

- ?注入組轉換?:

- 按

ADC_JSQR配置的順序轉換注入通道,結果存入ADC_JDR1~4。

- 按

- ?循環轉換(CONT=1時)??:

- 注入組完成后,立即重啟規則組轉換。

1.2.5 不連續采樣模式

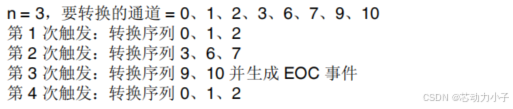

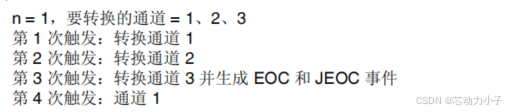

1.?規則組

? ? ? ? ADC_CR1.DISCEN -?不連續采樣模式使能

? ? ? ? ADC_CR1.DISCNUM[2:0] - n個子序列組

? ? ? ? ADC_SQR1.L[3:0] - 定義總序列長度

????????

2. 注入組

? ? ? ? ADC_CR1.JDISCEN -?不連續采樣模式使能

? ? ? ? ADC_JSQR1.L[1:0] - 定義總序列長度

????????

????????不能同時使用自動注入和不連續采樣模式。

????????不得同時為規則組和注入組設置不連續采樣模式。只能針對一個組使能不連續采樣模式。

1.3 數據對齊、通道采樣時間、快速轉換模式

1.3.0 規則/注入數據寄存器

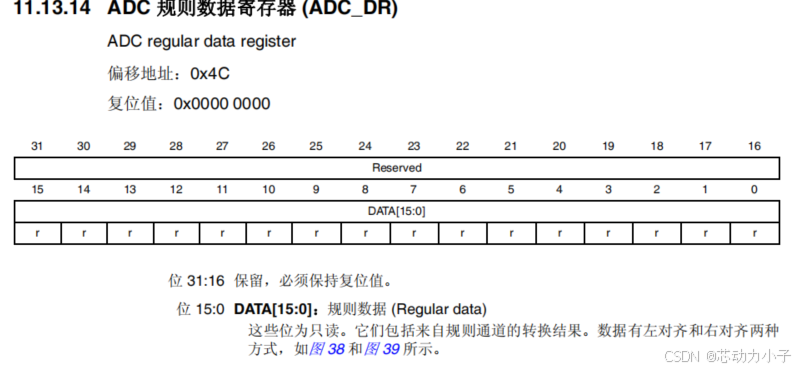

1.?規則數據寄存器(ADC_DR)

????????

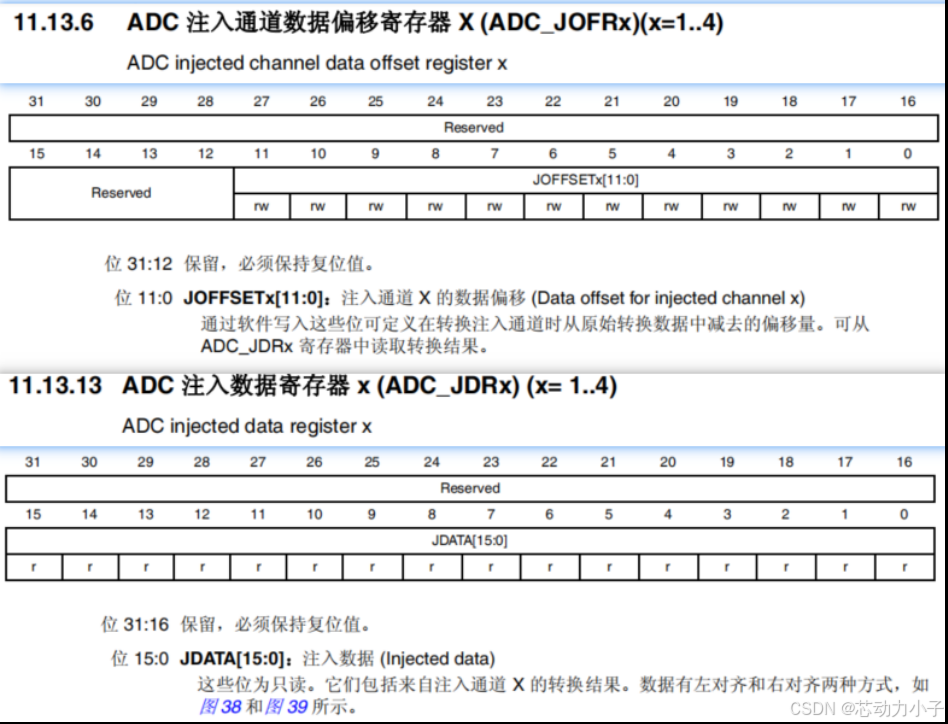

2.?注入數據寄存器(ADC_JOFRx、ADC_JDRx)

? ? ? ? ADC_JDRx?= 結果 - ADC_JOFRX (取16位補碼)

? ? ? ? SEXT位(擴展的符號值):負數填充1;正數填充0

????????

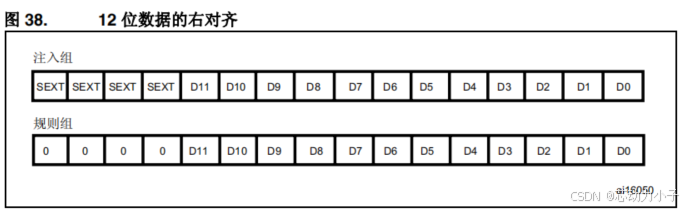

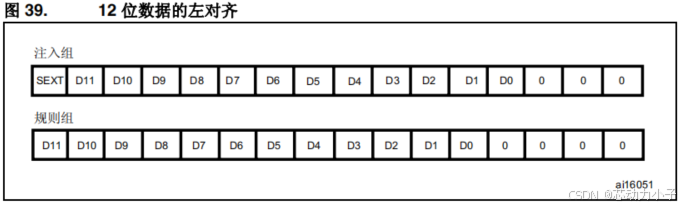

1.3.1?數據對齊ADC_CR2.ALIGN

????????ALIGN =0 右對齊(默認);=1 左對齊。

1. 右對齊(參考1.3.0)

????????

2. 左對齊(參考1.3.0)

????????

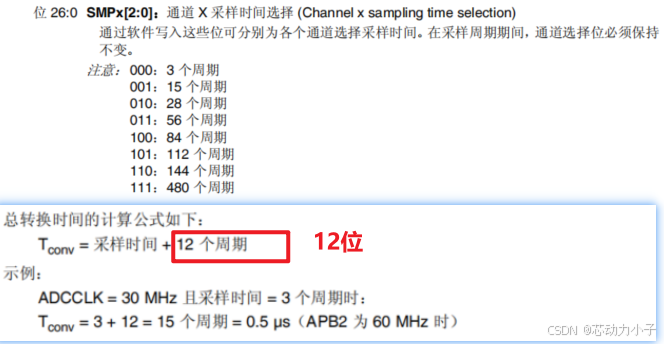

1.3.2?通道采樣時間與轉換時間

? ? ? ? 通過ADC_SMPR1、ADC_SMPR2的SMPx[2:0]控制各個通道的采樣周期。

????????

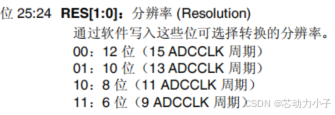

1.3.3?快速轉換模式(降低精度轉換)ADC_CR1.RES?

????????可通過降低 ADC 分辨率來執行快速轉換。下列為轉換時間。

????????

1.4 外部觸發和觸發極性

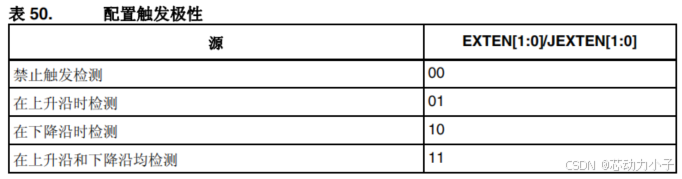

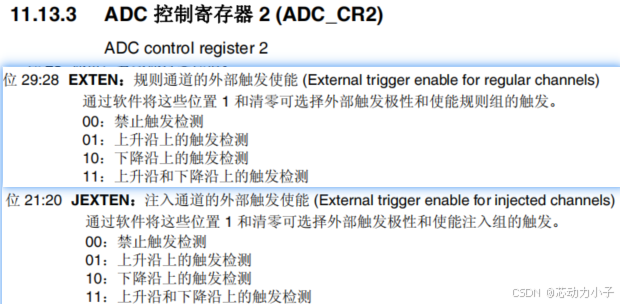

1.4.1?外部觸發極性

????????

????????

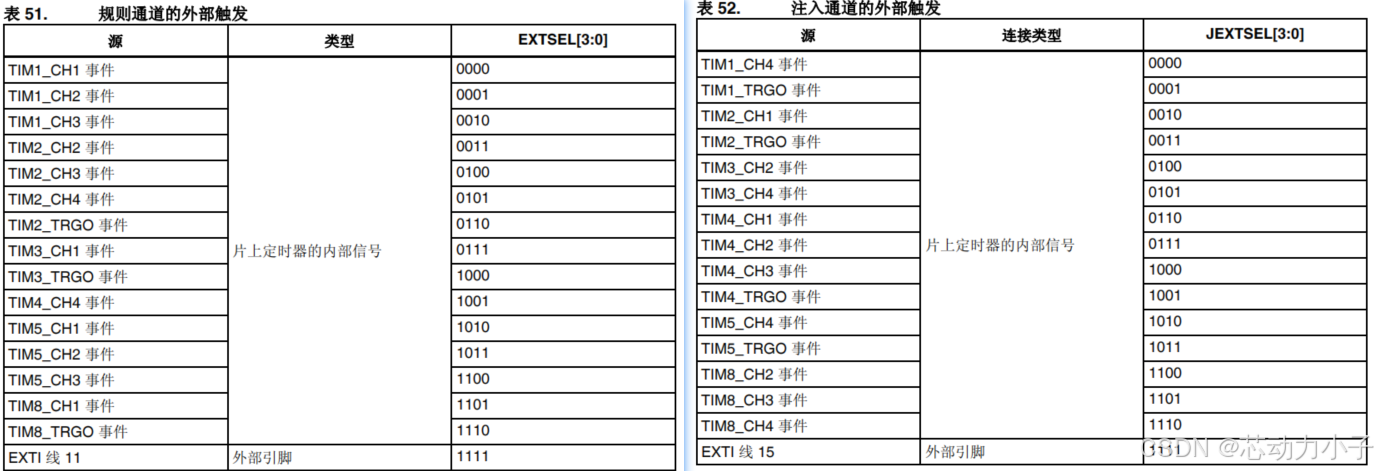

1.4.2. 外部觸發條件

?

1.5 ADC數據采集方式(三種)

1.5.1?使用 DMA(ADC_CR2.DMA 置1)

1.?配置步驟

- 使能DMA:置位

ADC_CR2寄存器中的DMA位。 - 配置DMA控制器:設置目標地址(內存緩沖區)和傳輸次數(

NDTR計數器)。

2.?數據丟失(溢出)處理

- 溢出標志?:若數據未及時讀取且DMA未傳輸,

ADC_SR寄存器中的OVR位會置1,并可能觸發中斷(需使能OVRIE位)。 - ?溢出后果?:

- DMA傳輸被禁止,后續DMA請求被忽略。

- 正在進行的規則轉換被中止,后續規則觸發無效。

- ?恢復步驟?:

- ?重新初始化DMA?:調整目標地址和

NDTR計數器。 - ?清除溢出標志?:將

ADC_SR中的OVR位清零。 - ?重啟轉換?:觸發ADC開始新的轉換。

- ?重新初始化DMA?:調整目標地址和

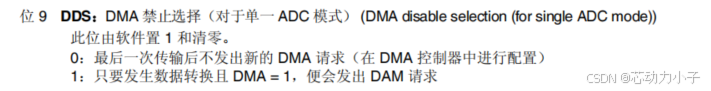

3.?DMA傳輸結束

- 若

ADC_CR2的DDS位為0,最后一次傳輸后停止DMA請求,需手動復位DMA位(先寫0再寫1)重啟。

- 若

DDS位為1,DMA繼續生成請求,支持雙緩沖區循環模式(適合連續流數據)。

1.5.2?在不使用 DMA 的情況下管理轉換序列

1.?配置步驟

- 禁止DMA:

ADC_CR2的DMA位清零。 - 使能每次轉換結束中斷:置位

ADC_CR1的EOCS位為1(EOC在每次轉換結束時置1)。

- ?溢出處理?:

- 與DMA模式相同:需手動清除

OVR位并重啟轉換。

- 與DMA模式相同:需手動清除

2.?配置步驟

- ?啟動轉換序列?:觸發ADC開始轉換。

- ?等待EOC標志?:每次轉換結束,

EOC位置1。 - ?讀取數據?:從

ADC_DR讀取當前通道數據。 - ?處理溢出?(若發生):清除

OVR位并重啟轉換。

1.5.3?在不使用 DMA 和溢出檢測的情況下進行轉換

- 禁止DMA:

ADC_CR2的DMA位清零。 - 僅在序列結束置位EOC:

EOCS位清零。 - 禁用溢出檢測:默認情況下溢出檢測已關閉。

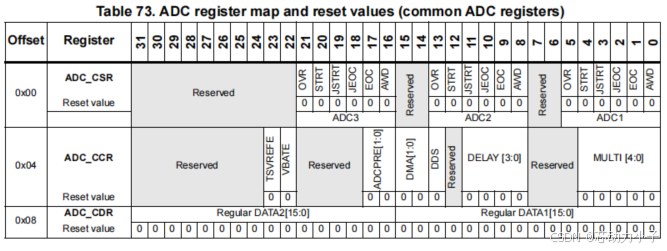

1.6?多重 ADC 模式

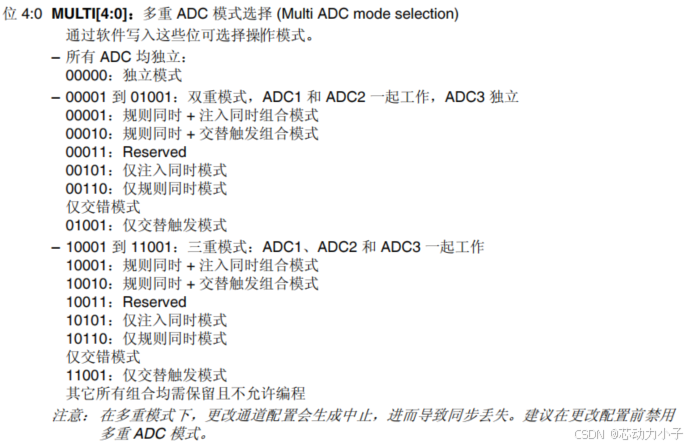

1.6.1 多重 ADC 模式介紹(ADC_CCR.MULTI[4:0])

????????

1. 四種模式(也可以組合使用)

????????● 規則同時模式

2.?多重ADC框圖

注: 1.?盡管 ADC2 和 ADC3 上存在外部觸發,但它們并未顯示在此圖中。

? ? ? ? 2.?在雙重 ADC 模式下,不存在 ADC3 從器件部分。

? ? ? ? 3.?在三重 ADC 模式下,ADC 通用數據寄存器 (ADC_CDR) 包含 ADC1、ADC2 和 ADC3 的規則轉換數據。按照所選的存儲順序使用全部 32 個寄存器位。在雙重 ADC 模式下,ADC 通用數據寄存器 (ADC_CDR) 包含 ADC1 和 ADC2 的規則轉換數據。使用全部32個寄存器位。

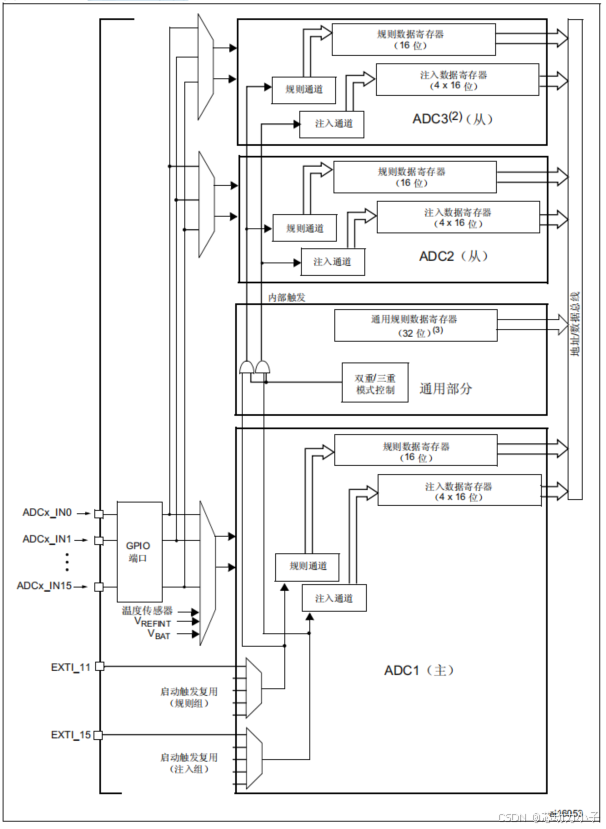

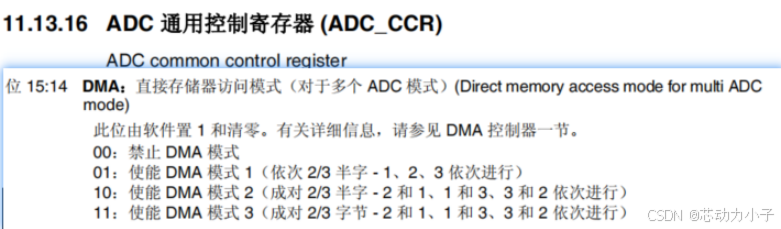

1.6.2 多重模式下DMA模式(ADC_CCR.DMA[1:0])(三種)

????????

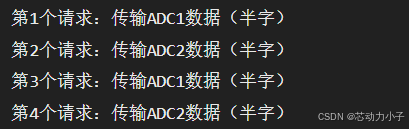

1. DMA模式1(半字傳輸)

- 核心特性

?傳輸單位?:每個DMA請求傳輸 ?一個半字(16位)?,對應單個ADC的轉換結果。

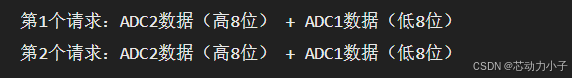

觸發條件?:每完成一次ADC轉換(一個數據項可用)時觸發DMA請求。 - 數據傳輸順序

· 兩重模式

請求順序為 ?ADC1→ADC2→ADC1→ADC2...?,依次循環。

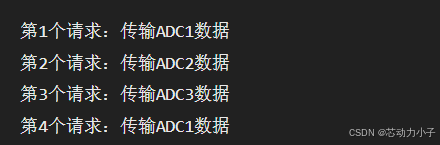

· 三重模式

請求順序為 ?ADC1→ADC2→ADC3→ADC1→ADC2→ADC3...?,依次循環。

- 應用場景

規則同時模式?:需要逐個讀取多ADC數據的場景。

示例?:多通道溫度監測,ADC1、ADC2、ADC3分別采集不同區域的溫度值。

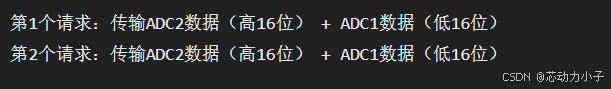

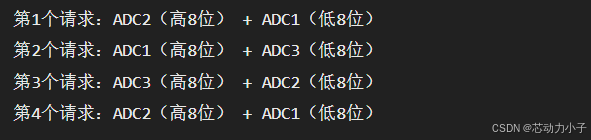

2. DMA模式2(字傳輸)

- 核心特性

?傳輸單位?:每個DMA請求傳輸 ?一個字(32位)?,包含 ?兩個半字?(兩個ADC的轉換結果)。

觸發條件?:每完成兩次ADC轉換(兩個數據項可用)時觸發DMA請求。 - 數據傳輸順序

?· 兩重模式

每個字的高16位存儲 ?ADC2數據,低16位存儲 ?ADC1數據。

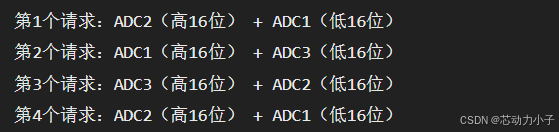

· 三重模式

按 ?固定組合順序? 傳輸三個ADC的數據,每個字包含兩個半字:

- 應用場景

交替模式?:需要同時讀取兩個ADC數據的場景,例如電機控制中電流和電壓同步采集。

示例?:雙重交替模式下,ADC1采集電流信號,ADC2采集電壓信號,每個DMA請求同時傳輸兩者數據。

3. DMA模式3(字節傳輸)

- 核心特性

?傳輸單位?:每個DMA請求傳輸 ?兩個字節(8位×2)?,適用于 ?6位或8位分辨率? 的ADC。

觸發條件?:每完成兩次ADC轉換(兩個數據項可用)時觸發DMA請求。 - 數據傳輸順序

?· 兩重模式

每個DMA請求的高8位存儲 ?ADC2數據,低8位存儲 ?ADC1數據。

· 三重模式

數據傳輸順序與DMA模式2相似,但以字節為單位:

- 應用場景

規則同時模式?:適用于6位或8位ADC的快速數據采集,簡單傳感器信號(如光敏電阻)。

示例?:ADC1和ADC2分別采集兩個低分辨率傳感器的開關狀態。

1.7?多重 ADC 模式

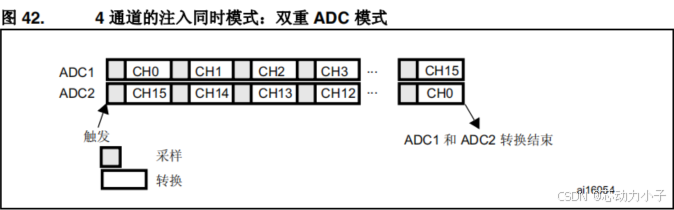

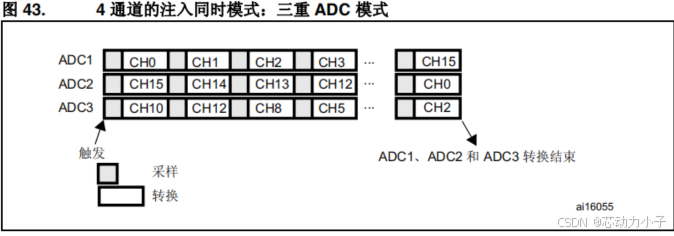

1.7.1 注入同時模式

?

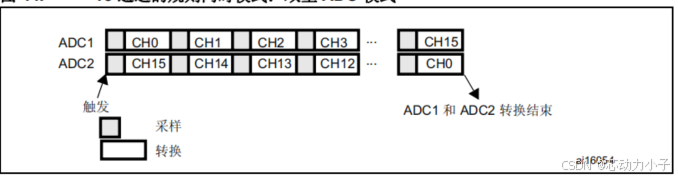

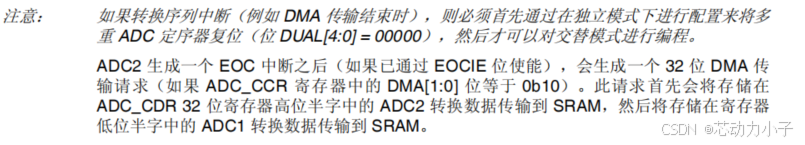

1.7.2 規則同時模式(ADC_CDR)

ADC_CDR:適用于雙重和三重模式的 ADC 通用規則數據寄存器

注:必須禁止注入轉換。

????????

1.?雙重ADC

- 觸發條件?:當任意一個ADC(ADC1或ADC2)完成一次轉換時,觸發DMA請求。

- ?DMA配置?:

- 設置

ADC_CCR寄存器的DMA[1:0] = 0b10。 - 生成 ?單次32位DMA傳輸請求,將 ?ADC2和ADC1的轉換數據? 組合傳輸。

- 設置

- ?數據格式?:

- 32位數據寄存器

ADC_CDR的高16位存儲 ?ADC2的轉換結果,低16位存儲 ?ADC1的轉換結果。 - 示例:若ADC1轉換值為

0x1234,ADC2轉換值為0x5678,則ADC_CDR = 0x56781234。

- 32位數據寄存器

- ?傳輸流程?:

- DMA將

ADC_CDR高16位(ADC2數據)寫入SRAM目標地址。 - DMA將

ADC_CDR低16位(ADC1數據)寫入下一個SRAM地址。 - 重復直到所有通道轉換完成。

- DMA將

? ? ? ?中斷生成:

?????????EOC中斷?:當 ?所有常規通道均完成轉換? 后,觸發EOC(轉換結束)中斷。

? ? ? ? ?中斷使能?:需在 ?至少一個ADC接口? 的 ADC_CR1 寄存器中使能 EOCIE 位。

????????

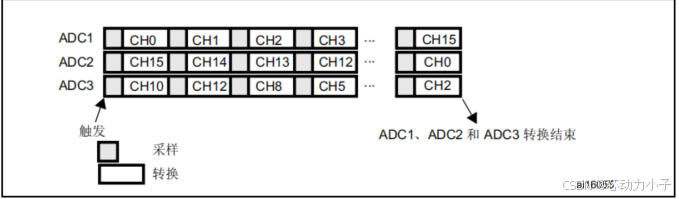

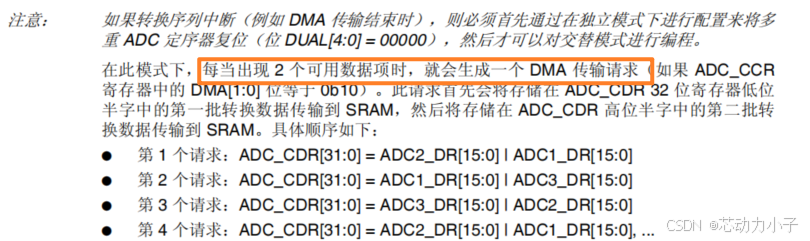

2. 三重ADC

- 觸發條件?:當任意一個ADC(ADC1、ADC2或ADC3)完成一次轉換時,觸發DMA請求。

- ?DMA配置?:

- 設置

ADC_CCR寄存器的DMA[1:0] = 0b01。 - 生成 ?三次32位DMA傳輸請求,分別傳輸 ?ADC1、ADC2、ADC3的轉換數據。

- 設置

- ?數據格式?:

- 每個ADC的轉換結果存儲在獨立的

ADC_CDR寄存器中。 - 傳輸順序:先ADC1→再ADC2→最后ADC3。

- 每個ADC的轉換結果存儲在獨立的

- ?傳輸流程?:

- 第一次DMA傳輸:ADC1數據寫入SRAM地址A。

- 第二次DMA傳輸:ADC2數據寫入地址A+4(32位對齊)。

- 第三次DMA傳輸:ADC3數據寫入地址A+8。

- 重復直到所有通道轉換完成。

-

中斷生成?

EOC中斷?:當 ?所有常規通道均完成轉換? 后,觸發EOC(轉換結束)中斷。

中斷使能?:需在 ?至少一個ADC接口? 的ADC_CR1寄存器中使能EOCIE位。

????????

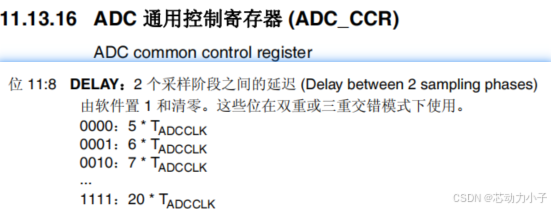

1.7.3 交替模式

此模式只能用于規則組(通常為一個通道)。外部觸發源來自 ADC1 的規則通道多路復用器。

ADC_CCR.DELAY[3:0] - 設置交替模式下的采樣時間。

????????

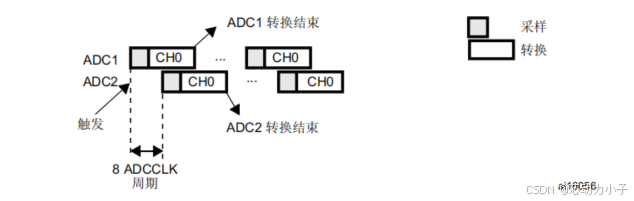

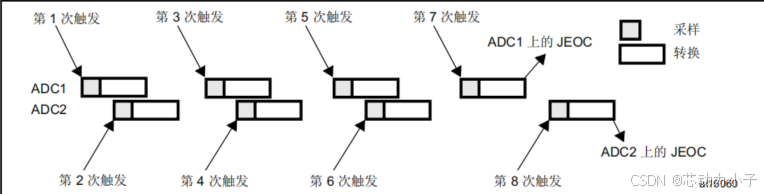

1.?雙重 ADC 模式

????????ADC1立即啟動,經過幾個ADC時鐘周期延遲后ADC2啟動。

? ? ? ? 只有一共ADC能夠對輸入信號采樣,即DELAY設置的延遲時間小于采用時間時,延遲時間=采樣時間+2個ADC_CLK時鐘周期。如果 ADC1 和 ADC2 上的 CONT 位均置 1,則這兩個 ADC 所選規則通道會連續進行轉換。

????????

????????

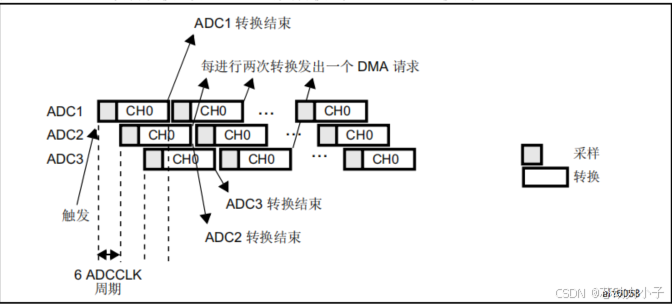

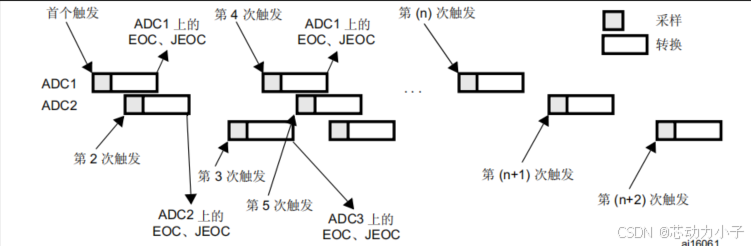

2.?三重 ADC 模式

????????ADC1 立即啟動,經過幾個ADC時鐘周期延遲后ADC2啟動,在ADC2轉換經過幾個ADC時鐘周期的延遲后ADC3啟動。

????????

????????

1.7.4?交替觸發模式

????????只能用于注入組。外部觸發源來自 ADC1 的注入組多路復用器。

????????

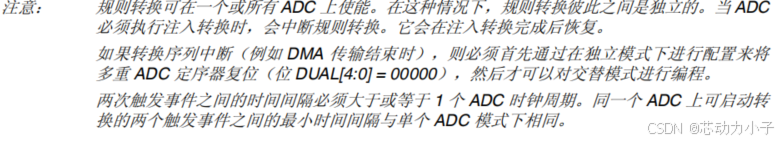

1.?雙重 ADC 模式

????????● 發生第一次觸發時,將轉換ADC1中注入組的所有通道

????????????????當組中的所有注入 ADC1 通道都轉換完成后,會生成一個 JEOC 中斷(如果已使能)

????????● 發生第二次觸發時,將轉換ADC2中注入組的所有通道

????????????????當組中的所有注入 ADC2 通道都轉換完成后,會生成一個 JEOC 中斷(如果已使能)

????????

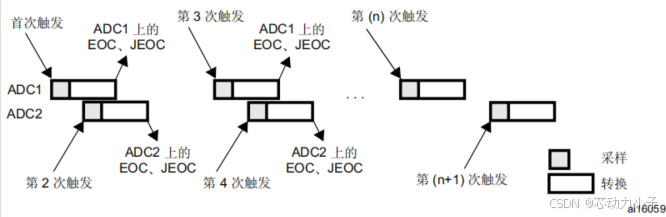

如果使能 ADC1 和 ADC2 的注入不連續采樣模式:

????????● 發生第一次觸發時,將轉換第一個注入 ADC1 通道

????????● 發生第二次觸發時,將轉換第一個注入 ADC2 通道

????????● 發生第三次觸發時,將轉換第二個注入 ADC1 通道

????????● 發生第四次觸發時,將轉換第二個注入 ADC2 通道

????????● ……

????????當組中的所有注入 ADC1 通道都轉換完成后,會生成一個 JEOC 中斷(如果已使能)

????????當組中的所有注入 ADC2 通道都轉換完成后,會生成一個 JEOC 中斷(如果已使能)

????????

2.?三重 ADC 模式

????????● 發生第一次觸發時,將轉換ADC1中注入組的所有通道

????????????????當組中的所有注入 ADC1 通道都轉換完成后,會生成一個 JEOC 中斷(如果已使能)

????????● 發生第二次觸發時,將轉換ADC2中注入組的所有通道

????????????????當組中的所有注入 ADC2 通道都轉換完成后,會生成一個 JEOC 中斷(如果已使能)

????????● 發生第三次觸發時,將轉換ADC3中注入組的所有通道

????????????????當組中的所有注入 ADC3 通道都轉換完成后,會生成一個 JEOC 中斷(如果已使能)

????????

1.7.5?混合型規則/注入同時模式

可以中斷規則組的同時轉換,然后開始注入組的同時轉換。

1.7.6?規則同時 + 交替觸發組合模式

????????可以中斷規則組的同時轉換,然后開始注入組的交替觸發轉換。

????????注入事件后立即開始注入交替轉換。當規則轉換處于運行狀態時,為確保在注入轉換后實現同步,所有的(主/從) ADC規則轉換均將停止,并會在注入轉換結束時得以恢復運行。

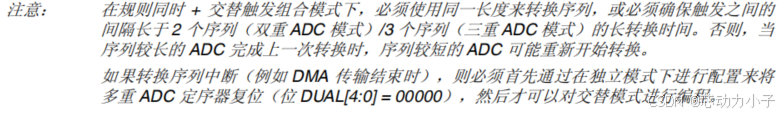

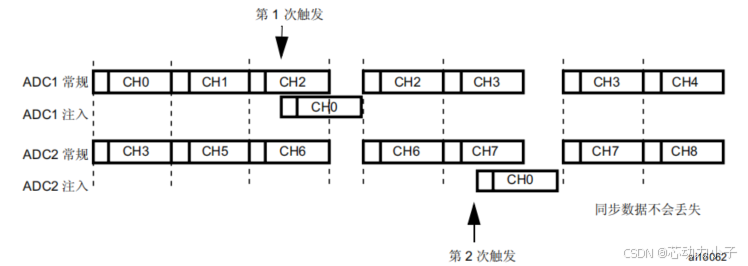

????????

????????

1.8?ADC中斷

| 中斷事件 | 標志位 | 使能控制位 | 觸發條件 |

|---|---|---|---|

| 規則組轉換結束 | EOC | EOCIE | 規則通道組所有通道轉換完成(單通道或掃描模式) |

| 注入組轉換結束 | JEOC | JEOCIE | 注入通道組所有通道轉換完成(需外部觸發或自動注入) |

| 模擬看門狗狀態位置 1 | AWD | AWDIE | 輸入電壓超過模擬看門狗閾值(高 / 低閾值由 ADC_HTR 和 ADC_LTR 定義) |

| 數據溢出(Overrun) | OVR | OVRIE | 數據寄存器(ADC_DR 或 ADC_JDRx)未及時讀取,新數據覆蓋舊值 |

2.?基于HAL庫配置ADC外設

2.1?CubeMX配置ADC外設

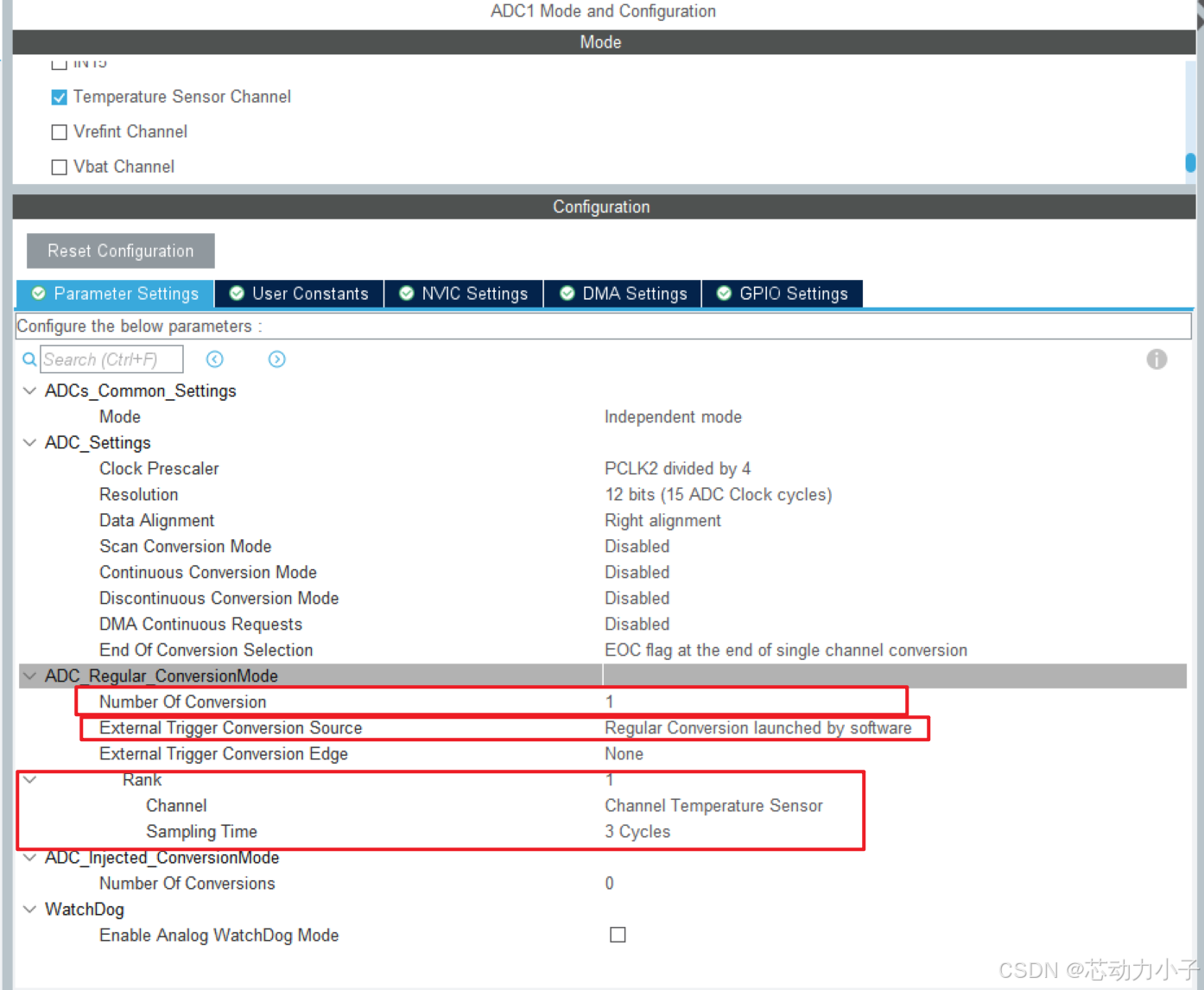

2.1.1 單通道采集內部溫度傳感器

?????????

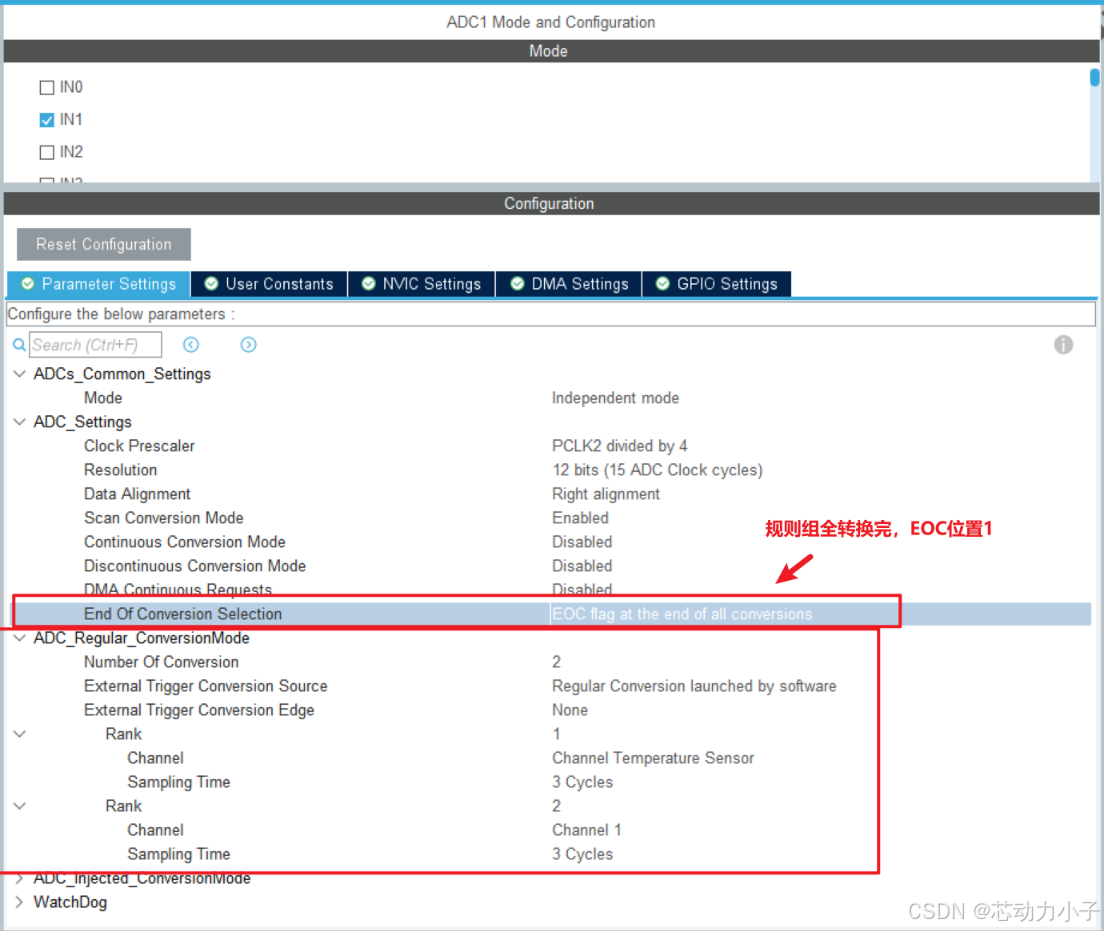

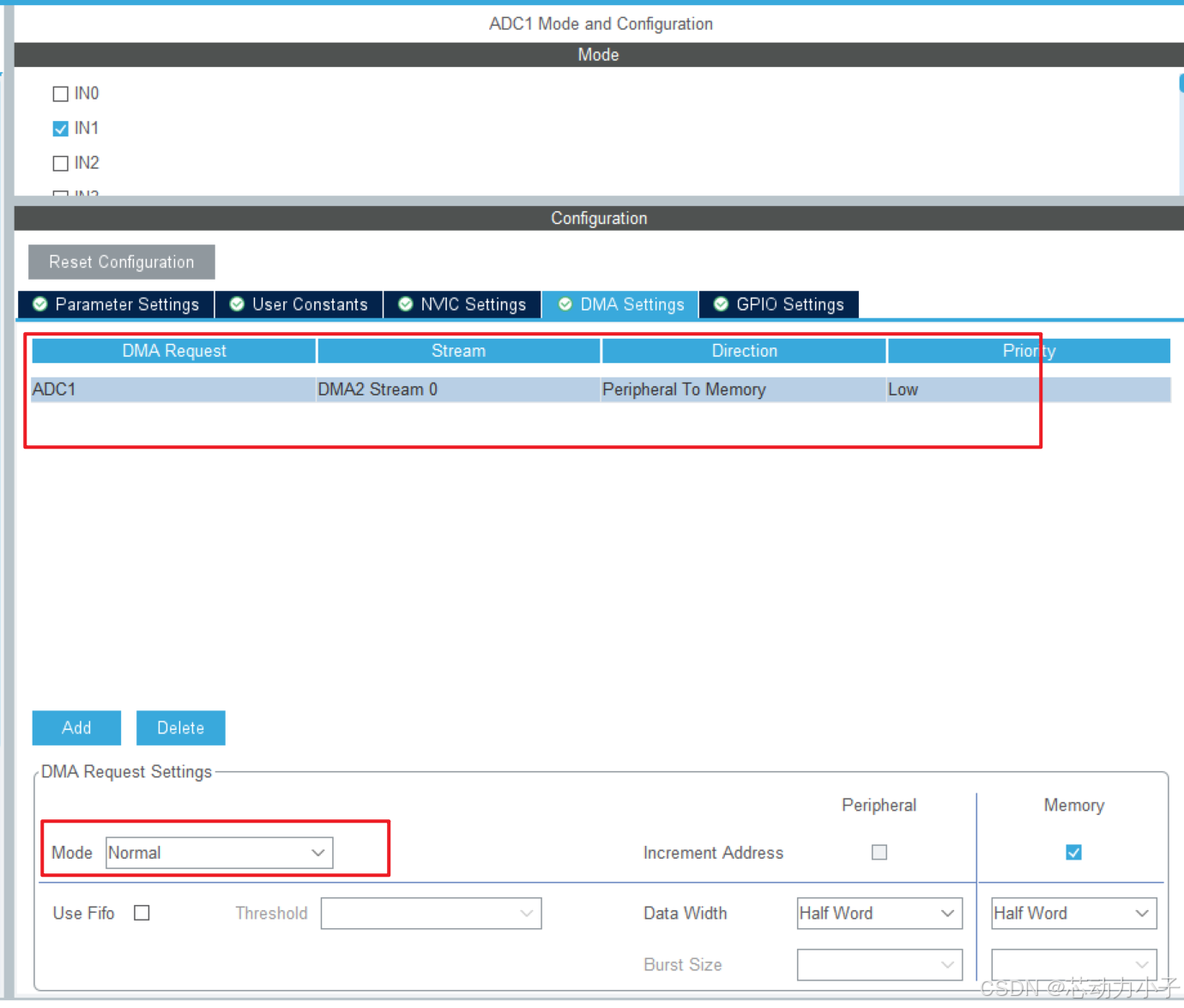

2.1.2 多通道ADC采集(單次DMA請求)

????????

????????

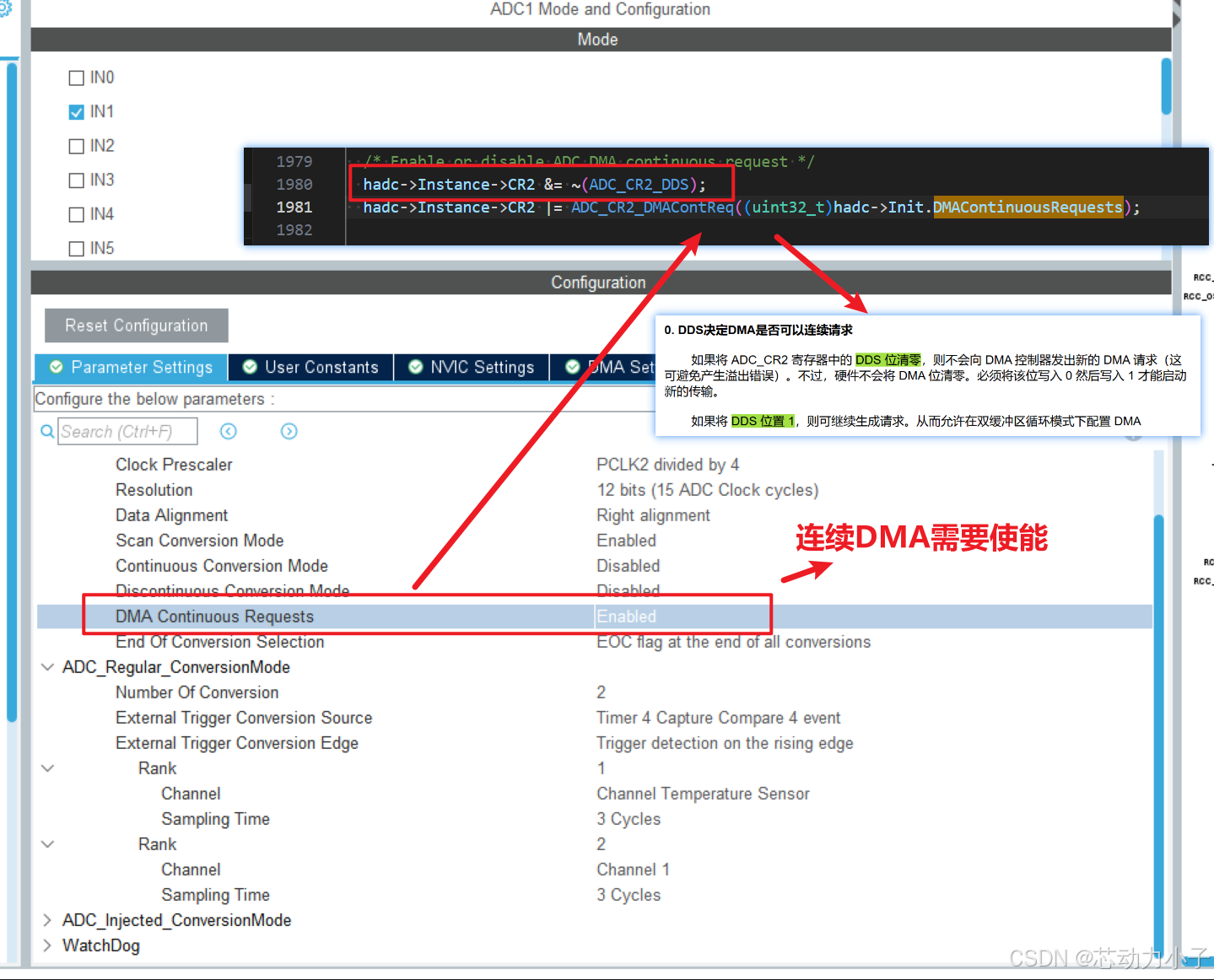

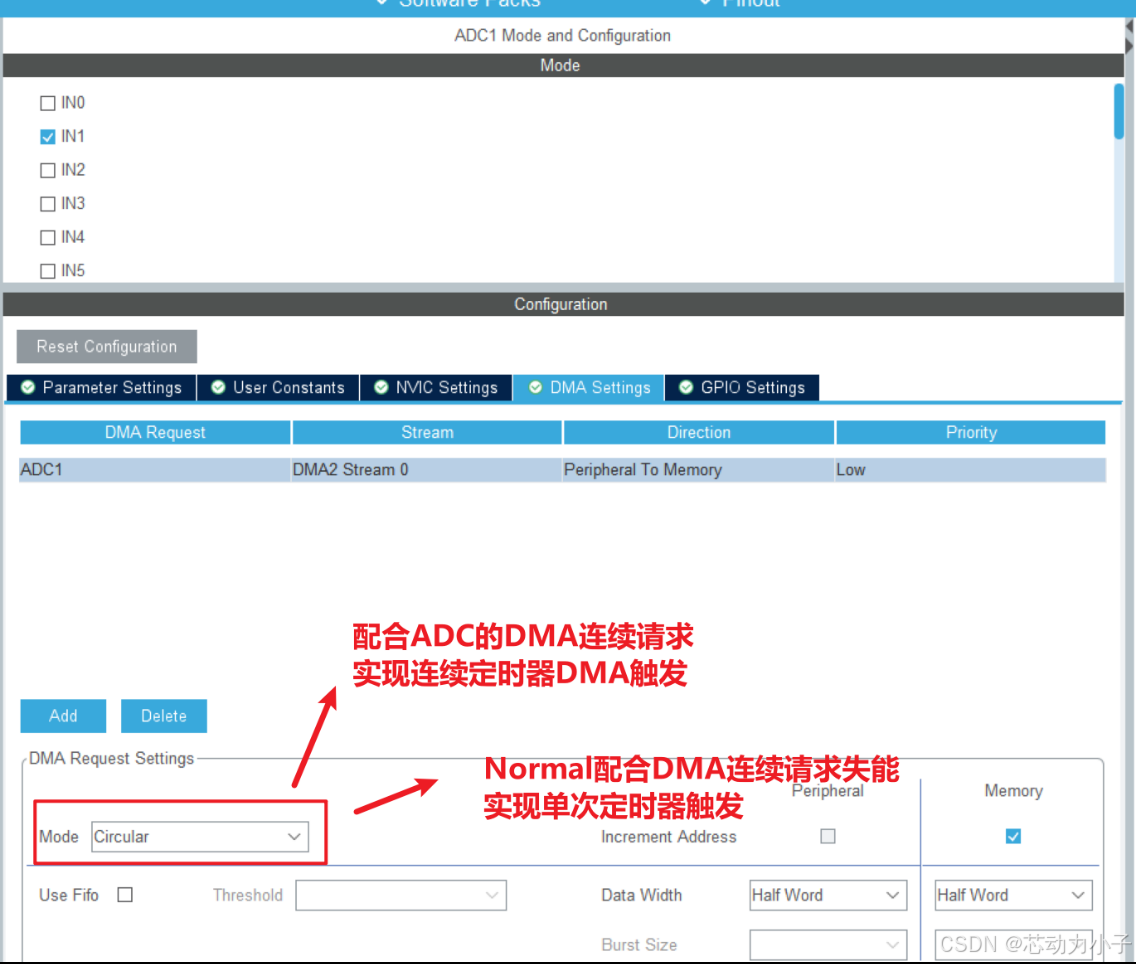

2.1.3 多通道ADC采集 (定時器觸發ADC采集(單次/連續))

?????????

????????

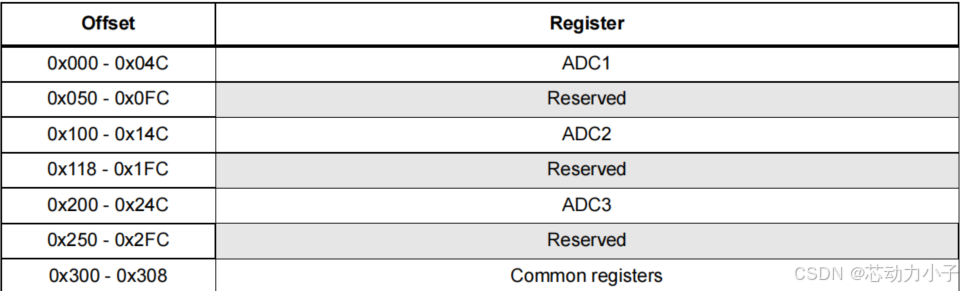

2.2?基本定時器寄存器基地址

????????

2.3?基本定時器寄存器

????????

????????

3. ADC實踐

本次實踐分為三個部分:單通道采集芯片內部溫度傳感器(ADC1_ch16);利用軟件觸發單次觸發多通道DMA ADC采集;利用定時器單次/連續觸發多通道DMA ADC采集。

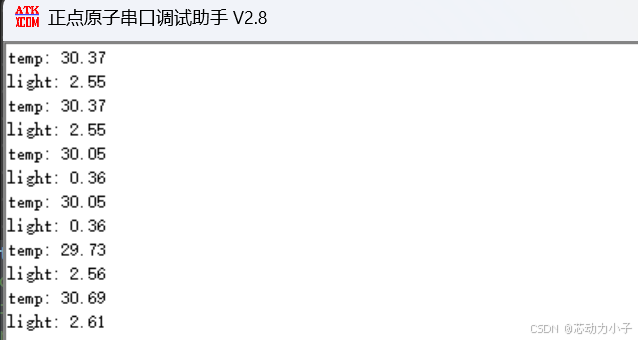

多通道是內部溫度傳感器(ADC1_ch16)、光敏傳感器(ADC1_ch1)

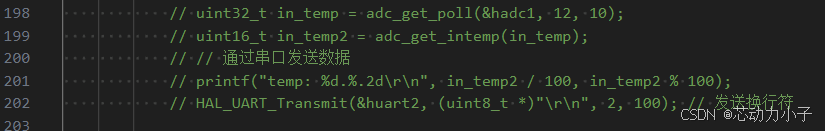

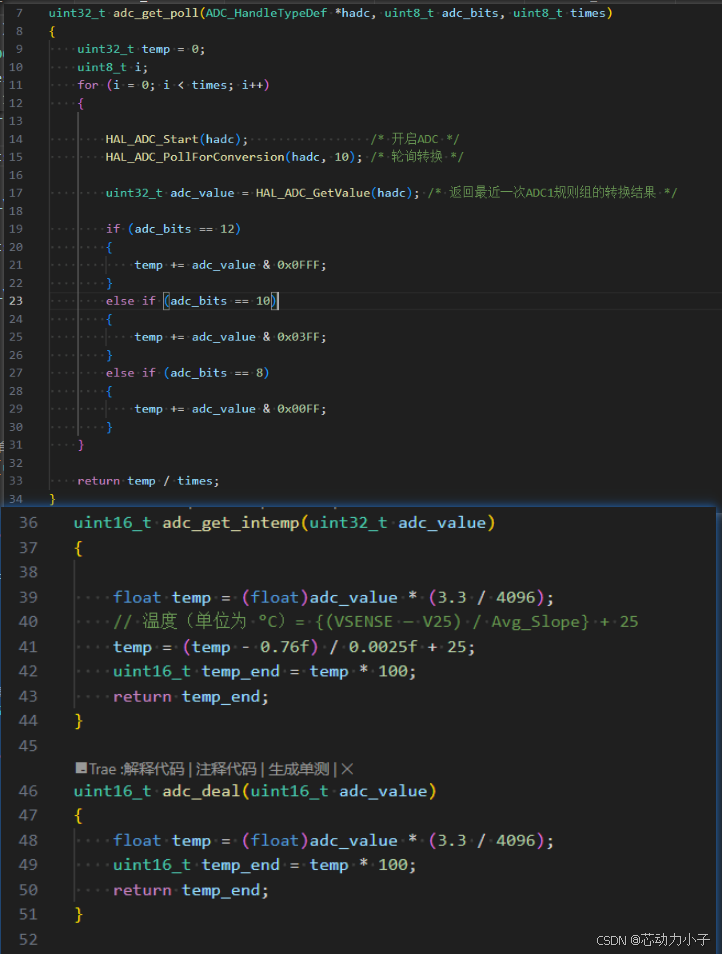

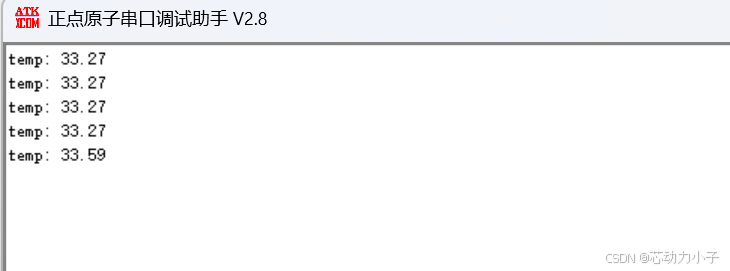

3.1 單通道采集內部溫度傳感器(查詢)

- main函數

- 功能函數

- 實踐結果

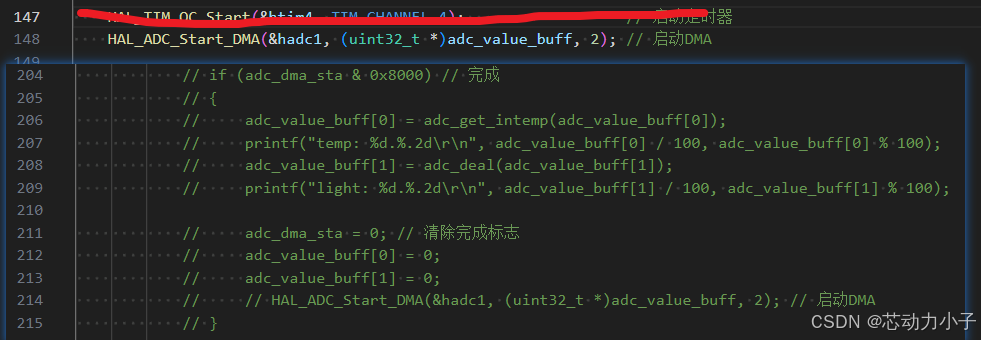

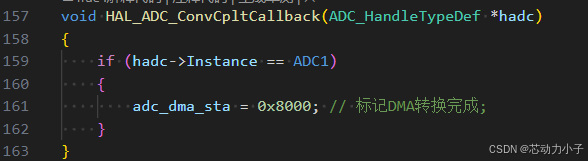

?3.2 多通道ADC采集(單次DMA)

- main函數

- 中斷回調函數

- 實踐結果

????????

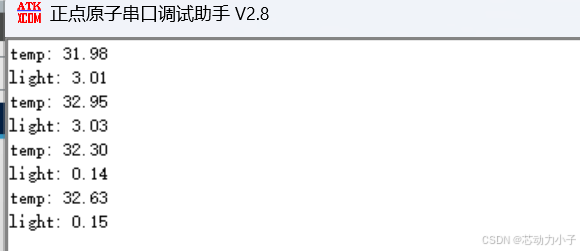

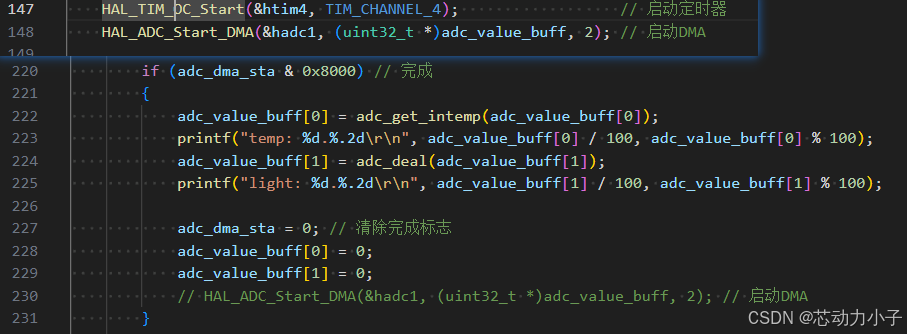

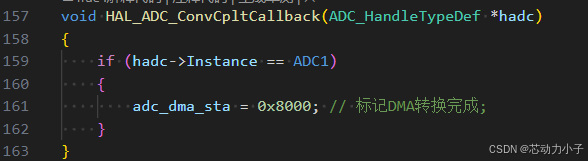

?3.3 多通道ADC采集(定時器單次/連續觸發DMA)

- main函數

- 中斷回調函數

- 實踐結果

4.?本文的工程文件下載鏈接

工程Github下載鏈接:https://github.com/chipdynkid/MCU-DL-STM32

(國內)工程Gitcode下載鏈接https://gitcode.com/chipdynkid/MCU-DL-STM32

)

)