接觸fpga一段時間,也能寫點跑點吧……試試系統地康康呢~這個需要耐心但是回報巨大的工作。正原子&&小梅哥

15_語法篇:Verilog高級知識點_嗶哩嗶哩_bilibili

1Verilog基礎

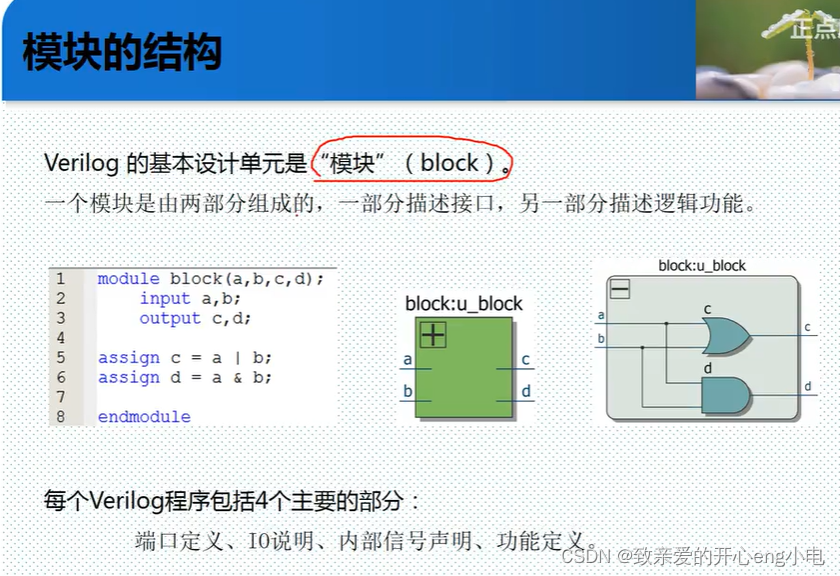

Verilog程序框架:模塊的結構

類比:c語言的基礎單位是函數

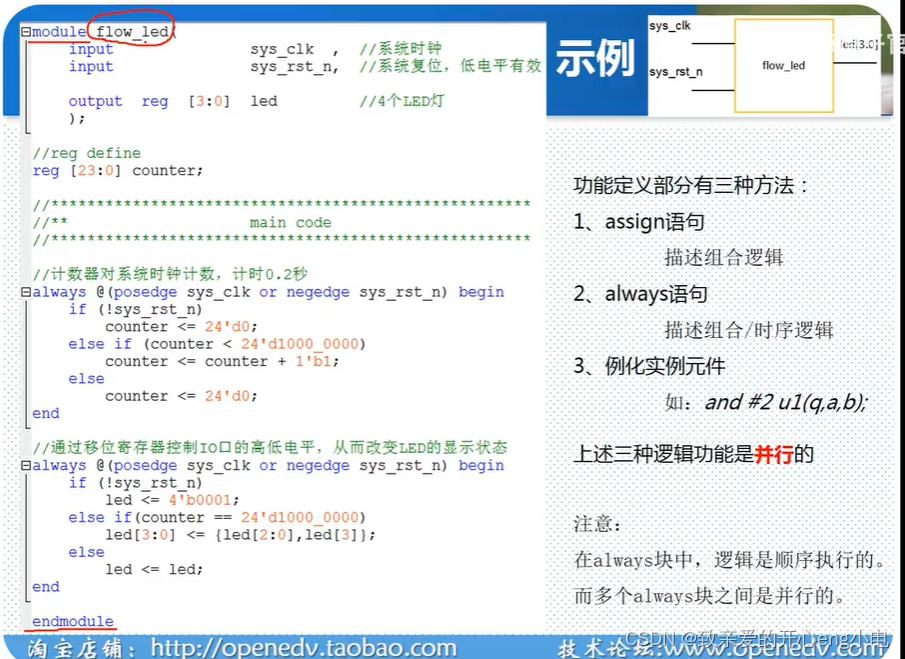

一個流水燈實驗的example

counter即是內部信號聲明

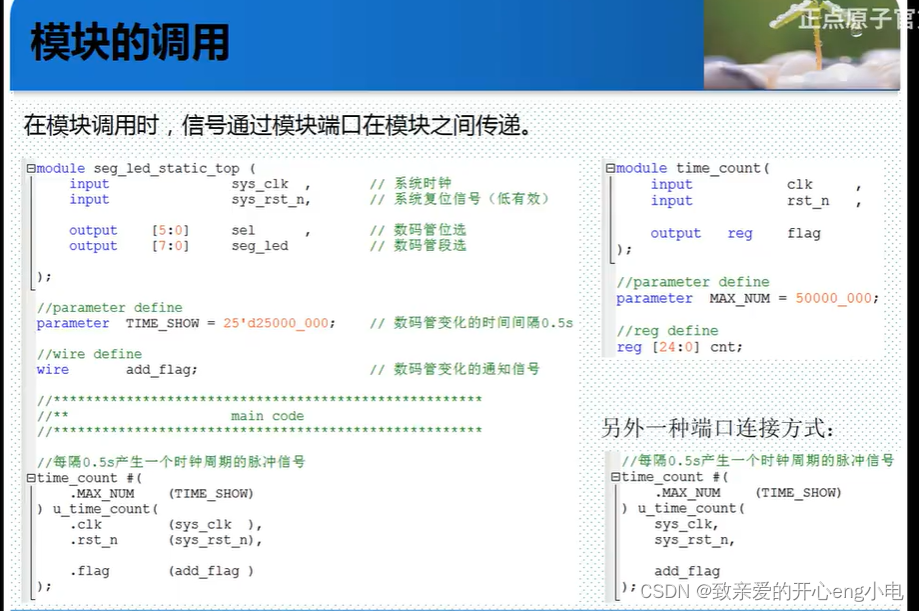

模塊的調用

例化中的參數傳遞問題

在Verilog中,#(.PARAM_NAME(VALUE))是一種參數化實例化(parameterized instantiation)語法,用于在實例化模塊時傳遞參數。具體來說,它用于在實例化某個模塊時,覆蓋該模塊中定義的默認參數值。

假設我們有一個模塊Timer,其定義如下:

module Timer #(parameter MAX_NUM = 100) (

? ? input wire clk,

? ? input wire reset,

? ? output reg [7:0] count

);

? ? always @(posedge clk or posedge reset) begin

? ? ? ? if (reset)

? ? ? ? ? ? count <= 0;

? ? ? ? else if (count < MAX_NUM)

? ? ? ? ? ? count <= count + 1;

? ? ? ? else

? ? ? ? ? ? count <= 0;

? ? end

endmodule

在這個模塊中,MAX_NUM是一個參數,默認值為100。如果我們在實例化這個模塊時,希望將MAX_NUM的值改為某個不同的值,例如TIME_SHOW,我們可以使用參數化實例化語法來實現。

module TopModule (

? ? input wire clk,

? ? input wire reset,

? ? output wire [7:0] timer_count

);

? ? // Parameterized instantiation

? ? Timer #(.MAX_NUM(TIME_SHOW)) timer_instance (

? ? ? ? .clk(clk),

? ? ? ? .reset(reset),

? ? ? ? .count(timer_count)

? ? );

endmodule

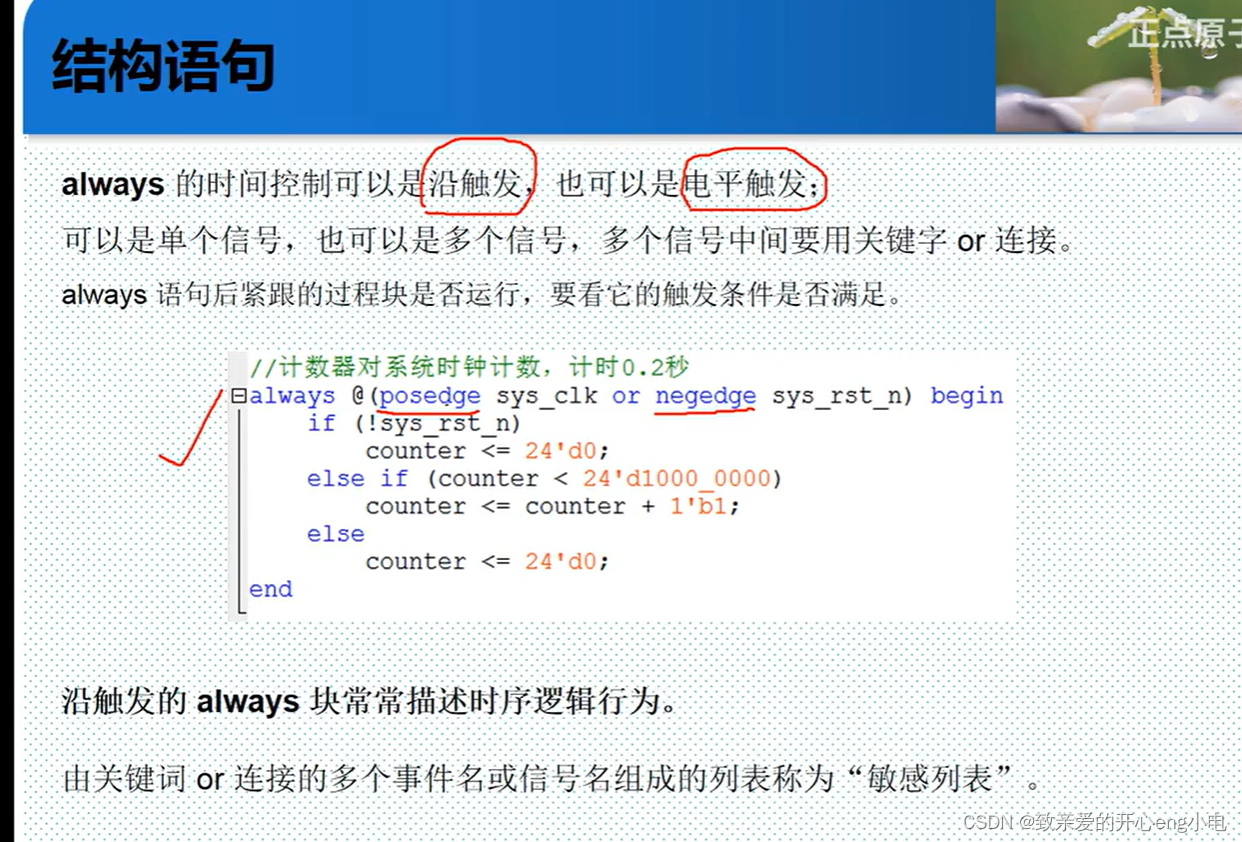

結構語句

initial

#20:延時20個單位的時間

延時了20個單位后又延時了10個單位又延時了30個單位……

timescale

時間單位是通過timescale指令設置的。在你的Verilog文件中添加適當的timescale指令,可以明確定義時間單位和時間精度,從而確定延時語句(如#20)的具體含義。

`timescale 1ns / 1ps指令設置時間單位為1納秒,時間精度為1皮秒。

#10表示延時10納秒。

always

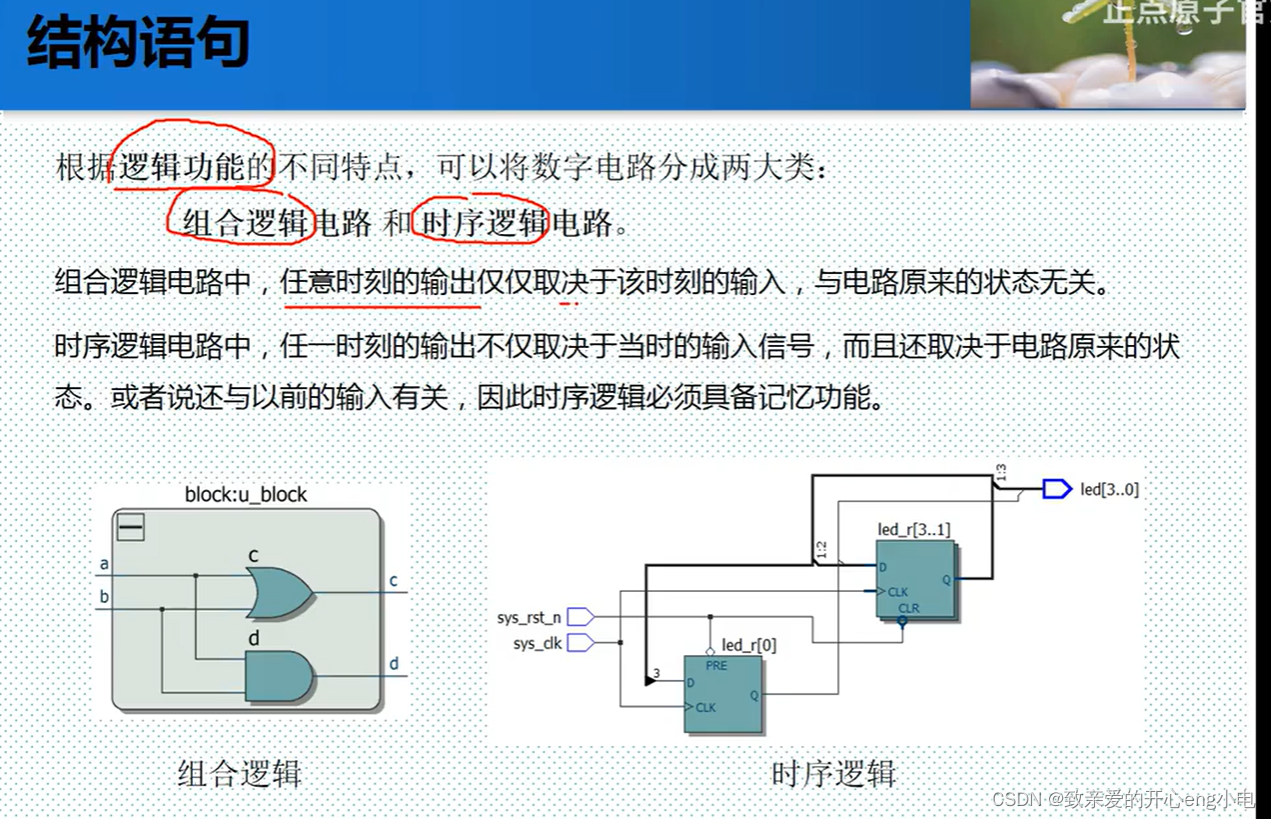

組合邏輯vs時序邏輯

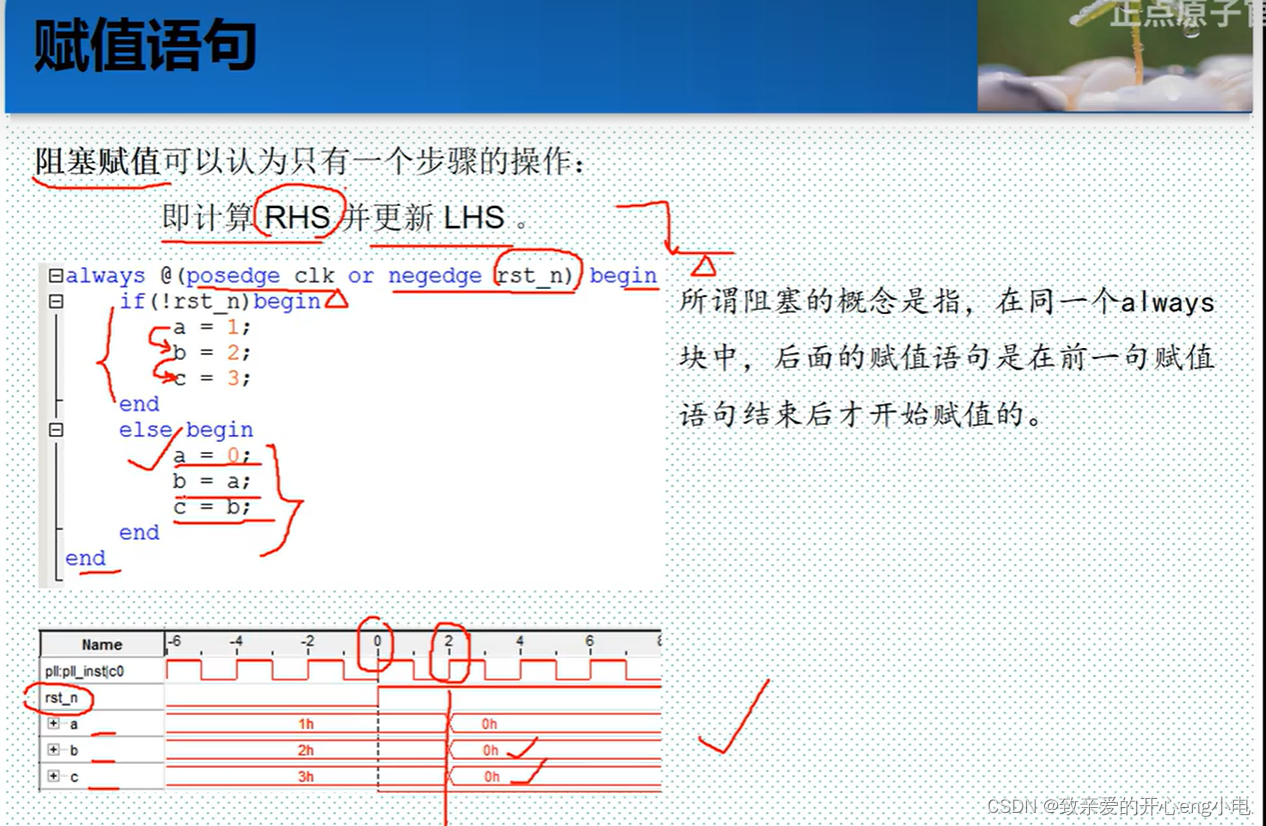

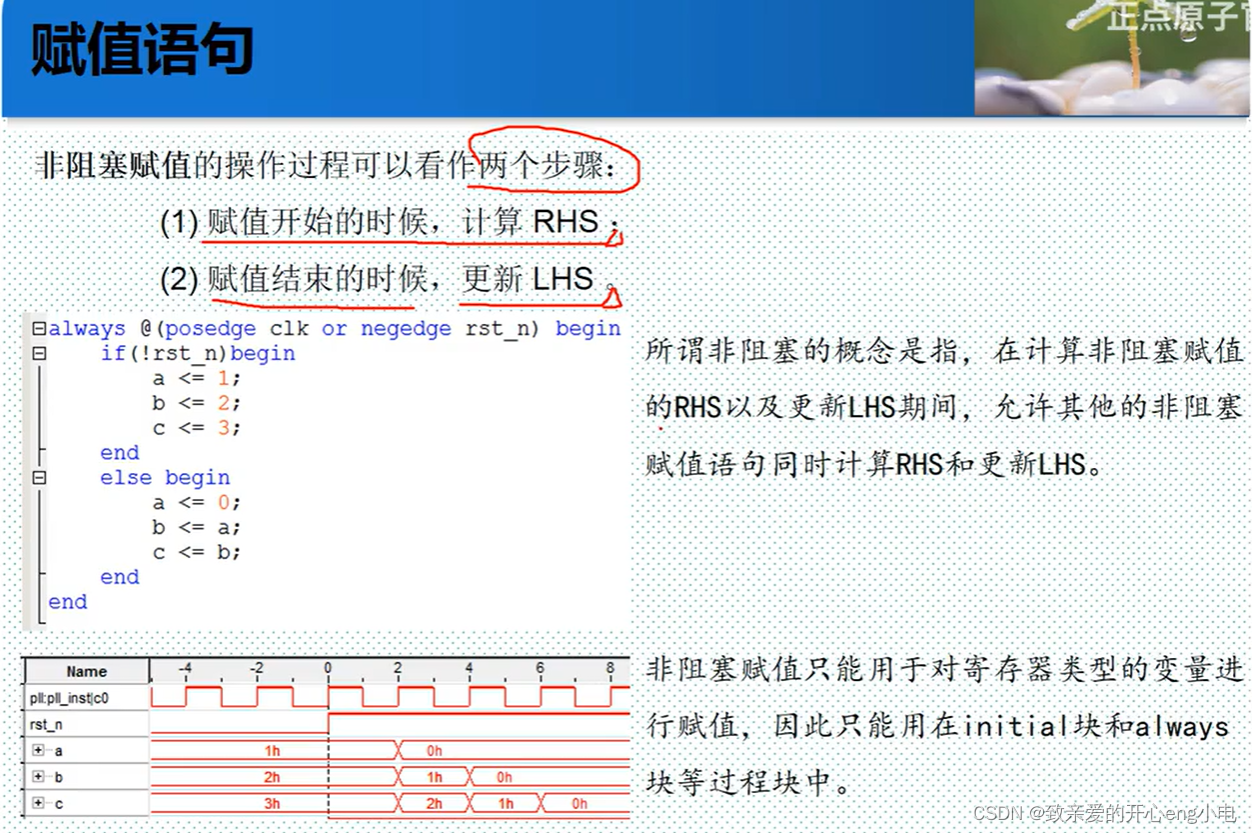

賦值語句:阻塞語句和非阻塞語句

條件語句

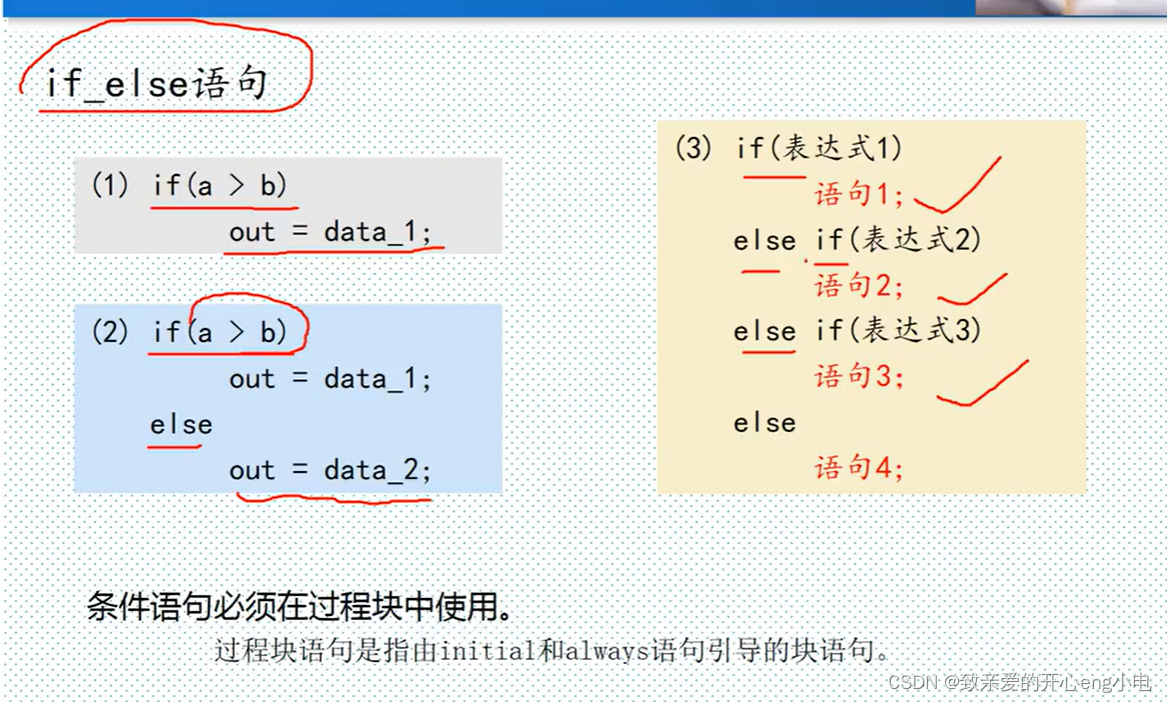

if else

case

‘bx:默認32位

狀態機

狀態機的概念

狀態機是Verilog中很常見的一種語法結構。

首先,我們在什么時候需要用狀態機捏?一個密碼鎖的example:

狀態機的模型

moore狀態機是mealy狀態機的一個特例

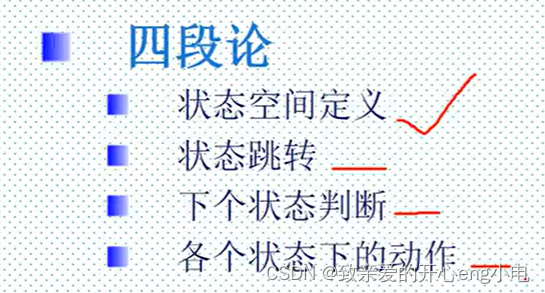

狀態機的設計

八股文。寫就有分。

example:推薦獨熱碼

latch:會導致電路毛刺很多

產生latch的原因:1case情況沒給完全2if沒有對應的else

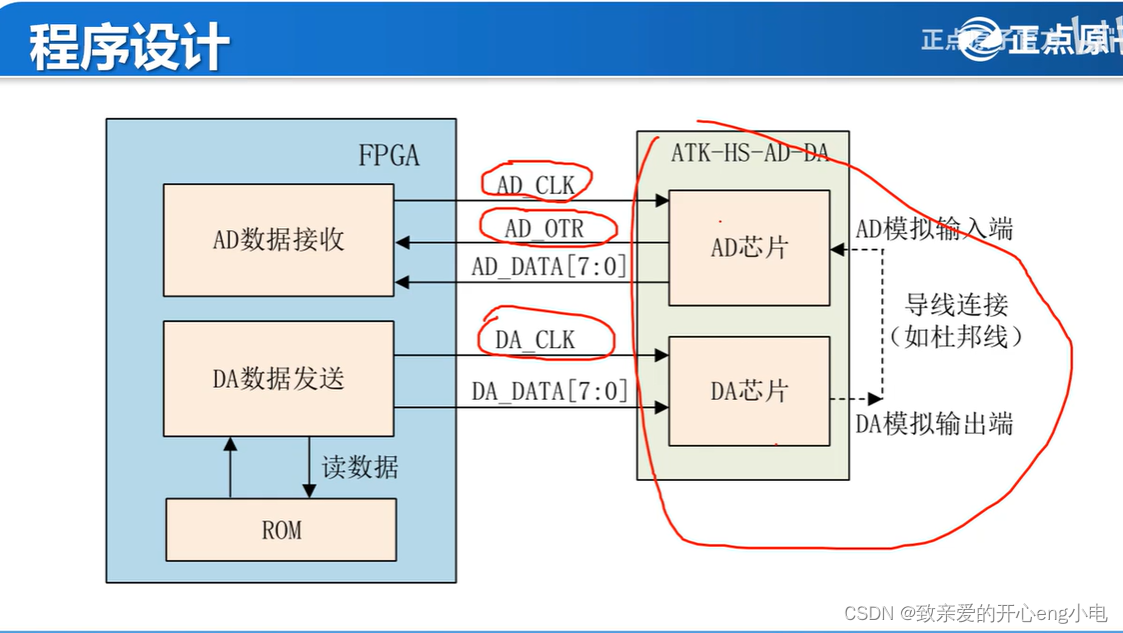

2ADDA

AD_OTR:指示位,模擬量超出量程了!

3串口通訊發送原理

后臺系統的員工管理業務開發)

@entry和@Component的生命周期)

)

值得一看)

:DISTINCT)

)

—— memmove()函數 (內含memmove的講解和模擬實現))