之前嘗試UART0(MIO50、51),串口調試助手收到發送的內容。

現在板子上EMIO端有多個串口,所以看看這個怎么弄。

串口是484的轉接板(接232的串口就會輸出亂碼)

https://blog.51cto.com/u_15262460/2882973

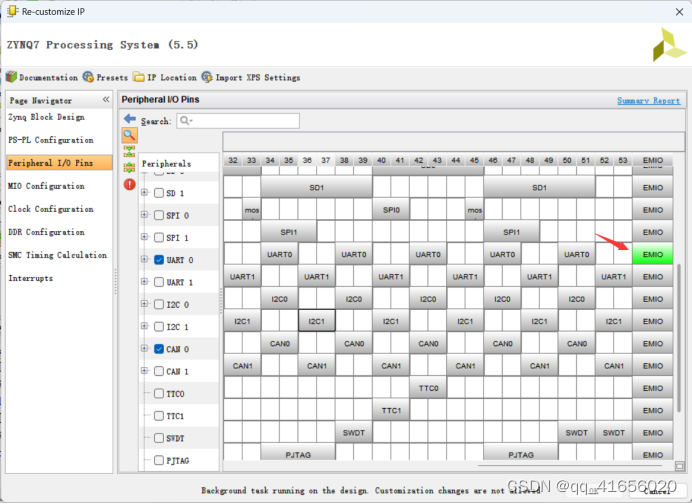

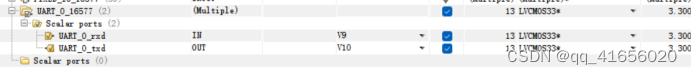

system IP配置UART0為EMIO,然后約束引腳

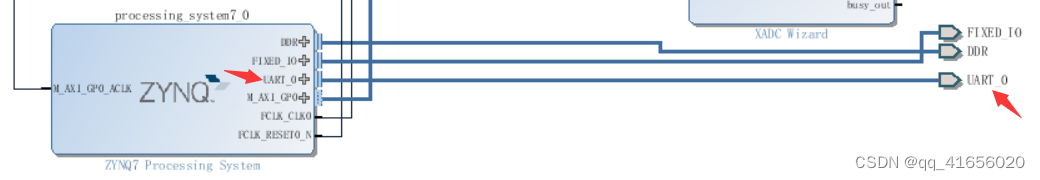

IP都是之前配置好了,現在重新配置,發現HDL Wrapper沒有UART管腳,發現是block這里需要Make External:

然后生成bit gen。

Launch SDK(記得include bitstream)

但是串口調試助手沒有收到任何打印信息。

UART 16550 IP核使用詳解_zynq uart16550-CSDN博客

AXI UART 16550 IP核簡介_axi16550-CSDN博客

ZYNQ axi uart16550 IP核擴展485接口使用-CSDN博客?

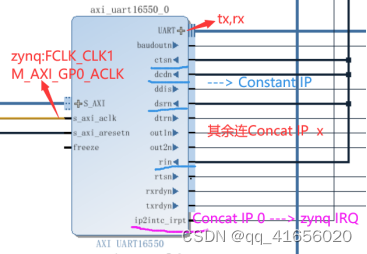

添加UART16550 IP核,配置AXI試試看。

ZYNQ UltraScale MPSOC,使用PL端AXI_UART16550IP核,且在PS端控制下實現RS485通信,接收不同幀長報文數據-----中斷方式_zynq rs485-CSDN博客

zynq IP:配置DDR,PL to PS IRQ,

AXI GPIO IP:1bit output(控制RS485的DE)

UART 16550 IP:RS485的數據接口

Run Automation自動連線

刪除AXI UART 16550 IP的UART引腳

展開UART 16550 的UART接口

添加constant IP:1bit,value = 1

連接UART 16550的ctsn、rin和constant IP;

再添加一個constant IP:1bit,value = 0

連接UART 16550的freeze,dcdn,dsrn與第二個constant IP;

將UART 16550 IP中的sin和sout引腳導出,修改引腳名字為RS485_RXD和RS485_TXD;

將AXI GPIO IP中引出的GPIO的引腳名字修改為RS485_DE。

添加concat IP,輸入連接UART 16550 IP的ip2intc_irpt,輸出dout連zynq IP的irq。

基于FPGA的UARTl6550的設計-AET-電子技術應用

引腳綁定為DE、Tx、Rx

但是看原理圖沒有DE腳。

所以修改了下走線:

Xilinx SDK程序Debug無法在main函數入口處停住解決_sdk 調試不進main-CSDN博客

程序跑飛了:看自己PS配置,bank1電源沒有設置為1.8V,DDR芯片型號設置錯誤

然后uart的tx、rx照著原理圖配置;RS484的A+和B-接反了。

波特率設置不一致:收到亂碼。修改后:成功!

)

)

系列-管理查詢調整)

)