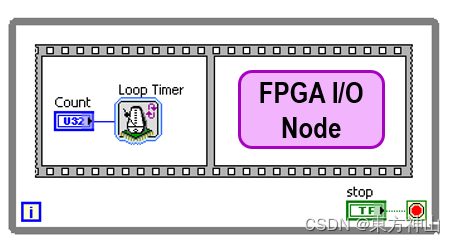

1.同步使用循環定時器VI計時循環速率的系列模塊

- 數字模塊

- SAR ADC 模塊

- 多路復用模塊

????????數字通道可以在一個時鐘周期內執行。模擬通道需要多個時鐘周期。

? ? ?????同步模擬模塊的每個通道有一個 ADC,采集的數據在通道之間沒有明顯的偏差。多路復用模塊使用多路復用器通過單個 ADC 路由多個通道,因此多路復用模塊中的所有通道之間存在通道間延遲或偏移。????????

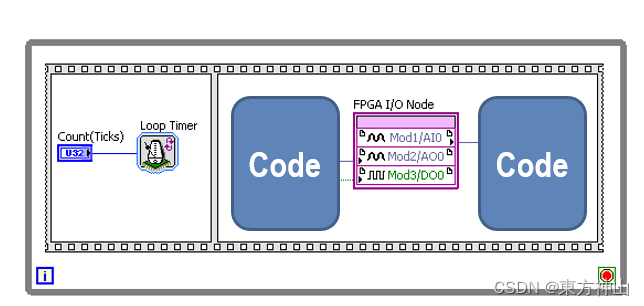

????????要同步不同通道和不同模塊,請將所有通道讀取或更新放在同一個 FPGA I/O 節點中,以最小的偏差混合模擬輸入、模擬輸出和數字 I/O 通道。?

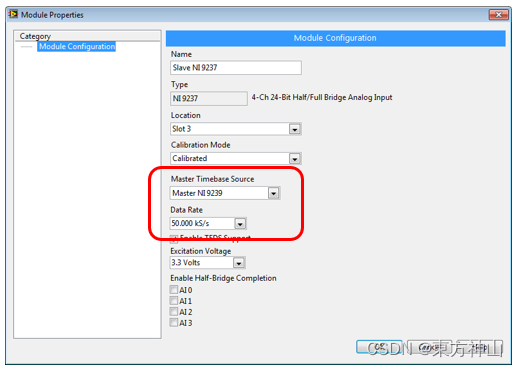

2.同步Delta-Sigma C 系列模塊

????????選擇其中一個模塊master,將時鐘導出到背板。其他模塊都設置從背板導入該時鐘。無論您選擇哪個模塊作為主模塊,都將覆蓋時基和可用采樣率。

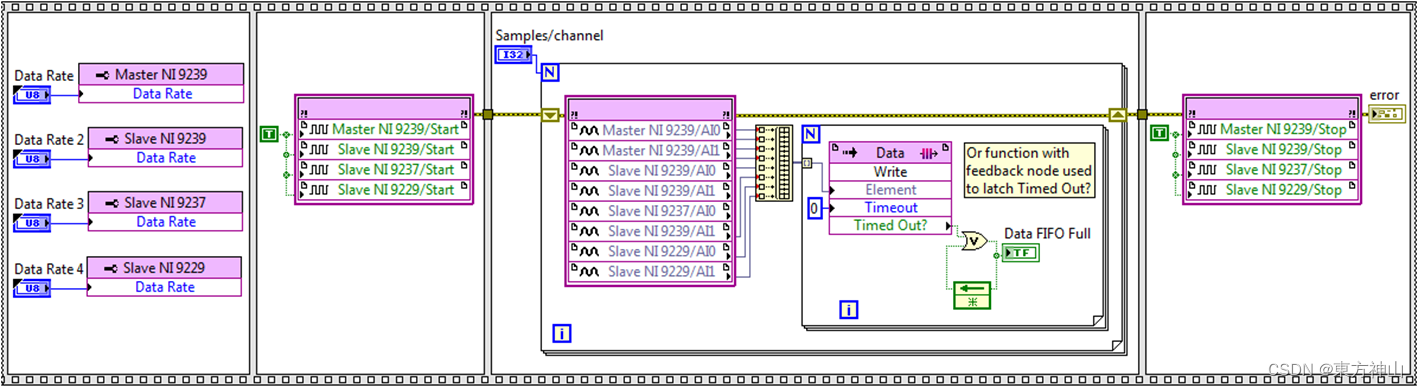

????????在框圖中,為每個io模塊創建一個Property Node,并使用“Data Rate”指定速率,請注意,即使I/O模塊共享相同的采樣率,您也必須為每個Property Node創建唯一的Data rate 右鍵單擊每個模塊的Property Node并選擇create?Constant)。這樣可以確保整數與特定I/O模塊的預期速率正確匹配。

????????為每個I/O模塊創建一個Start Trigger,并將它們放在同一個I/O節點中。這確保了正確路由了啟動觸發器。

? ? ? ?將來自所有同步模塊的所有通道讀取放到同一個I/O節點中。使用這個過程,您可以混合和匹配任何現有的同步delta-sigma模塊。

|

| 為主模塊和從模塊配置 FPGA I/O 屬性節點,并將控制連接到每個節點。 |

|

| 為要同步的模塊配置具有啟動通道的 FPGA I/O 節點,并將設置為 TRUE 的布爾常量連接到每個啟動通道。 |

|

| 使用要同步采樣的所有通道配置 FPGA I/O 節點。 |

|

| 為要同步的模塊配置具有停止通道的 FPGA I/O 節點,并將設置為 TRUE 的布爾常量連接到每個停止通道。 |

????????在LabVIEW FPGA中同步不同delta-sigma模塊的最佳方法是將每個模塊的I/O節點放在同一個While Loop中。如果將不同模塊的I/O節點放在并行While循環中,則必須解決額外的啟動延遲問題。您還需要考慮每個模塊的組延遲,因為模塊在同一循環中同時獲取數據。

? ? ? ? 群延遲是 Delta-Sigma 模數轉換器 (ADC) 固有的特性。所有使用 delta-sigma ADC 的 NI C 系列模塊在用戶手冊中都有群延遲規范。每個 ADC 的群延遲通常都不同,并且會根據采樣率而變化。補償群延遲中這些差異的方法是使用濾波器,該濾波器將信號延遲一小部分樣本。?

????????濾波器用于添加人工延遲,以便兩個模塊上的總延遲相等。例如,NI 9215 的群延遲為 0 個樣本,因為它使用 SAR ADC。另一方面,NI 9229 由于其 delta-sigma ADC 具有 40.0 個樣本的群延遲。群延遲中的樣本數量可以在?下面相關鏈接部分的規范文檔中的規范輸入延遲中查看。通過創建延遲長度為 40.0 個樣本的濾波器并將其應用于 NI 9215 數據,兩個模塊將具有相同的延遲并且數據將同步。

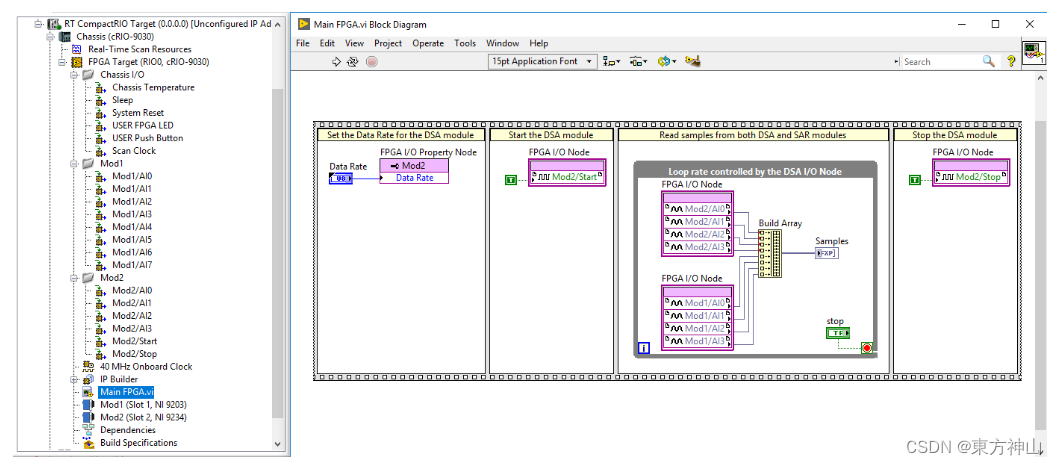

3.同步DSA與 SAR C系列模塊

????????使用 DSA 和 SAR 模塊的組合時,您可以使用數據速率屬性節點設計 delta-sigma 模塊計時的應用程序。通過這種方法,您可以添加按需 I/O 模塊,而無需使用 Loop Timer VI。此方法將所有模塊同步到 delta-sigma 模塊時鐘。

- 使用序列結構強制執行 DSA 模塊的數據速率配置、啟動和停止。

- 使用I/O屬性節點設置模塊的數據速率。

- 要更改屬性節點指向的項目:右鍵單擊屬性節點 > 選擇項目 > FPGA 目標 > Mod#,其中 # 是 Delta Sigma 模塊所在的插槽號。

- 您可以從項目資源管理器中拖放 FPGA I/O 節點。這些 I/O 節點可以擴展以容納多個輸入。使用同一 I/O 節點中的所有端子,以確保它們在 FPGA 中同時被讀取。

- 此方法將所有模塊同步到 delta-sigma 模塊時鐘。

- 需要考慮設備的 DSA 延遲。

- 要檢查C 系列模擬輸入模塊具有什么類型的 ADC,請查看設備的用戶手冊。

)

表的內連和外連)

:進程與進程間通信設計之趣味貓咪抓老鼠游戲)