今天天中午午休的時候,我剛要打開手機的準備刷抖音看無憂傳媒的學生們的“學習資料”的時候,看到CSDN -APP上有提醒,一看原來是一位道友發的一個問題:

本來小編最近由于剛剛從國外回來,手上的項目都已經結束了,這周開始學習仿真測試驗證呢,而且今天本來是準備開始寫上次遺漏的一個問題點:下圖紅色標記的地方。

這個文章是之前發布的關于POC電感的,感興趣或是忘記了的鐵子們可以點擊下面的鏈接去查閱之前的文章。

Marin說PCB之POC電路layout設計仿真案例---02

好了,既然氛圍都已經襯托到這了,那小編就開始了今天的POC電感案例仿真驗證了:

步驟:

一,在仿真軟件中導入我們單板的層疊信息:

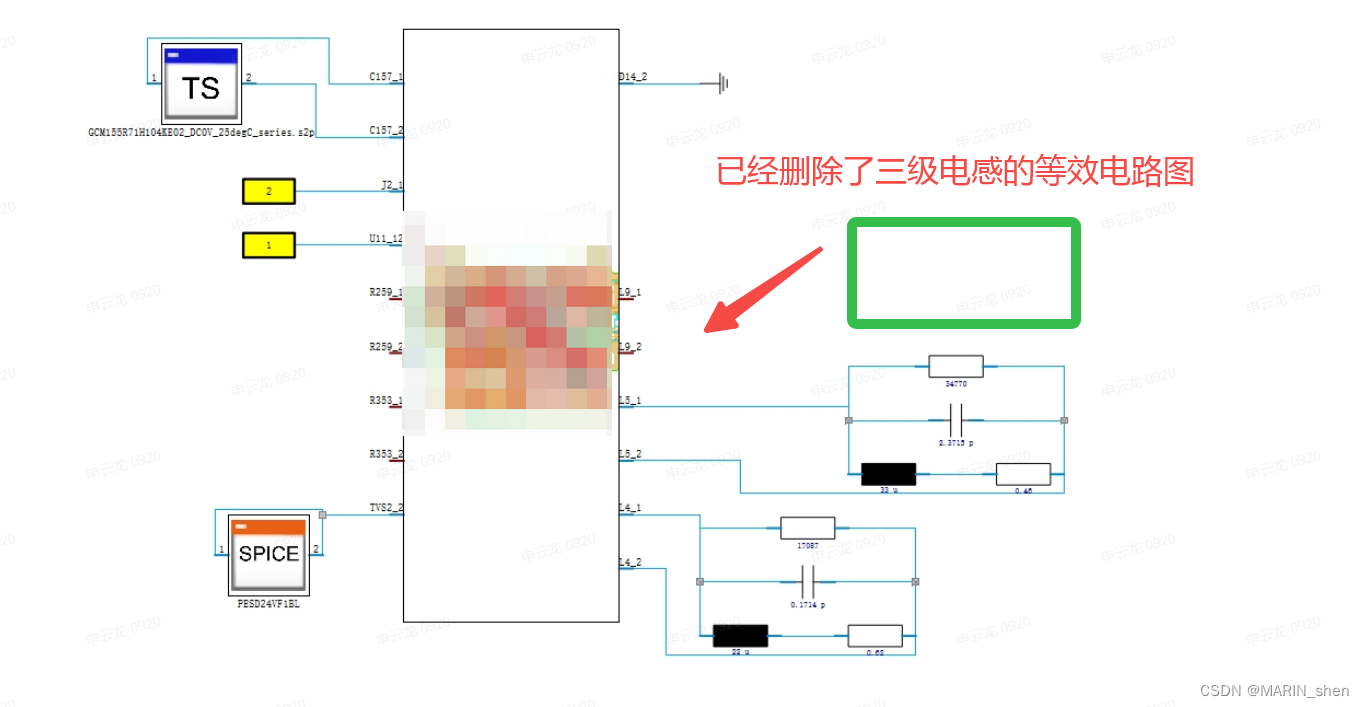

二,仿真原理的搭建,添加了電感的等效電路后的仿真電路圖如下圖,目前是已經把三級電感的等效電路圖刪除了,其設計中采用了GMSL 1 _3.125GBPS的速率配置。

三,IL的仿真結果如下圖所示:

四,RL的仿真結果如下圖所示:

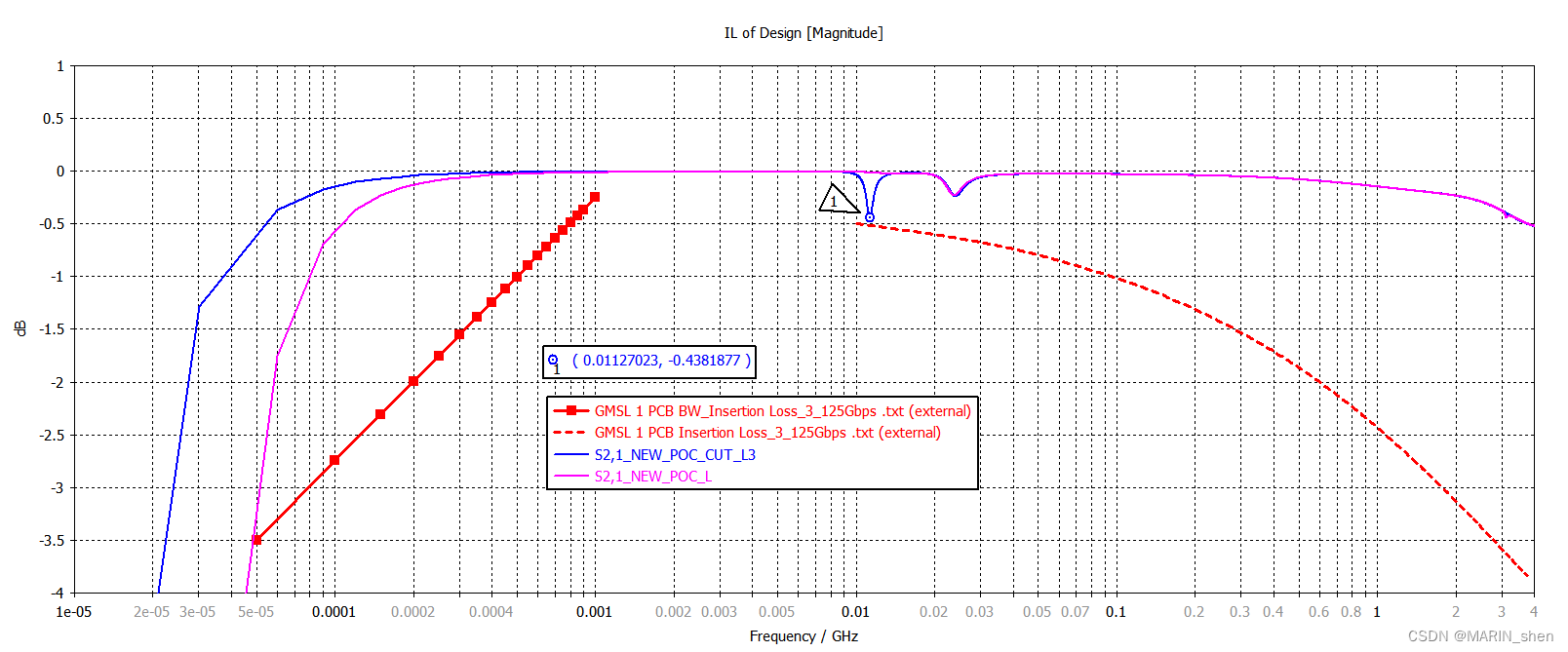

五,導入之前的完整的POC三級電感方案的IL的比對仿真結果如下圖所示:

六,導入之前的完整的POC三級電感方案的RL的比對仿真結果如下圖所示:

七,結論:從上面的兩幅仿真結果顯示POC三級電感的引入確實會改善其插損和回損的性能,在11.2MHz的時候串聯一個相同型號的三級電感會把這個掉坑給優化好,其主要原因是我們串聯一個型號相同電感相當于把其等效阻抗值抬升了。下面我們可以通過做一個仿真去驗證這個理論。

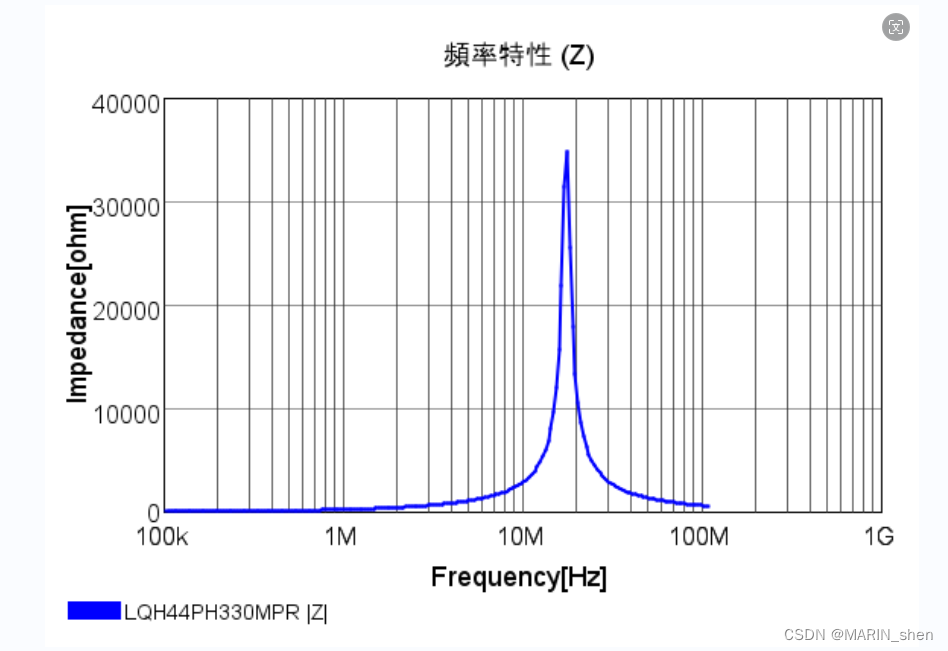

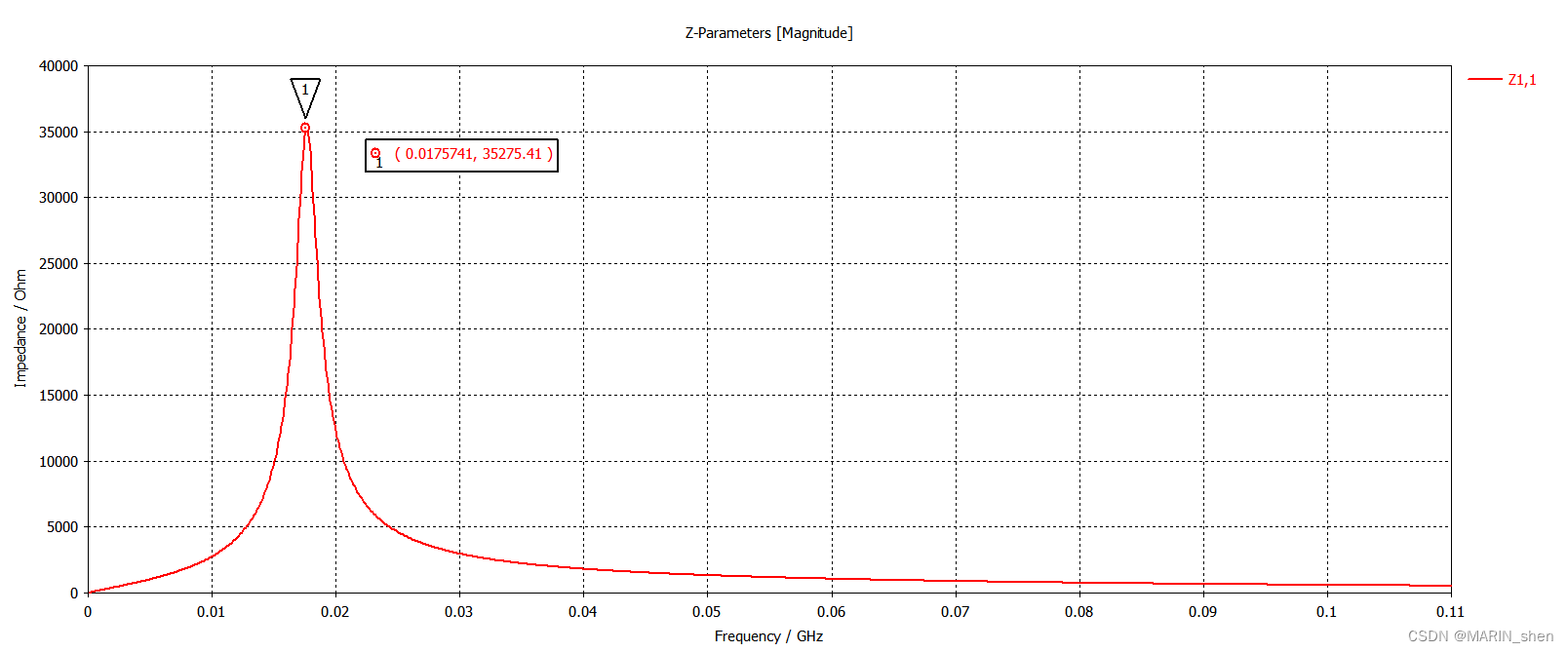

八,首先我們在官網上找到這顆電感的頻率特性阻抗曲線圖,然后我們在仿真軟件中導入其S參數去比對是否和官網上的頻率特性曲線一致,目前通過仿真比對來看整體是一致的。

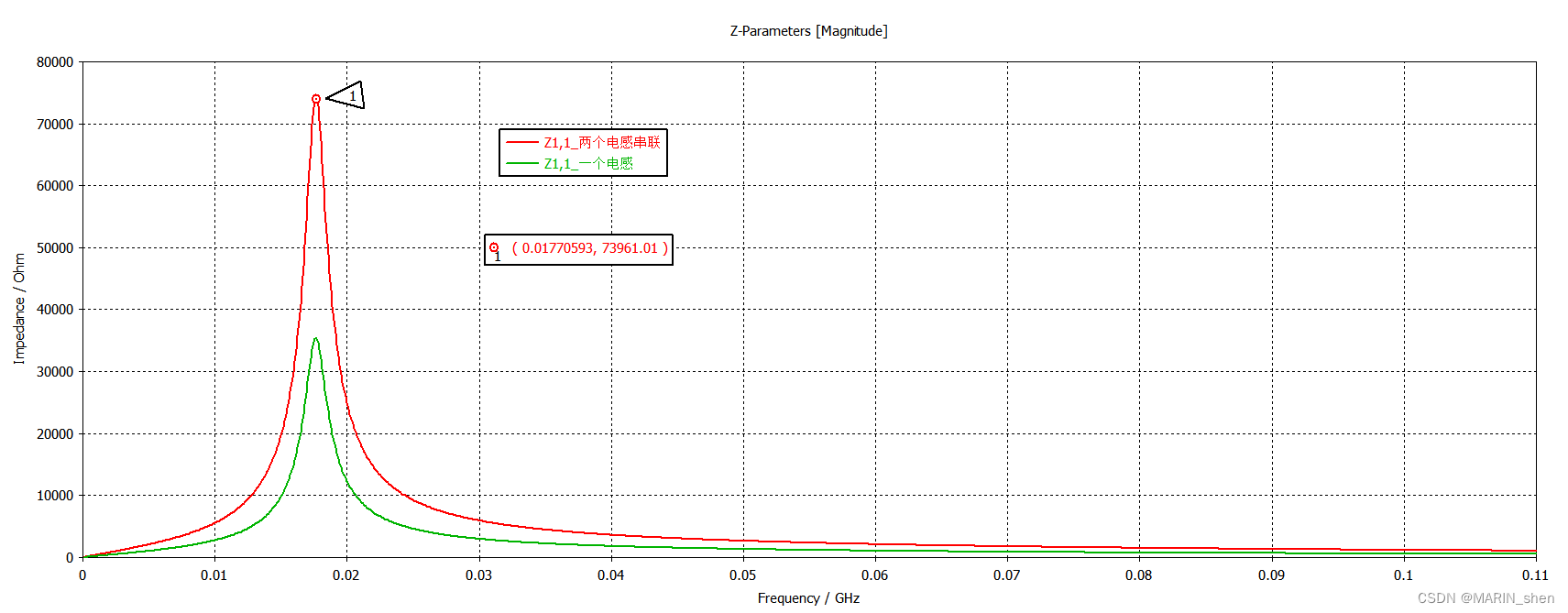

九,在仿真軟中把這兩個電感串聯起來去觀察其頻率特性阻抗曲線圖,如下圖所示:

十,在仿真軟中把這兩個電感并聯聯起來去觀察其頻率特性阻抗曲線圖,如下圖所示:

十一,結論:從上面的兩幅仿真結果顯示POC三級電感的引入確實會改善其插損和回損的性能的主要原因是:兩個型號相同的電感串聯后,其總的等效阻抗Z是變大了很多了,從之前的Z=35275歐姆變成了73961歐姆,這樣其總Q值變小了,POC電感的隔離度就變得很好了,最終體現在其插損和回損上就變小了。當然有人該說了你這個Q值是嘛意思啊?我聽不懂啊,這個Q值我之前 文章中也是有提到這的知識點的,既然有人提問了,我這就在多啰嗦一句吧:

電感的Q值:電感的Q值也叫作品質因數,其為無功功率除以有功功率。簡單理解的話,就是在一個信號周期內,無功功率為電感存儲的能量,有功功率為電感消耗的能量。

Q=無功功率/有功功率

電感一般使用頻率遠小于其自諧振頻率,因此寄生電容可以忽略,此時無功功率主要由電感產生,所以Q等于wL除以Rs

Q=無功功率/有功功率=JWL/Rs

這里有一點需要大家注意的是,這里的Rs并不是電感的直流導通電阻Rdc,它包含了電感的所有損耗,我們可以稱之為等效串聯總電阻。

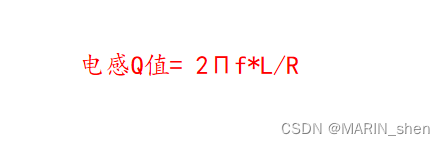

對電感來說,在某一頻率的交流電壓下工作時,所呈現的感抗與其等效損耗電阻之比。要計算線圈的Q值,請使用以下公式:

Q=2πFL/R

其中Q表示的是線圈的質量數值也就是我們常說的品質因子,F為頻率,R則表示的是高頻率的直接電阻的分量。

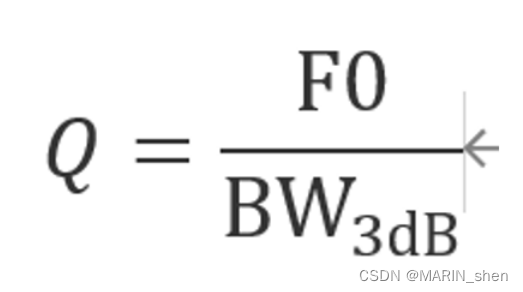

Q還有一個公式定義:

實線的曲線是高Q電感的曲線,虛線的是低Q的曲線;如之前有列過Q和Bw的公式,Q越大,Bw越窄,過了諧振點后的阻抗曲線下落明顯,是否就意味著電容分量越大;Q越小,Bw越寬;是否也就意味著過了諧振點后電容分量更小;這樣,降低Q值了,電路的反諧振的概率就低了。同樣的道理,幾個容值相差很多電容并聯,也會產生反諧振,也是在當中串(注,電容的情況時串阻尼電阻)來破壞其反諧振點(其實也是降低了電容的ESL分量).

總的來說就是我們POC電路中的電感的阻抗增加了,其Q值是降低了,其隔離度就越好了,插損及回損就變的越小,對應的其S參數的插損和回損的曲線就很平滑了,不會出現掉坑的情況了。至于電感的Q值和其阻抗的關系為啥是反比的,感興趣的鐵子們可以自己課下推算一下,我也給大家補充說明一下吧:

?首先我們電感實際生產出來并不是理想電感,線圈匝數之間也會存在寄生電電容,線圈也不是超導體,會存在 直流電阻,所以,電感等效模型如下圖。

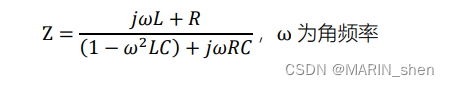

電感模型由電感和電阻串聯,然后和電容并聯構成,很容易列出去復阻抗表達式:

這個R和我們上面的Q=2πFL/R中的R都是電感線圈的直流電阻DCR,(Q值的公示中R我們可以近視看做是其電感的直流電阻DCR,其他的一些磁芯材料磁滯損耗和渦流損耗;趨膚效應造成的損耗這些我們先忽略不計),最終經過推到我們可以得出結論就是:電感的Q值和其阻抗的關系是成反比的。

好了,以上就是本期的所有內容了,我們下期文章不見不散。看完記得點贊加關注,謝謝。

)

logback配置詳解)