第 5 章IJTAG 網絡插入

IJTAG 網絡插入功能使您能夠連接現有的instrument,并插入 SIB、TDR 和 ScanMux 以創建您自己的 IJTAG 網絡。 IJTAG 網絡插入功能使您能夠將網絡連接到 TAP 控制器或設計中已有的 TAP 控制器。IJTAG 網絡插入的原理是使用 create_dft_specification 命令,非常簡單。工具讀取設計中instrument的 ICL 模型,并根據 ICL 模型的訪問需求插入 SIB 或 TDR。如果需要,您可以編輯或修改 IJTAG 網絡以滿足設計需求。 完成設計編輯后,您可以使用 extract_icl 命令生成 IJTAG 網絡的 ICL 描述。請注意,工具在 IJTAG 網絡插入后不會自動執行 ICL 提取,因為您可以在提取前進行額外的編輯。 Tessent IJTAG 可以生成并連接自己的 TAP,也可以連接到已有的 TAP 控制器。如果 IJTAG 網絡需要連接到已有的 TAP 控制器,則必須提供該 TAP 控制器的 ICL。

IJTAG 網絡插入流程

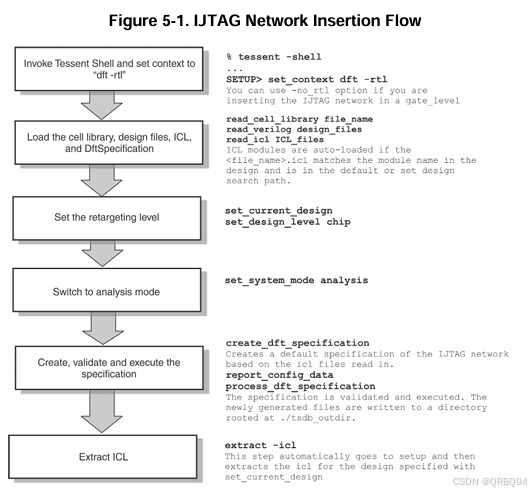

本節介紹了基本的 IJTAG 網絡插入流程,并列出了實現該流程的相應命令。 圖 5-1 展示了您使用 Tessent Shell 執行的基本 IJTAG 網絡插入流程的步驟。

如圖 5-1 所示,IJTAG 網絡插入流程相對簡單。由于您需要修改設計文件,因此必須將工具設置為 DFT 上下文,然后加載單元庫、設計文件以及所有使用的instrument的 ICL(這些可以自動為您加載)。第一個 create_dft_specification 命令指示工具創建 DftSpecification,第二個命令 process_dft_specification 在生成并修改設計文件之前運行一個驗證步驟。 當工具處理 DftSpecification 時,它會將文件寫入磁盤上的有組織的目錄結構中。這些文件包括以 ICL 和 Verilog 格式表示的所有插入的 IJTAG 網絡對象(SIB、TDR 和 ScanMux)以及所有修改后的設計文件。IJTAG 網絡是使用 create_dft_specification 命令自動生成的。然而,您始終可以使用編輯命令或通過使用 display_specification 的 GUI 來修改創建的 DftSpecification。如前所述,網絡的 ICL 描述不會自動生成,因為您可能需要進行進一步的設計編輯。然而,由于所有數據都存儲在內存中,您可以使用 extract_icl 命令執行后續的 IJTAG 網絡提取步驟。

IJTAG 網絡插入示例

以下是一個 IJTAG 網絡插入的示例。

set_context dft -no_rtl

## 讀取庫

read_cell_library ./library/adk_complete.tcelllib

read_cell_library ./library/memory.atpglib

## 讀取網表

read_verilog ./netlist/cpu_top_scan_tk.v

read_verilog ./generated/cpu_top_edt.v

read_verilog ./PLL/PLL.v -interface_only

## 在 set_current_design 之前讀取 ICL 和 PDL 文件

read_icl ./PLL/PLL.icl

dofile ./PLL/PLL.pdl

set_current_design cpu_top

## 在運行 set_system_mode analysis 之前設置設計級別

set_design_level chip

## 使用 set_attribute_value 指定 TAP 引腳

set_attribute_value tck_p -name function -value tck

set_attribute_value tdi_p -name function -value tdi

set_attribute_value tms_p -name function -value tms

set_attribute_value trst_p -name function -value trst

set_attribute_value tdo_p -name function -value tdo

set_system_mode analysis

report_icl_modules

## 自動從讀取 Verilog 的目錄中讀取任何 ICL

create_dft_specification

report_config_data

## 使用 display_specification 編輯或修改規范,或者使用編輯命令(如果需要)

## 如果需要的話。

process_dft_specification

extract_icl

exit

上述示例首先將context設置為 dft 并讀取庫。 下一步是讀取已經插入掃描和 EDT IP 的 Verilog 網表,其中 PLL 模塊已經存在。對于 PLL 模塊,已經單獨創建并驗證了 ICL 和 PDL。接下來讀取 PLL 的 PDL 和 ICL。使用 set_design_level 指定插入 IJTAG 網絡的級別。在此示例中,IJTAG 網絡插入在設計的頂層,因此在運行“set_system_mode analysis”之前指定了 TAP 引腳。 通過 create_dft_specification,PLL 和 EDT instrument的 ICL 自動配置為插入到 IJTAG 網絡中。可以使用 report_config_data 報告此網絡。如果需要 IJTAG 網絡連接,則使用 process_dft_specification,否則使用編輯命令或與 Configuration Data Visualizer 一起使用的 display_specification 來編輯。最后一步是 extract_icl,它為使用 set_current_design 設置的級別提供 ICL。

布局感知的 IJTAG 連接

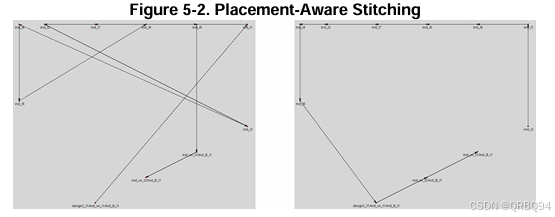

布局感知的 IJTAG 連接功能通過使用 DEF 文件中的坐標來創建節點之間的最短路徑,從而改善 IJTAG 掃描鏈中元素的排序。 如果沒有布局信息,工具會按字母順序將每個層次級別的簽核模塊和 IJTAG instrument連接到一個 IJTAG 鏈中。按字母順序連接可能導致布局和布線問題,但布局感知連接有助于緩解這一問題。 圖 5-2 比較了按字母順序連接(左側)和布局感知連接(右側)的 IJTAG 網絡布局示例。

布局感知連接使用 DEF 文件中的坐標生成一個 DftSpecification 包裝器,該包裝器對 IJTAG 元素進行排序以創建節點之間的最短路徑。加載 DEF 文件時,布局感知處理是自動進行的(不需要特殊的命令或開關)。DEF 文件應提供 IJTAG instrument掃描輸出引腳的布局信息。如果掃描輸出引腳的坐標缺失,布局感知連接將使用實例坐標。 連接從 IJTAG 掃描輸出端口(ijtag_so 或 tdo)開始。工具確定哪個元素的布局位置最近,并將其作為下一個節點,直到所有元素都連接到鏈中。如果掃描輸出端口的坐標缺失,連接將從坐標最接近(0,0)點的元素開始。 注意 您也可以通過在 Tessent Shell 中設置 “def_x_coordinate” 和 “def_y_coordinate” 屬性來提供節點坐標。

修改 IJTAG 網絡插入流程

在大多數使用場景中,您可以使用基本的 IJTAG 網絡插入流程。然而,如果需要,您可以對流程進行以下修改。

表 5-1. IJTAG 網絡插入流程的修改

要... | 描述 |

更改輸出目錄根目錄 | 默認情況下,process_dft_specification 命令將所有編輯后的設計文件和生成的 IJTAG 網絡對象文件寫入以 ./tsdb_outdir 為根目錄的有序目錄結構中。您可以使用 set_tsdb_output_directory 命令指示工具使用任何其他目錄根目錄;如果該目錄尚不存在,工具將創建它。 |

驗證寫入的 DftSpecification 是否正確 | 您有多種選項可以驗證寫入的 DftSpecification 是否正確。請參閱 process_dft_specification 命令的“-no_insertion”和“-validate_only”選項。 |

轉錄所有執行的設計編輯 | 高級命令 process_dft_specification 運行一系列 Tessent Shell 編輯命令,例如 create_connections 或 create_instance。通常,這些命令不會被轉錄,但在調試時可能很有用。process_dft_specification 命令為您提供 -transcript_insertion_commands 選項,該選項將 DftSpecification 執行期間執行的所有設計編輯步驟添加到轉錄中。 |

運行 DftSpecification | 您可以為當前設計加載多個 DftSpecification;它們根據用戶指定的標識符有所不同。有關更多信息,請參閱 DftSpecification 包裝器描述。通過 process_dft_specification 命令的 “id” 選項,可以輕松選擇其中一個或另一個 DftSpecification。 |

自動運行額外的設計編輯 | 在 DftSpecification 處理結束時,修改后的設計文件將寫入輸出目錄。如果您想進一步編輯設計,自動寫入設計文件是一個不必要的且可能耗時的步驟。process_dft_specification 命令提供了一種方法,告訴工具在寫入最終的修改后設計文件之前,先運行您的設計編輯命令。然后,該文件將包含插入的 IJTAG 網絡以及您指定的設計編輯。 |

寫入 process_dft_specification.post_insertion 過程 | 如果您正在編寫一個名為 process_dft_specification.post_insertion 的特定名稱的 Tcl 過程,并將其加載到內存中,您可以使用 dofile 命令并針對包含此過程的文件。或者,您也可以直接在主 dofile 中編寫 Tcl 過程。當 process_dft_specification 命令看到存在 Tcl 過程時,它將在 DftSpecification 指定的所有設計編輯成功完成后,但在運行 write_design 命令之前,自動調用 Tcl 過程。 |

- mtk_pd_adapter.c)

基本了解和工程配置)

LED 驅動芯片:特性與應用)

優化函數(付完整代碼))

算法詳解)

![[特殊字符] 認識用戶手冊用戶手冊(也稱用戶指南、產品手冊)是通過對產品功能的清](http://pic.xiahunao.cn/[特殊字符] 認識用戶手冊用戶手冊(也稱用戶指南、產品手冊)是通過對產品功能的清)