VCS仿真分為兩步式(編譯/compilation+仿真/simulation)和三步式(分析/analysis+細化/elaboration+simulation/仿真);

注2:analysis/分析是三步式flow中仿真design的第一步,在此階段將使用vhdlan或vlogan分析VHDL、Verilog、SystemVerilog和OpenVera文件。下面的部分包括幾個分析設計文件的示例命令行:

Analyzing your VHDL files:

vhdlan [vhdlan_options] file1.vhd file2.vhd

Analyzing your Verilog files:

vlogan [vlogan_options] file1.v file2.v

Analyzing your SystemVerilog files:

vlogan -sverilog [vlogan_options] file1.sv file2.sv file3.v

Analyzing your OpenVera files:

vlogan -ntb [vlogan_options] file1.vr file2.vr file3.v

Analyzing your SystemVerilog and OpenVera files:

vlogan -sverilog -ntb [vlogan_options] file1.sv file2.vr file3.v

注3:elaboration/細化是三步式flow中仿真design的第二步,在這個階段,使用分析過程中生成的中間文件,VCS構建實例層次結構并生成一個二進制可執行的simv,該二進制可執行文件之后用于仿真。可選擇優化模式或調試模式來細化design。

1.1.??編譯

1.1.1.?關于編譯

(1)?構建實例的層次結構,并且生成二進制可執行文件simv,該二進制可執行文件后續會用于仿真.

(2)?在編譯階段,可以選擇optimized mode或debug_mode進行design的編譯;

1.1.2.?編譯命令

(1)?vcs ?[compile_options] verilog_files

(2)?vcs?-sverilog?[compile_options] sverilog_files ?(using sv with vcs)

(3)?vcs -sverilog?-ntb_opts uvm-1.2?[compile_options] user_source_files_using_UVM ?????(using uvm-1.2 with vcs, -ntb_opts uvm-1.2會load UVM-1.2)

(4)?顯式指定UVM文件與參數: vcs -sverilog?+incdir+${UVM_HOME}/src ??${UVM_HOME}/src/uvm_pkg.sv ?${UVM_HOME}/src/dpi/uvm_dpi.cc ???-CFLAGS -DVCS?[compile_options]user_source_files_using_UVM

(5)?使用需要通過UVM register backdoor機制訪問HDL寄存器的test: vcs -sverilog?-debug_pp?-ntb_opts uvm [compile_options] user_source_files_using_UVM ?(-debug_pp可能會影響仿真性能,需要使用+vcs+learn+pli提高HDL訪問性能)

1.1.3.?常用的編譯option

注1:?-h or -help列出最常用的VCS編譯和運行時選項的描述;

注2:?-ID返回有用的信息,如VCS版本和構建日期,VCS編譯器版本,以及工作站名稱、平臺和主機ID;

(1)?-v filename:可以指定一個verilog庫文件,vcs會在該文件中查找module或UDP實例的定義;

(2)?-y directory:可以指定verilog庫文件路徑;

(3)?+incdir+directory+:指定路徑,vcs會在這些路徑下搜索`include語句中的文件;

(4)?+libext+extension+:指定vcs在指定路徑下搜索哪些擴展名的文件;

(5)?-full64:使能64-bit模式下的編譯與仿真;

(6)?-file filename:指定包含一系列文件與編譯時間選項的文件;

(7)?-gui:當在編譯時使用gui模式,仿真時會啟動DVE(Discovery Visualization Environment);

(8)?-R:在編譯完成后,立刻開始仿真;

(9)?-l filename:指定vcs記錄編譯信息的文件;如果同時使用-R option,vcs會將編譯信息和仿真信息均記錄到該文件內;

(10)?+define+macro=value+:其中=value參數是可選的,可以通過在verilog代碼中使用`ifdef來測試該define;

(11)?-debug, -debug_all, -debug_access(+<option>)

(12)?-o:可以指定編譯生成的二進制可執行文件的名字;

(13)?+mindelays:門級仿真時使用,表示器件延時使用sdf 文件中的最小值(sdf 文件中的時序(min:typ:max));

(14)?+maxdelays:門級仿真時使用,表示器件延時使用sdf 文件中的最大值(sdf 文件中的時序(min:typ:max));

(15)?–sverilog:支持systemverilog 語法(vcs 用,verid 用-sv);

(16)?+v2k:支持verilog 2001 特性;

(17)?-lca:Limited Customer Availability,支持動態數據類型associative Array,dynamic Array,smart Queue,string,

event,class;

(18)?–debug_all:支持所有debug 操作,DVE 選項,可以查看所有斷點(line,time,value,event etc) all 就是加權限。+w 是寫,+r 是讀,+f 是force, +l 是支持ucli 的單步調試, +n 是對網表操作。具體可以看手冊。+all 就是把所有的權限全開;

(19)?–debug_acess+all:在VCS 編譯的時候不用再加-p novas.tab pli.a 來定verdi 的路徑。

(20)?+ntb_random_seed=value:指定仿真隨機種子;

(21)?+ntb_random_seed_automatic:VCS 自動生成隨機種子;

(22)?-timescale=1ns/10ps:命令行定義仿真時間刻度,若rtl 中有timescale 的定義,則會覆蓋makefile 中的定義;

(23)?+neg_tchk:門級仿真時使用,表示當進行negative timing check時必須包含該option,否則vcs會把所有負值變為0,這會使得timing check很悲觀.

(24)+nospecify/+notimingcheck:門級仿真時使用,表示忽略path delay和specify延時;

(25)?-negdelay:門級仿真時使用,表示使能SDF文件中的所有的負值,但是要保證setup和hold(rec和rem)的和為正值,否則vcs會忽略負值同時給出warning.

1.2.??仿真?

1.2.1.?關于仿真

(1)?在編譯階段,vcs會生成二進制可執行文件.simv;可以使用simv進行仿真;

(2)?根據怎么編譯design,仿真可以有兩種模式: interactive模式(編譯采用debug模式,也稱為interactive模式)與batch模式;

(3)?Interactive mode:?在初始階段以交互模式(調試模式)編譯design。在這個階段,可以使用GUI或通過命令行調試design問題。通過GUI進行調試可以使用Verdi,通過命令行進行調試可以使用UCLI (Unified command line interface);

(4) batch mode:?當大多數design問題解決后,可以使用批處理模式(優化模式)編譯design。在這個階段,可以以最小的debug性能來換取更好的性能來運行回歸

1.2.2.?仿真命令

(1)?simv [run_options]

(2)?uvm仿真命令: simv?+UVM_TESTNAME=your_uvm_test??[sim_options]

1.2.3.?常用的仿真option

1.2.4.?interactive模式下仿真

(1)?必須使用DVE或者UCLI;

(2)?DVE的優點:

(2.1) DVE提供GUI接口,便于debug,使用時需要保證VCS與DVE版本相同;

(2.2)?DVE便于觀察波形,比較波形,觀察原理圖;

(2.3)?執行ucli/tcl命令;

(2.4)?設置斷點;

(3)?DVE工作在interactive模式下的仿真命令

(3.1)?simv -gui

(4)?DVE工作在post-processing模式下的仿真命令

(4.1)?dve -vpd [VPD/EVCD_filename]

(5)?UCLI簡介

(5.1)?ucli命令基于tcl;

(5.2)?通過使用ucli命令,可以控制仿真, dump VPD文件,保存或重現仿真狀態, force/release信號;

(5.3)?使用斷點;

(6)?啟動ucli

(6.1)?simv [simv_options] -ucli

1.2.5.?batch模式下仿真

1.3.??dump波形

1.3.1?使能波形dump

無論采用系統函數或ucli dump波形,都必須采用如下option中的一個進行波形dump的使能;

(1)?-debug_access

(2)?-fsdb

(3)?-P $VERDI_LIB/novas.tab $VERDI_LIB/pli.a

1.3.2?采用系統函數進行波形dump

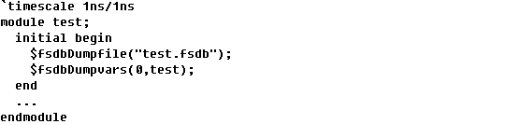

(1)?code內部調用系統函數,如下所示;

注1:dump波形時,避免在module內的兩個線程內都調用$fsdbDumpfile函數;因為第一次調用該函數時,會產生一個后綴為.fsdb的文件,當第二次調用該函數時,會報如下warning:"FSDB WARNING: The FSDB file already exists. Overwriting the FSDB file may crash the programs that are using this file.",這種情況下,只有第一次調用生效;

(2)?編譯命令如下所示;

![]()

![]()

(3)?仿真命令如下所示;

simv

1.3.3?采用ucli dump波形

![]()

)

:基于 Qt Widgets 搭建串口調試界面)

)