【開篇:設備——芯片工業的“劍與盾”】

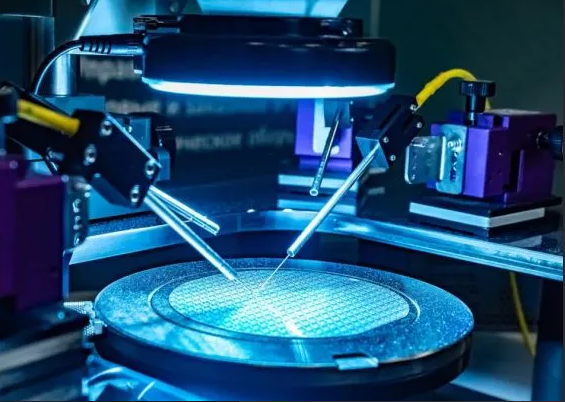

當ASML的EUV光刻機以每秒5萬次激光脈沖在硅片上雕刻出0.13nm精度的電路(相當于在月球表面精準定位一枚二維碼),當國產28nm光刻機在華虹產線實現“從0到1”的突破,這場精密制造的全球博弈早已超越技術競賽,成為國家科技實力的終極試煉場。據SEMI預測,2025年全球半導體設備市場規模將達1200億美元,其中光刻機、蝕刻機、薄膜沉積與檢測設備四巨頭壟斷超70%份額——每臺售價過億的設備背后,是材料科學、算法優化與光學工程的生死較量,更是全球產業鏈重構的縮影。

【系列導覽】

在《芯片生態鏈深度解析》系列中,首篇《基礎材料篇》揭開了硅片、光刻膠的“地基”密碼。本文將聚焦產業鏈中技術壁壘最高、資本密度最大的環節——基礎設備,從“卡脖子”最嚴重的光刻機,到國產化率不足5%的檢測設備,從蝕刻機的等離子體控制到薄膜沉積的原子級工藝,解析四大核心設備的技術攻堅與突圍路徑。

1光刻機:芯片制造的“皇冠”

1.1 作用

光刻機是芯片制造的核心設備,其作用類似于“納米級雕刻大師”,將電路圖案以極高的精度投射到硅片上。

-

精度要求:在7nm以下制程中,光刻機需刻畫比人類頭發絲小5000倍的線條(相當于在月球表面雕刻二維碼),誤差控制在原子級別。

-

工藝地位:芯片制造需經歷20-30次光刻步驟,耗時占整個生產流程的50%,成本占比達1/3,是半導體產業鏈的“卡脖子”環節。

1.2 核心技術

EUV光刻技術——“納米級手術刀”

-

原理:使用波長僅13.5nm的極紫外光(比頭發絲短5萬倍),通過60個高精度反射鏡組成的光學系統,將電路圖案縮小至8nm分辨率。

-

技術難度:EUV光會被所有材料吸收,需在真空環境中運行;反射鏡表面粗糙度需控制在0.12nm以內(相當于在北京到上海的地表起伏不超過5cm)。

-

標桿產品:ASML的TWINSCAN NXE:3600D機型,每小時可處理185片晶圓,單臺售價超1.2億美元(約9億元人民幣),是工業皇冠上的明珠。

雙工件臺系統——“分身術”提升效率

-

原理:通過兩個獨立控制的工件臺(一個曝光、一個測量),實現“曝光-測量”同步進行,將套刻精度提升至1.1nm(相當于在上海到北京的距離上誤差不超過1毫米)。

-

意義:大幅提升生產效率,避免傳統單工件臺“停頓-啟動”的時間損耗。

光源技術——“光刻機的心臟”

-

ASML的突破:EUV光源功率達500W(相當于將10萬瓦燈泡的能量壓縮到1平方厘米),可支持3nm以下制程。

-

國產差距:中國EUV光源功率仍停留在10W量級,差距約50倍,是國產化的最大瓶頸之一。

1.3 全球競爭格局

ASML的壟斷地位

-

市場占比:占據全球75%光刻機市場,EUV設備100%壟斷,2024年營收達235億美元。

-

技術壁壘:供應鏈整合德國蔡司(光學鏡片)、美國Cymer(光源)、日本東京電子(鍍膜)等全球頂級廠商,形成難以復制的生態閉環。

日本企業的“中低端突圍”

-

尼康、佳能:憑借i-line(365nm)、KrF(248nm)設備在成熟制程(如車載芯片)領域占據一席之地,但ArF(193nm)以上高端市場幾乎歸零。

-

優勢領域:在面板顯示、封裝光刻機等細分市場仍有競爭力。

中國的“破局之路”

-

28nm突破:上海微電子SSA600/20曝光機通過中芯國際驗證,實現國產替代。

-

EUV研發:中科院與上海微電子合作推進LPP(激光等離子體)光源技術,光源收集效率達15%(ASML方案為30%),預計2030年前后實現工程化。

-

政策支持:國家“十四五”規劃將EUV光刻列為重點攻關領域,大基金二期投入超200億元。

1.4 國產化挑戰

技術封鎖:瓦森納協定的陰影

-

限制條款:《瓦森納協定》禁止向中國出口14nm以下制程的光刻設備,EUV技術受嚴格管控。

-

影響:中芯國際7nm工藝曾因無法獲得EUV設備,被迫采用多重曝光(LELE+SAQP)替代方案,成本增加30%。

零部件依賴:全球供應鏈的“卡脖子”

-

光源:美國Cymer壟斷EUV光源,國產替代率不足5%。

-

物鏡:德國蔡司主導高端光學鏡片,表面粗糙度控制在0.12nm以內(相當于地球表面起伏不超過5米)。

-

工作臺:德國PI(普旭)壟斷超精密運動平臺,定位精度達0.5nm(相當于飛機飛行1000公里誤差不超過5cm)。

人才缺口:全球“搶人大戰”

-

頂級人才稀缺:全球頂尖光刻機工程師不足2000人,中國相關領域博士培養量僅為美國的1/5。

-

解決路徑:清華大學、中科院等機構設立“光刻專項”,聯合HW、中芯國際定向培養復合型人才(光學、材料、算法跨學科)。

1.5 未來展望

-

技術路線:

-

EUV國產化:2030年前后實現LPP光源工程化,突破500W功率瓶頸。

-

計算光刻:通過AI算法優化掩模設計,降低對物理設備的依賴(參考ASML的SMO技術)。

-

納米壓印:中科院探索NIL(納米壓印光刻)技術,成本僅為EUV的1/3,適用于存儲芯片領域。

-

-

產業協同:HW與上海微電子共建實驗室,推動光刻機與芯片工藝的適配。

2蝕刻機:芯片制造的“雕刻刀”

2蝕刻機:芯片制造的“雕刻刀”

2.1 作用

蝕刻機是芯片制造的核心工藝設備,其作用類似于“納米級雕刻大師”,通過等離子體或化學溶液,將光刻膠未覆蓋區域的材料精準去除,形成立體電路結構。

-

3D NAND挑戰:在170層以上的垂直雕刻中,需實現每層誤差不超過0.5nm,相當于“在頭發絲上建摩天大樓”。

-

工藝地位:芯片制造需經歷20-50次蝕刻步驟,耗時占整個生產流程的30%,成本占比達15%,是半導體產業鏈的“關鍵節點”。

2.2 核心技術

等離子體控制——“原子級手術刀”

-

原理:通過射頻電源激發氣體產生高能等離子體(溫度超1萬℃),利用離子轟擊和化學反應去除材料。

-

技術難度:需在亞微米尺度控制離子能量分布,避免過度損傷底層結構。應用材料的Centris Sym3系統可實現0.3nm級精度(相當于DNA雙螺旋結構的1/10寬度)。

-

國產突破:中微半導體的CCp介質蝕刻機在5nm節點實現99.99%的選擇比(僅去除目標材料,不損傷其他層),打破國際壟斷。

多腔體協同——“流水線式雕刻工坊”

-

原理:通過多個獨立反應腔(PM腔)并行作業,提升生產效率。Lam Research的Kiyo系列采用8個腔體同步作業,將晶圓處理速度提升3倍。

-

國產進展:中微刻蝕機實驗室精度達0.02nm(原子級),單臺設備可同時處理4片12英寸晶圓,良率超99.9%。

選擇性蝕刻——“精準識別材料的“偵探”

-

技術核心:通過調節蝕刻氣體或化學溶液配比,實現對特定材料的高效去除。例如,在5G射頻芯片中,需對氮化鎵(GaN)和二氧化硅(SiO?)進行差異化蝕刻。

-

應用場景:3D NAND堆疊層數突破500層后,需依賴選擇性蝕刻技術確保每層通孔對齊誤差<1nm。

2.3 全球競爭格局

美企主導:應用材料與泛林的雙寡頭格局

-

市場占比:應用材料(AMAT)、泛林半導體(Lam Research)占據全球47%蝕刻機市場,尤其在介質蝕刻、導體蝕刻領域形成技術壁壘。

-

技術優勢:應用材料的Centris平臺支持5nm以下制程,泛林的Kiyo系列在3D NAND領域市占率超60%。

中國突破:從“跟跑”到“并跑”

-

中微半導體:5nm蝕刻機進入臺積電供應鏈,CCp介質蝕刻機良率超99.9%,單臺售價約2000萬美元(僅為ASML光刻機的1/5)。

-

北方華創:硅通孔蝕刻機在長江存儲、合肥長鑫產線實現批量應用,市占率達12%。

-

政策支持:國家大基金二期向蝕刻機領域注資超30億元,重點支持12英寸設備研發。

日本力量:東京電子的“細分賽道”

-

技術優勢:在12英寸硅片刻蝕領域保持領先,設備兼容性強,可適配28nm-7nm全制程。

-

市場份額:受中美競爭影響,日本蝕刻機全球份額不足8%,但在車載芯片領域仍有競爭力。

2.4 國產化進展

技術突破:中微的“零的突破”

-

CCp介質蝕刻機:通過臺積電5nm認證,關鍵指標(選擇比、均勻性)達國際先進水平,單臺設備可替代3臺進口設備。

-

陶瓷部件國產化:中微自主研發的靜電吸盤、聚焦環等陶瓷部件,耐等離子體腐蝕性能提升50%,成本降低30%。

產能爬坡:長江存儲的“國產化試驗田”

-

采購數據:長江存儲二期產線采購的200臺蝕刻機中,國產設備占比從5%提升至18%,預計2025年達30%。

-

協同創新:中微與HW共建聯合實驗室,針對3nm GAA晶體管結構開發新型蝕刻工藝。

政策紅利:大基金與地方補貼雙輪驅動

-

大基金二期:注資30億元支持12英寸蝕刻機研發,重點突破原子層蝕刻(ALE)技術。

-

地方補貼:上海臨港、深圳光明科學城等地對蝕刻機企業給予15%-20%研發投入返還。

2.5 未來展望

-

技術路線:

-

原子層蝕刻(ALE):中微與中科院合作推進ALE技術,可在1nm以下節點實現單原子層去除。

-

混合蝕刻:結合干法(等離子體)與濕法(BOE蝕刻液)工藝,提升3D NAND深孔結構加工效率。

-

AI控制:應用材料已推出Enlight光學監測系統,通過實時反饋優化蝕刻參數,國產設備正加速跟進。

-

-

產業協同:HW與中微共建實驗室,推動蝕刻機與芯片工藝的適配。

3薄膜沉積設備:芯片制造的“涂裝師”

3.1 作用

薄膜沉積設備是芯片制造的核心工藝設備,其作用類似于“納米級貼膜師”,在硅片表面沉積金屬、絕緣體等薄膜材料,構建芯片的“骨架”與“血管”。

-

工藝需求:在3nm芯片中,需沉積超100層薄膜(較90nm制程翻倍),總厚度不足人類頭發直徑的1/10(約5μm),每層誤差需控制在0.1nm以內。

-

產業地位:薄膜沉積設備占晶圓制造設備成本的22%,2023年全球市場規模達211億美元,預計2025年將突破300億美元。

-

技術演進:從2D NAND到3D NAND(層數超170層),薄膜沉積需求激增;FinFET晶體管結構的復雜化進一步推動設備需求增長。

3.2 核心技術

原子層沉積(ALD)——“原子級畫師”

-

原理:通過脈沖式通入氣相前驅體,在基底表面發生飽和化學反應,逐層沉積單原子層薄膜。每層厚度約0.1nm(10次鍍膜≈1nm)。

-

技術難度:需實現表面飽和反應控制、高均勻性(深寬比>100:1的結構仍能均勻覆蓋)、低污染(雜質含量<1ppm)。

-

標桿產品:ASM International的Navigator ALD設備,單層沉積精度達0.1nm,應用于3D NAND字線、鎢插塞等關鍵工藝,良率超99.9%。

-

國產進展:微導納米開發的PEALD設備在5nm邏輯芯片實現氧化鋁(Al?O?)沉積,均勻性誤差<0.5%。

化學氣相沉積(CVD)——“高溫熔爐”

-

原理:通過高溫(800-1200℃)使氣態前驅體在硅片表面發生化學反應,生成固態薄膜(如二氧化硅、氮化硅)。

-

細分領域:

-

PECVD(等離子體增強CVD):在300-400℃低溫下成膜,占全球CVD市場30%(2023年約63億美元),應用如STI淺槽隔離、金屬層間介質。

-

HDPCVD(高密度等離子體CVD):通過磁場約束等離子體,實現高深寬比(>8:1)結構填充,泛林半導體的Centura平臺市占率超40%。

-

-

標桿產品:應用材料的Producer PECVD系統支持12英寸晶圓沉積,產能達200片/小時,介質膜致密度達2.2g/cm3。

-

國產突破:拓荊科技的PECVD 2800設備通過中芯國際28nm驗證,氧化硅(SiO?)沉積速率較進口設備提升15%。

物理氣相沉積(PVD)——“原子級濺射槍”

-

原理:利用高能離子轟擊金屬靶材,濺射出原子并沉積在硅片表面,形成金屬導電層(如銅、鈷)。

-

技術難點:需平衡薄膜附著力(>50MPa)、均勻性(誤差<2%)、高深寬比結構填充能力。

-

細分領域:

-

濺射PVD:占PVD市場70%,愛發科(Ulvac)的Magnetron濺射設備在銅互聯領域市占率超70%。

-

ECD(電化學沉積):用于銅大馬士革工藝,應用材料的Electra系統實現3nm節點銅填充,電阻率<1.8μΩ·cm。

-

-

國產進展:北方華創的Hermes PVD設備在長江存儲3D NAND產線實現鈷硬掩膜沉積,市占率突破5%。

3.3 全球競爭格局

歐美日壟斷:應用材料、ASM、愛發科的“鐵三角”

-

市場集中度:CR3(應用材料、ASM、東京電子)市占率達72%。應用材料以43%份額居首,ASM在ALD領域占46%。

-

技術壁壘:應用材料壟斷PECVD高端市場(80%以上邏輯芯片產線),ASM的SACVD(選擇性CVD)設備在蘋果A系列芯片封裝中市占率100%。

中國追趕:拓荊、北方華創的“雙雄戰略”

-

拓荊科技:CVD設備龍頭,2023年營收28億元,PECVD 2800進入中芯國際28nm產線,氧化硅沉積均勻性達±1.5%。

-

北方華創:PVD設備領跑者,Hermes PVD在長江存儲3D NAND產線替代東京電子設備,單臺售價約800萬美元。

-

政策支持:國家大基金二期向拓荊科技注資12億元,重點支持ALD設備研發。

日韓力量:東京電子、SEMES的“細分賽道”

-

東京電子:在LPCVD(低壓CVD)領域市占率36%,設備兼容28nm-7nm全制程,但受中美競爭影響,全球份額不足11%。

-

韓國SEMES:專注半導體顯示設備,CVD設備在OLED面板領域市占率超60%。

3.4 國產化挑戰

技術封鎖:瓦森納協定的陰影

-

限制條款:禁止向中國出口14nm以下制程的ALD、PECVD設備,拓荊科技14nm設備曾因無法獲取美國射頻電源被迫延期交付。

-

應對策略:中科院聯合拓荊開發國產射頻電源,功率穩定性達±0.1%

3.4 未來展望

-

需求驅動:5G、AI、存儲芯片堆疊層數提升(3D NAND超170層),薄膜沉積工序翻倍。

-

產業協同:設備廠商與晶圓廠(如中芯國際、長江存儲)深度綁定,加速工藝適配。

-

智能化升級:AI優化沉積參數,良率提升至99.9%以上。

4檢測設備:芯片制造的“質檢員”

4.1 作用

檢測設備是芯片制造過程中控制良率的關鍵環節,通過光學、電子束等技術實現納米級缺陷識別。在先進制程(如3nm及以下)中,設備需滿足:

-

超高速掃描:單臺設備每秒完成超10萬次掃描(如KLA-Tencor的Hercules檢測系統)。

-

超高精度:缺陷識別能力達亞納米級(0.5-1nm),確保晶圓良率穩定在99.99%以上。

-

全流程覆蓋:涵蓋薄膜厚度、關鍵尺寸(CD)、表面缺陷等200余項參數檢測。

4.2 核心技術

-

電子束檢測:KLA-Tencor的eDR7380系統分辨率達0.8nm,可檢測出單個原子級別的缺陷。

-

光學檢測:Onto Innovation的UVision系統通過深紫外光實現3D形貌重建,檢測速度達8000片/小時。

-

AI質檢:中科飛測將深度學習應用于缺陷分類,誤報率從5%降至0.5%。

4.3 全球競爭格局

-

美國主導:KLA-Tencor占據全球54%檢測設備市場,在電子束、光學檢測領域形成雙壟斷。

-

中國突破:上海精測半導體前道檢測設備進入華虹宏力12英寸產線,中科飛測AI質檢系統商業化落地。

-

日本力量:日立高新在CD-SEM領域保持技術優勢,但市場份額不足10%。

4.4 國產化挑戰

-

核心部件依賴:電子束檢測的高亮度燈絲(依賴FEI)、光學系統的超低畸變鏡頭(蔡司壟斷)仍需進口。

-

工藝適配性:GAA晶體管三維結構檢測需突破多角度照明、偏振光分析等關鍵技術。

4.5 未來方向

-

混合檢測技術:結合電子束與光學檢測優勢(如KLA的Surfscan+eScan系統),兼顧速度與精度。

-

智能化升級:AI預測性維護(如應用材料的Enlight AI系統)降低設備停機時間,國產廠商正開發類似技術。

-

綠色制造:低能耗電子束源、無汞紫外光源等環保工藝將成為行業標準。

【未來展望:設備突圍的“三大戰役”】

-

EUV光刻機攻堅:

-

中科院聯合企業啟動“EUV光源攻關計劃”,目標2030年實現500W功率突破。

-

納米壓印技術(NIL)成本僅為EUV的1/3,或成存儲芯片領域替代方案。

-

-

產業鏈協同創新:

-

中芯國際聯合北方華創、中微半導體成立“先進制程設備聯盟”,加速設備與工藝適配。

-

HW與拓荊科技合作開發ALD+CVD混合沉積工藝,目標3nm GAA晶體管。

-

-

智能化與綠色制造:

-

AI優化沉積參數(如應用材料Enlight系統),良率提升至99.9%以上。

-

低能耗電子束源、無汞紫外光源成為環保標準。

-

結語:設備革命即未來

從EUV光刻機的13.5nm光源到蝕刻機的等離子體控制,從ALD原子層沉積到AI驅動的缺陷檢測,芯片設備正以超越摩爾定律的速度進化。當ASML的EUV設備需40艘集裝箱運輸,而國產28nm光刻機實現“從0到1”的突破時,我們愈發確信:芯片戰爭的本質是設備戰爭。這場戰爭不僅關乎光刻機的精度、檢測設備的智能,更是一場材料科學、精密制造與算法生態的全面較量。設備革命的終點,將是人類制造能力的邊界——而中國,正在這條邊界上刻下自己的坐標。

系列預告:芯片設計篇——從EDA到架構的“智慧博弈”

下期《芯片生態鏈深度解析(三):芯片設計篇》

我們將聚焦芯片產業的“大腦”——設計環節,揭秘:

-

EDA軟件:如何通過算法優化決定芯片性能的90%?國產工具(如華大九天)能否突破Synopsys壟斷?

-

RISC-V架構:開源生態如何挑戰ARM的移動市場霸權?阿里平頭哥倚天710、HW鯤鵬的“去ARM化”路徑分析。

-

架構創新:存算一體、光子計算等顛覆性設計如何重塑AI芯片格局?寒武紀、壁仞科技的突圍案例。

![[ linux-系統 ] 命令行參數 | 環境變量](http://pic.xiahunao.cn/[ linux-系統 ] 命令行參數 | 環境變量)

凱撒密碼——附py代碼)

詳解,附代碼。)

)

)

)