DDR4控制器一般采用自帶的MIG控制器,用戶控制主要是基于MIG IP核進行設計

實際工程項目中可能只掛載了一組DDR,但是用戶數據可能有很多種,用戶通過給每種數據劃分特定地址進行存儲,如何實現靈活管理成為設計的關鍵

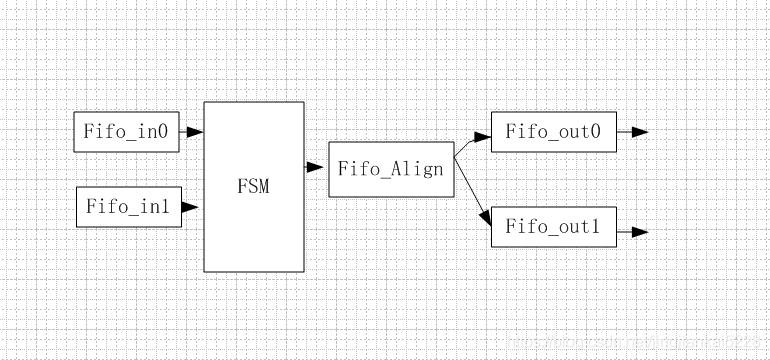

為了方便后端數據分流,可以通過緩存FIFO進行數據分流處理,示意圖如下圖所示,從FIFO_in0進入的數據最終輸出到FIFO_out0通道,這樣前端數據可以同時到達,只要數據的總帶寬不大于DDR4的理論帶寬,就不會發生數據丟失,從宏觀上看,DDR4是可以完成讀寫同時的,只要用戶數據不夠突發長度,即可發起DDR4的讀操作

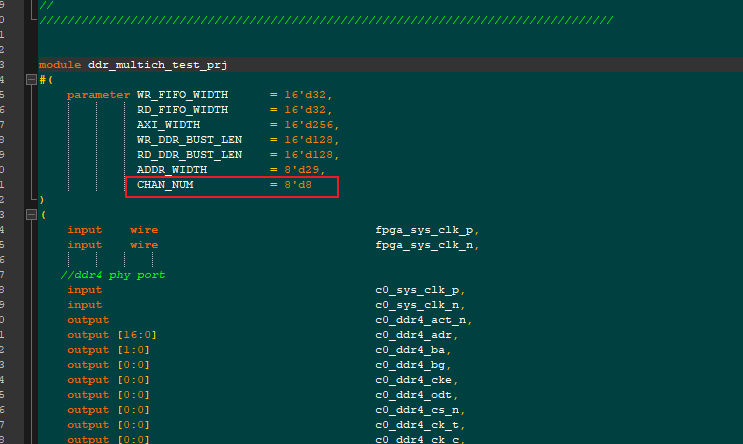

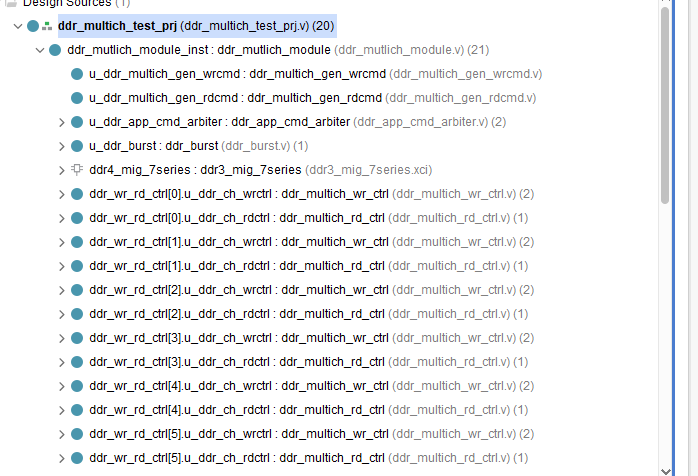

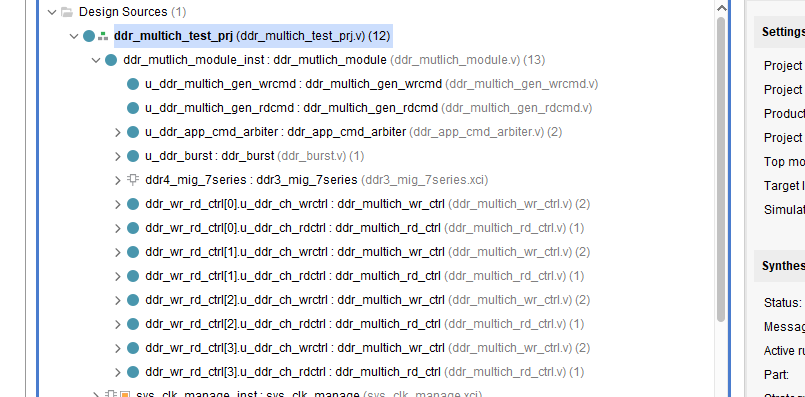

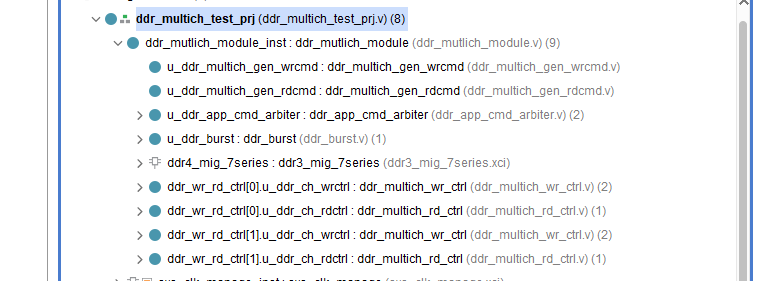

程序設計過程中,為了隨意裁剪通道數,盡量采用generate例化方式

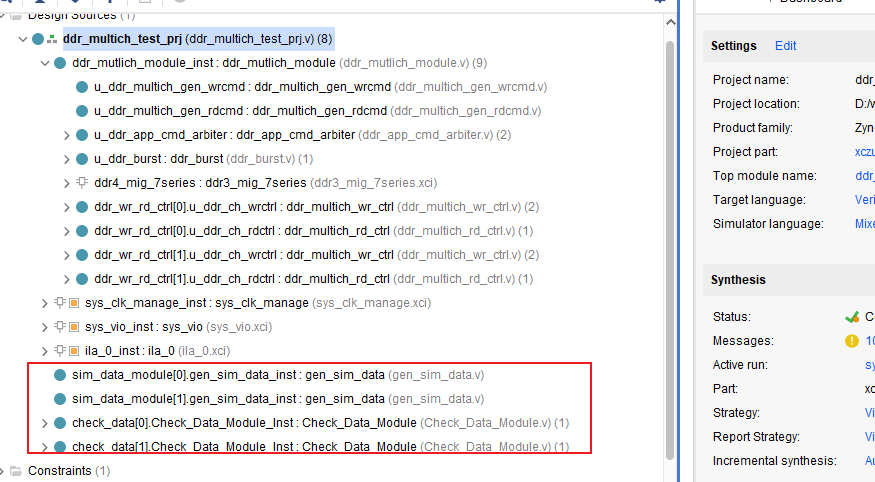

通過parameter決定實際使用的通道數

上圖為8通道例化

4通道例化

上圖為2通道例化模式

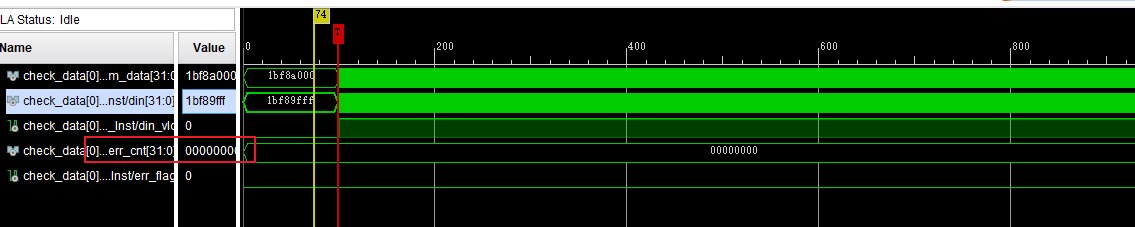

測試過程通過產生一個遞增數,然后輸出添加對應的校驗模塊

實際測試

通過統計錯誤數據個數,監測內部數據有無讀寫錯誤

測試下來DDR4的讀寫同時效率基本可以保證在75%左右

)

:測試gstreamer/v4l2+sdl2/v4l2+QtOpengl打攝像頭延遲和內存)

)

![LeetCode[102]二叉樹的層序遍歷](http://pic.xiahunao.cn/LeetCode[102]二叉樹的層序遍歷)