1Clock時鐘電路

時鐘電路就是類似像時鐘一樣準確運動的震蕩電路,任何工作都是依照時間順序,那么產生這個時間的電路就是時鐘電路,時鐘電路一般是由晶體振蕩器、晶振、控制芯片以及匹配電容組成

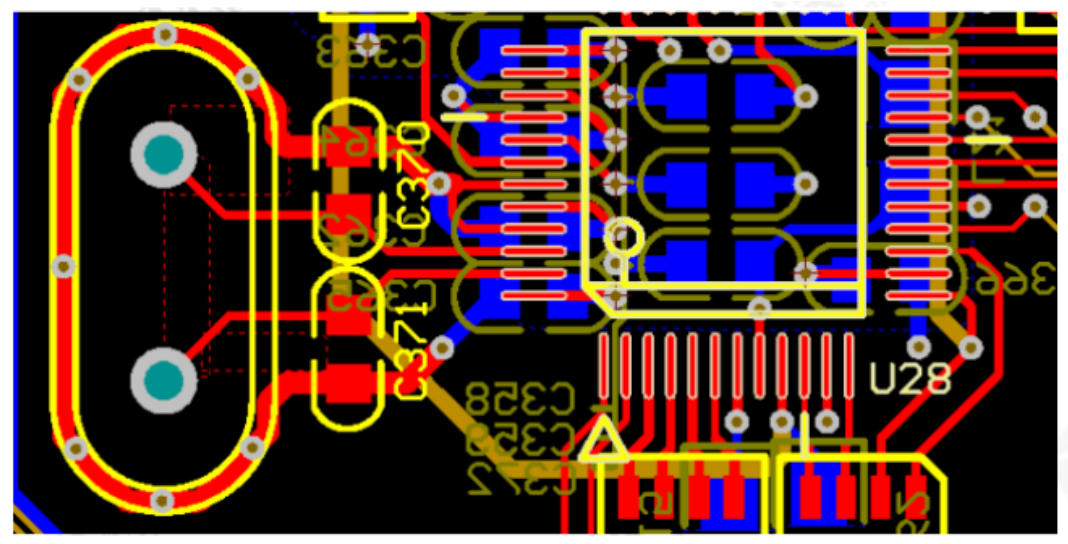

2.時鐘電路布局

- 晶體電路布局需要優先考慮,布局整體緊湊,布局時應與芯片在同一層并盡量靠近放置,以避免打過孔,晶體走線盡可能的短,遠離干擾源,盡量遠離板邊緣;

- 如果出現晶體電路在布局過程中與芯片放置在不同層的情況,應盡可能的讓靠近芯片,讓走線變短,并需要將晶體走線全程進行包地處理,以避免被干擾;

- 晶體以及時鐘信號走線需要全程包地處理,包地線每隔200-300mil至少添加一個GND過孔,并且必須保證鄰層的地參考面完整。

- 晶體的當前層可圍繞其進行GND走線形成地環,在地環放置GND過孔,連接到相鄰的GND平面層,用以隔離噪聲。

- 時鐘走線Xin與Xout以及晶體下方投影區域禁止任何走線,避免噪聲耦合進入時鐘電路;

- 晶體下面相鄰層必須保證完整的參考平面,避免出現跨分割現象,有助于隔離噪聲,保持晶體輸出。

- 晶振電路一般采用π型濾波形式,放置在晶振的前面。

3.時鐘電路布線要求

走線采取類差分走線;

晶體走線需加粗處理:8-12mil,晶振按照普通單端阻抗線走線即可;

對信號采取包地處理,每隔50mil放置一個屏蔽地過孔。

晶體晶振本體下方所有層原則上不準許走線,特別是關鍵信號線。(晶體晶振為干擾源)。

不準許出現stub線頭,防止天線效應,出現額外的干擾。

:從理論到實踐)

)

)

)

![[計算機網絡]數據鏈路層](http://pic.xiahunao.cn/[計算機網絡]數據鏈路層)