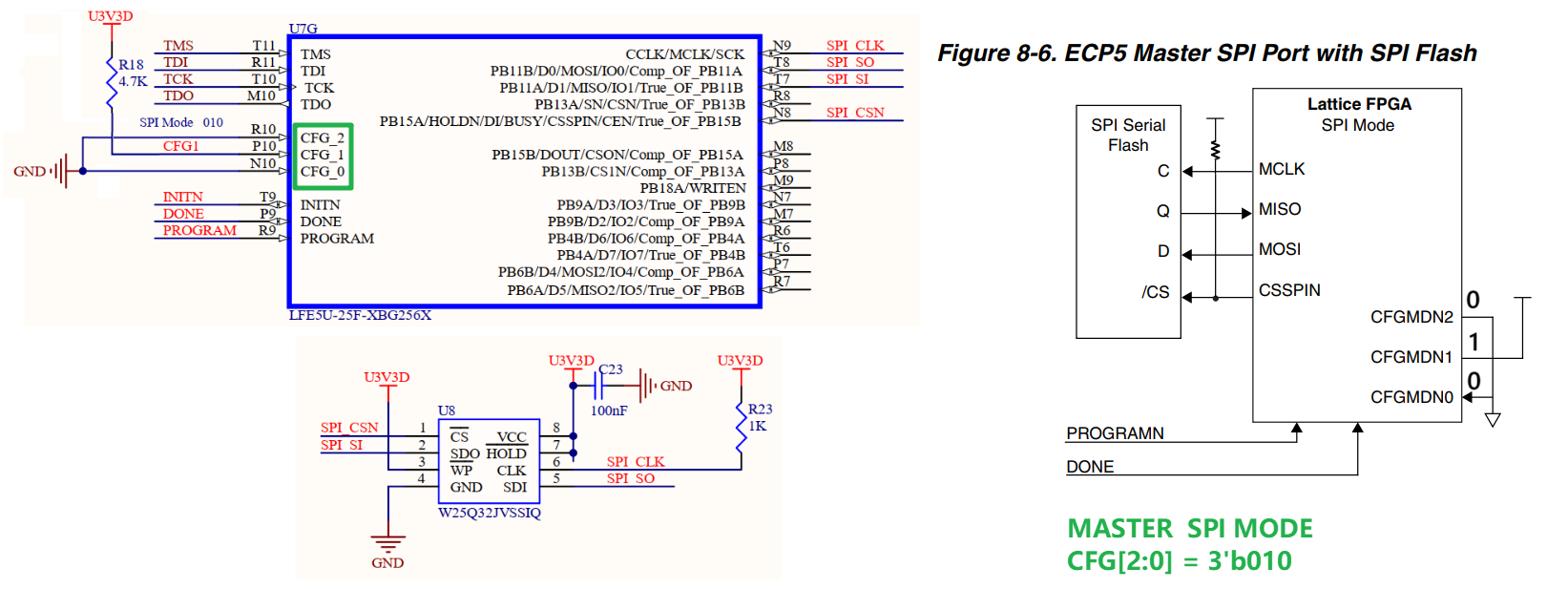

1.什么是FPGA的專用SPI接口?

此處的SPI FLASH接口即為FPGA的專用SPI接口,上電時,FPGA從該FLASH讀出程序并運行。

2.訪問SPI?PROM需要注意哪些地方?

1)處于MASTER?SPI MODE

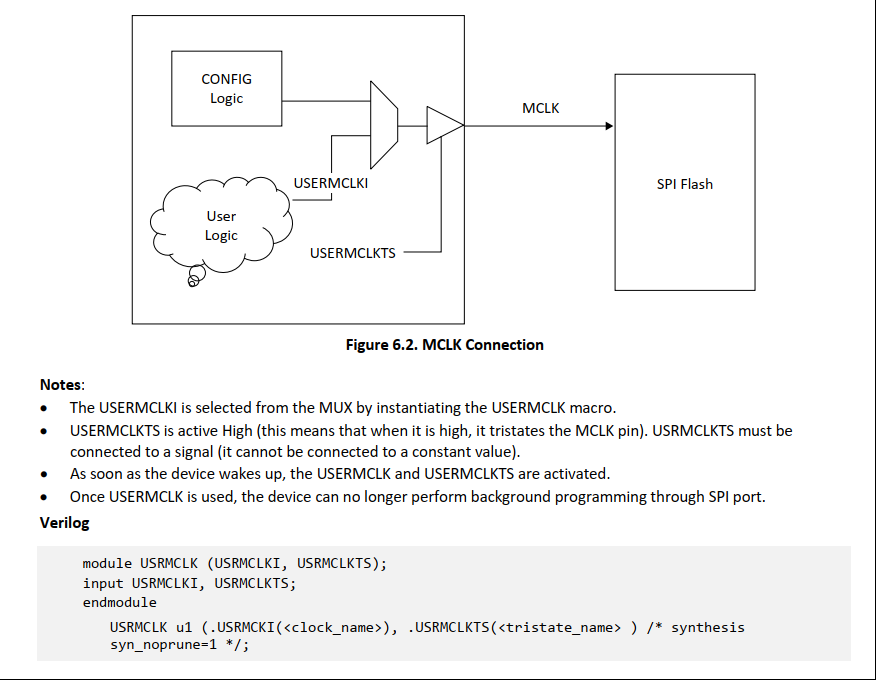

2)調用USRMCLK原語,使用時序邏輯配置USRMCLKTS,

? ? ?上電過程中先是高,然后PLL的lock鎖定后幾個時鐘再把這個信號拉低。

3)將CONEIG IOVOLTAGE設置為3.3

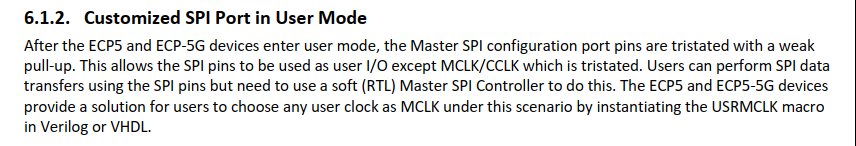

3.USRMCLK原語說明

查看數據手冊<<ECP5 and ECP5-5G sysCONFIG User Guide>>可知,通過調用原語USRMCLK

將切換SPI接口的MCLK引腳時鐘源。

?

module top(//System interface input rst_n,input sys_clk,//Flash interface ? ? ? ? ? ? ? ? ?input spi_miso,output spi_mosi,output spi_cs_n );wire clk_flash;wire pll_locked;reg pll_locked_ff1;reg pll_locked_ff2;reg spi_clk_en;pll_sys u_pll_sys(.CLKI(sys_clk), //50M.CLKOP(clk_flash), //20M.LOCK(pll_locked) );always @(posedge clk_flash or negedge pll_locked)beginif(!pll_locked)beginpll_locked_ff1 <= 1'd0;pll_locked_ff2 <= 1'd0;endelse beginpll_locked_ff1 <= pll_locked;pll_locked_ff2 <= pll_locked_ff1;endendalways @(posedge clk_flash or negedge pll_locked)beginif(!pll_locked)spi_clk_en <= 1'd1;else if(pll_locked_ff2)spi_clk_en <= 1'd0;else;endUSRMCLK u_USRMCLK(.USRMCLKI(spi_clk),.USRMCLKTS(spi_clk_en) ) /* synthesis syn_noprune=1 */;flash_drive flash_drive_u0(.i_clk (clk_flash ),.i_rst (~rst_n ),.i_operation_type (w_operation_type ),.i_operation_addr (w_operation_addr ),.i_operation_num (w_operation_num ),.i_operation_valid (w_operation_valid ),.o_operation_ready (w_operation_ready ),.i_write_data (w_write_data ),.i_write_sop (w_write_sop ),.i_write_eop (w_write_eop ),.i_write_valid (w_write_valid ),.o_read_data (w_read_data ),.o_read_sop (w_read_sop ),.o_read_eop (w_read_eop ),.o_read_valid (w_read_valid ),.o_spi_clk (spi_clk ),.o_spi_cs (o_spi_cs_n ),.o_spi_mosi (o_spi_mosi ),.i_spi_miso (i_spi_miso )

);endmodule4.CONFIG?IOVOLTAGE設置

)

)

)

:你吸收什么,便成為什么)