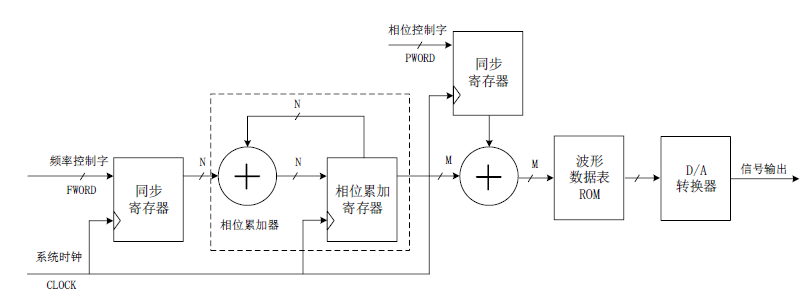

DDS信號發生器原理

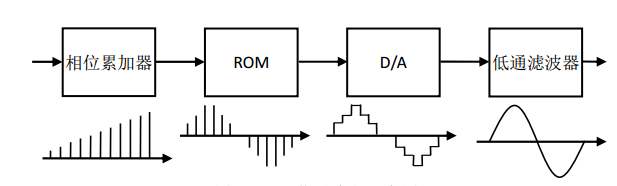

DDS主要由相位累加器、相位調制器、波形數據表以及D/A轉換器構成。其中相位累加器由N位加法器與N位寄存器構成。每個時鐘周期的時鐘上升沿,加法器就將頻率控制字與累加寄存器輸出的相位數據相加,相加的結果又反饋至累加寄存器的數據輸入端,以使加法器在下一個時鐘脈沖的作用下繼續與頻率控制字相加。這樣,相位累加器在時鐘作用下,不斷對頻率控制字進行線性相位累加。即在每一個時鐘脈沖輸入時,相位累加器便把頻率控制字累加一次。

相位累加器輸出的數據就是合成信號的相位。相位累加器的溢出頻率,就是DDS輸出的信號頻率,相位累加器輸出的數據,作為波形存儲器的相位采樣地址,這樣就可以把存儲在波形存儲器里的波形采樣值經查表找出,完成相位到幅度的轉換。

波形存儲器的輸出數據送到 D/A 轉換器,由 D/A 轉換器將數字信號轉換成模擬信號輸出。

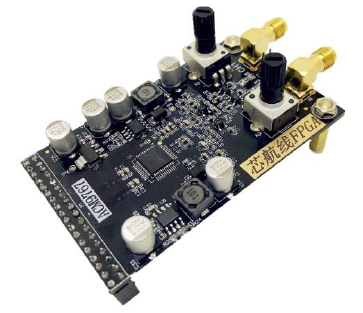

AD9767模塊介紹

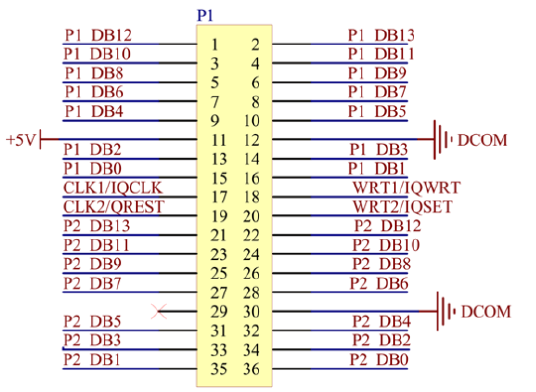

有兩個通道,每個通道的數據分辨率為14位,轉換速率最高可達到125Mbps,輸出電壓范圍為+/-5V。

ACM9767模塊是一款高性能高速雙通道 DAC 模塊。 模塊具有單電源 5V 供電輸入,雙通道數字轉模擬信號輸出,每個通道數據分辨率為 14 位, 輸出電壓范圍為+-5V, 且轉換速率高達125Msps,非常適合諸如信號發生器、數字調制通信系統的開發等應用。

設計要求

- 做一個雙通道的信號發生器

- 能夠簡單的調整每個通道的頻率輸出

- 能夠提哦啊正每個通道的輸出相位

- 能夠控制輸出的波形形式(sine,方波,三角波等)

設計代碼

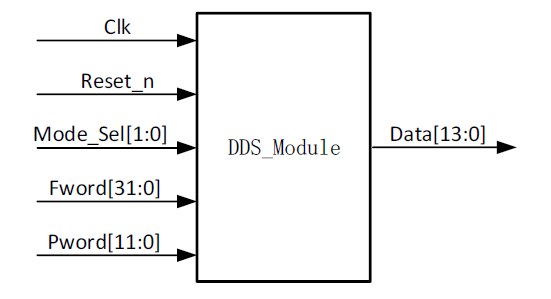

DDS 模塊

module DDS_Module(Clk,Reset_n,Mode_Sel,Fword,Pword,Data

);input Clk;input Reset_n;input [1:0]Mode_Sel; //模式切換input [31:0]Fword;input [11:0]Pword;output reg[13:0]Data;//頻率控制字同步寄存器reg [31:0]Fword_r;always@(posedge Clk)Fword_r <= Fword;//相位控制字同步寄存器reg [11:0]Pword_r;always@(posedge Clk)Pword_r <= Pword; //相位累加器 reg [31:0]Freq_ACC;always@(posedge Clk or negedge Reset_n)if(!Reset_n)Freq_ACC <= 0;elseFreq_ACC <= Fword_r + Freq_ACC;//波形數據表地址wire [11:0]Rom_Addr; assign Rom_Addr = Freq_ACC[31:20] + Pword_r;wire [13:0]Data_sine,Data_square,Data_triangular;

//調用底層模塊ROM表(由ip核生成的三種波形:sine,方波,三角波)rom_sine rom_sine(.clka(Clk),.addra(Rom_Addr),.douta(Data_sine));rom_square rom_square(.clka(Clk),.addra(Rom_Addr),.douta(Data_square));

-- 計算機網絡)

)

學習思路總結)