關注作者了解更多

我的其他CSDN專欄

求職面試

大學英語

過程控制系統

工程測試技術

虛擬儀器技術

可編程控制器

工業現場總線

數字圖像處理

智能控制

傳感器技術

嵌入式系統

復變函數與積分變換

單片機原理

線性代數

大學物理

熱工與工程流體力學

數字信號處理

光電融合集成電路技術

電路原理

模擬電子技術

高等數學

概率論與數理統計

數據結構

C語言

模式識別原理

自動控制原理

數字電子技術

關注作者了解更多

資料來源于網絡,如有侵權請聯系編者

目錄

1.建立工程

2新建Verilog文件

3邏輯設計

5.鎖定引腳

?編輯6.綜合文件

7.生成.bit文件并下載

Xilinx ISE 13.4軟件使用方法本章將以實現一個如圖所示的4為加法器為例,來介紹Xilinx ISE13.4開發流程,并且最終下載到實驗板BASYS2中運行。

1.建立工程

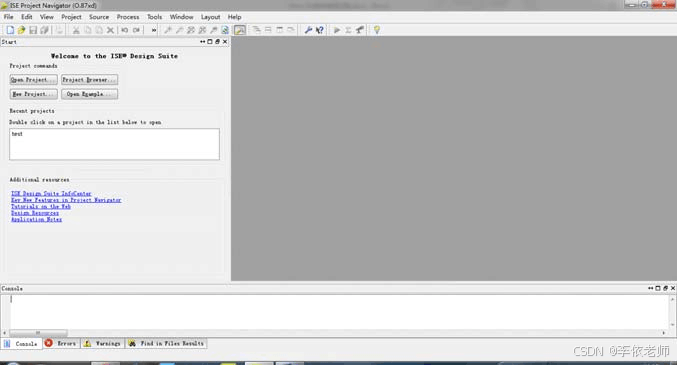

運行Xilinx ISE Design Suite 13.4,初始界面如圖F2所示

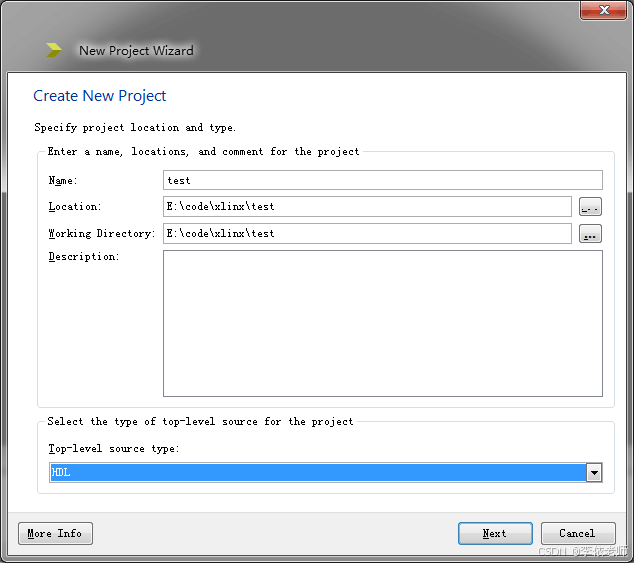

選擇File->New Project,該對話框顯示用向導新建工程所需的步驟。

在Name欄中輸入工程名稱(注意:以下所有不能含有中文字符或空格),如“test”。在Location欄中選擇想要存放的工程位置,如“E:\code\Xilinx\test”。頂層語言選項欄中選擇“HDL”語言。設置向導最終設置效果如圖F2所示

F2 路徑信息設置表

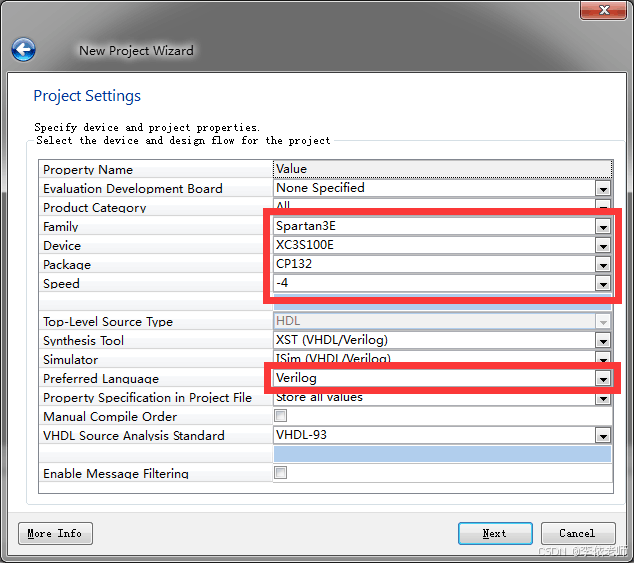

點擊“Next”,進入芯片型號選擇界面。在本界面中,根據BASYS2實驗板上的芯片型號進行相關設置,設置效果如圖F3所示。

F3 芯片信息選擇表

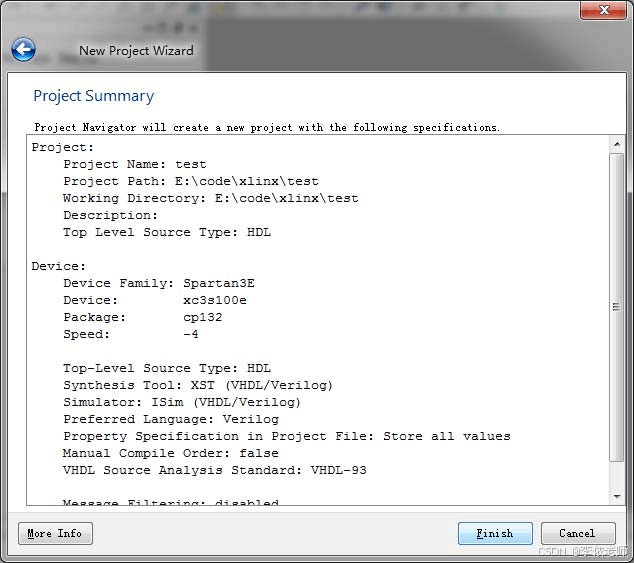

點擊“Next”,出現如圖F4所示工程信息匯總表格。

工程信息匯總表

點擊“Finish”完成設置。

2新建Verilog文件

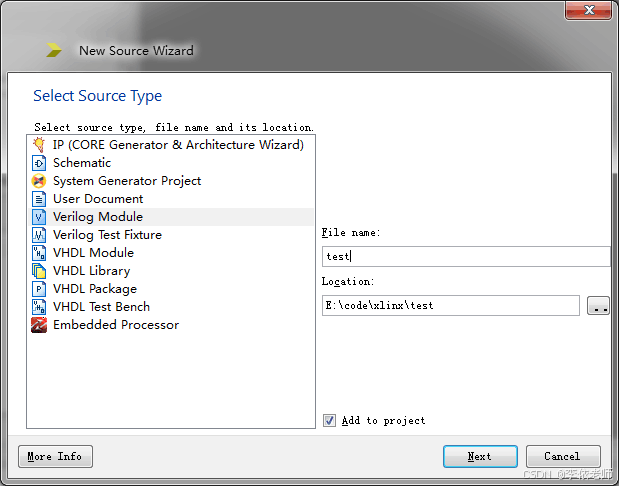

在F5所示界面中,如圖所示的區域內右擊鼠標,選擇“New Source”,出現F6對話框。

在File name欄中鍵入verilog文件的名稱,如“test”。

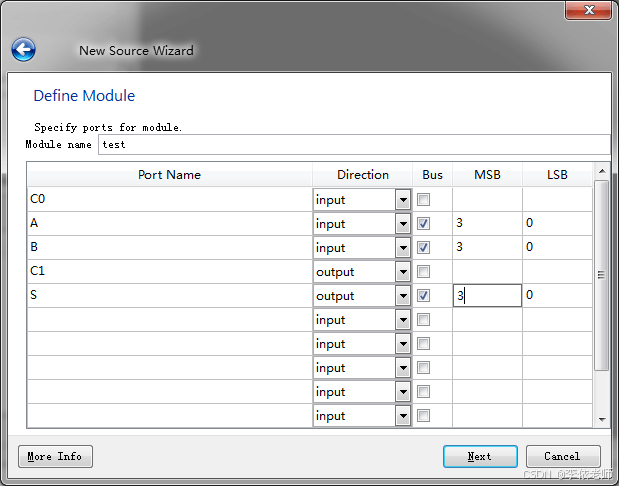

點擊“Next”,在本界面中將設置加法器的輸入輸出引腳數量,如圖F1所示的加法器共有A、B、C0、S和C1,5組引腳,其中A、B和S為4位總線形式,因此設置結果如圖F7所示。

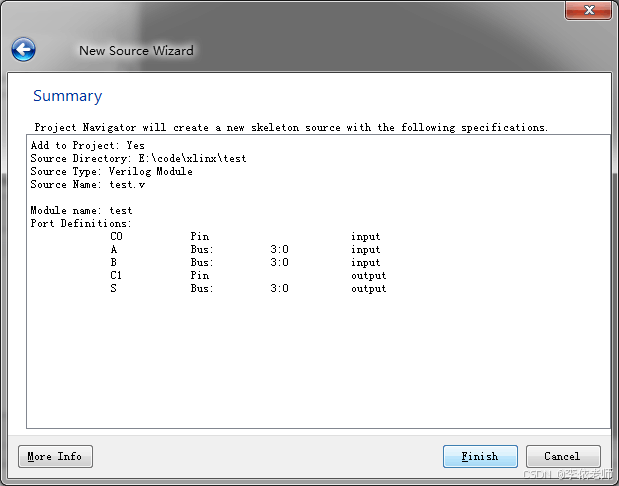

點擊“Next”,出現Verilog新建信息匯總表。

點擊“Finish”,完成Verilog新建工作。

3邏輯設計

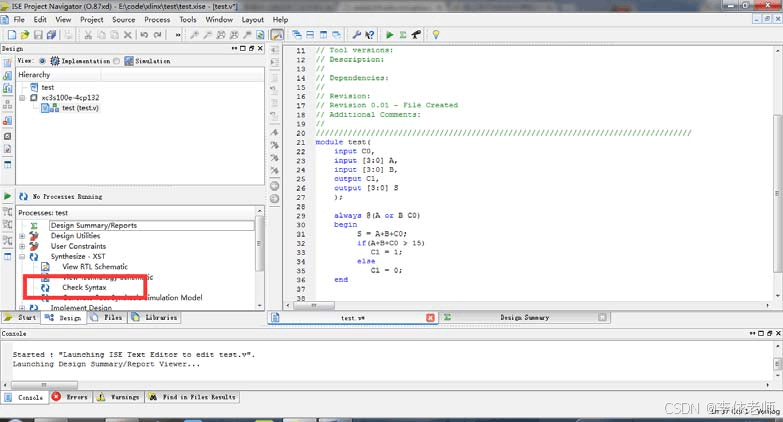

輸入代碼

在輸入完成后,雙擊“Check Syntax”對代碼進行語法檢測。

5.鎖定引腳

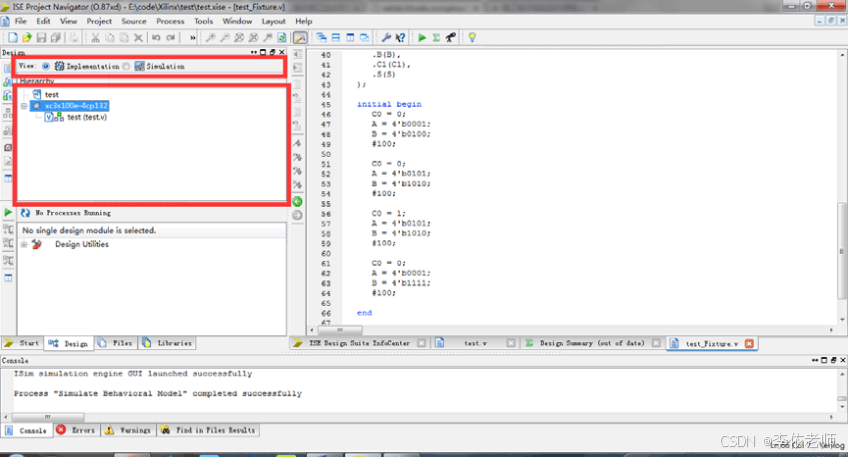

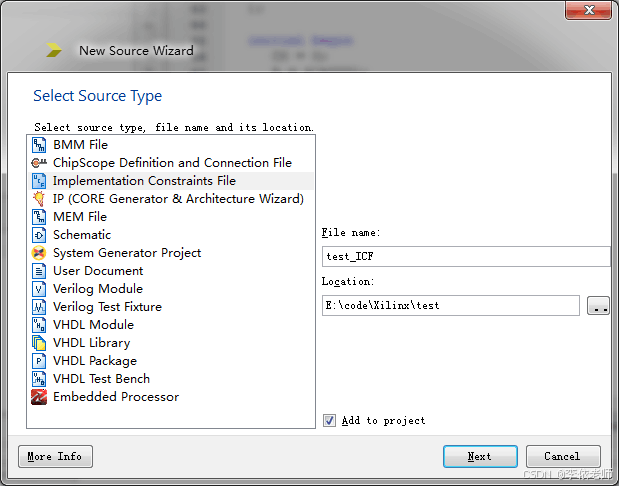

? ? ?關閉仿真界面,顯示如圖F14所示界面,首先將工程切換至“Implementation”狀態,然后在左上區域內右擊鼠標,為工程添加“Implementation Constraints Files”選項。

在“Files Name”選項中命名引腳文件,如“Test_ICF”。

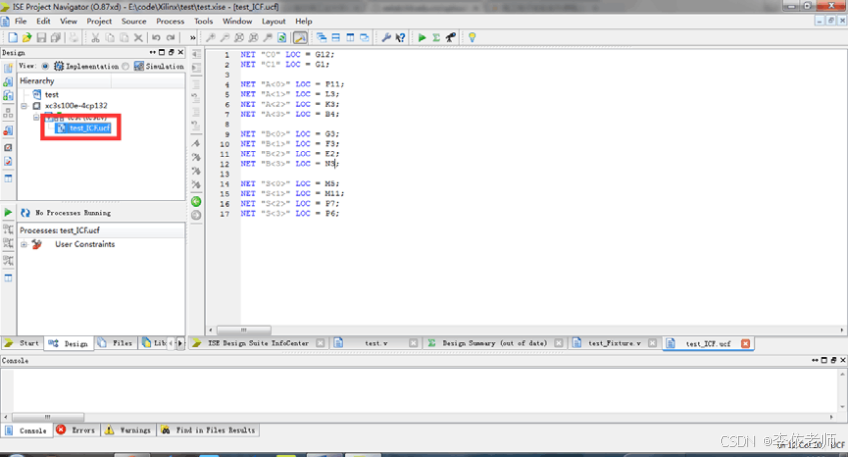

在引腳鎖定文件中,輸入引腳映射關系。效果如圖F16所示。

6.綜合文件

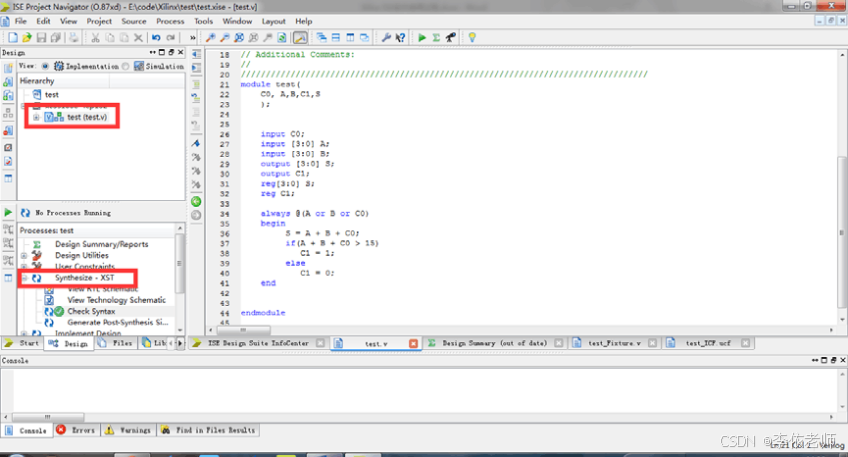

選擇如圖F17所示的test.v文件,然后雙擊“Synthesize - XST”進行綜合。

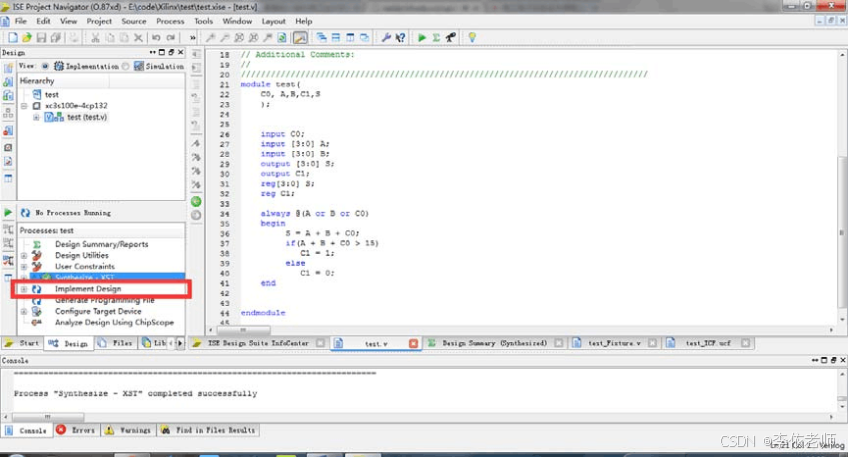

雙擊“Implement Design”。

7.生成.bit文件并下載

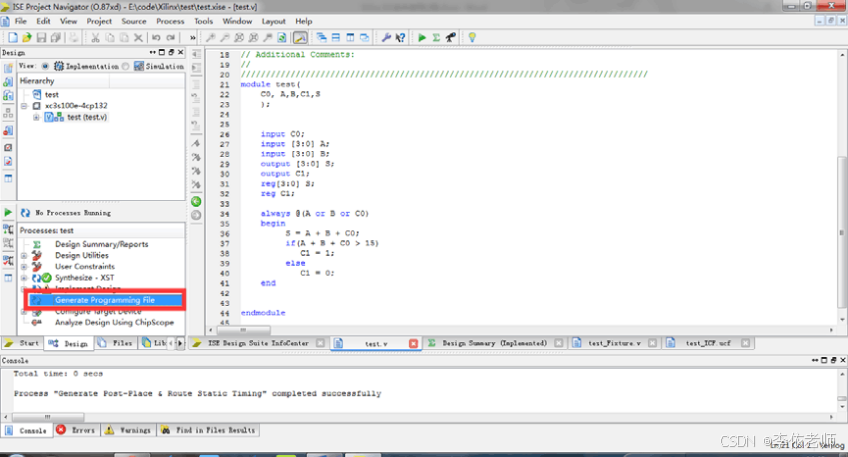

雙擊“Generate Programming Files”文件,生成.bit文件。

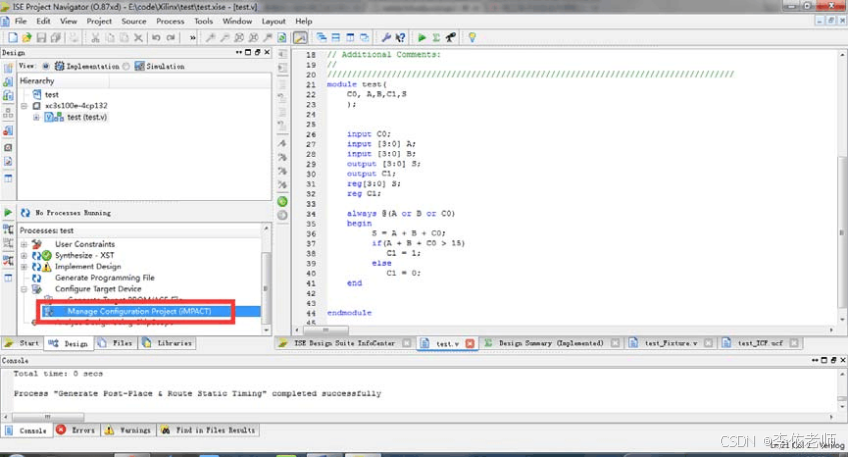

雙擊“Configuration Target Device”->“Management Configuration Project”進入下載

界面。

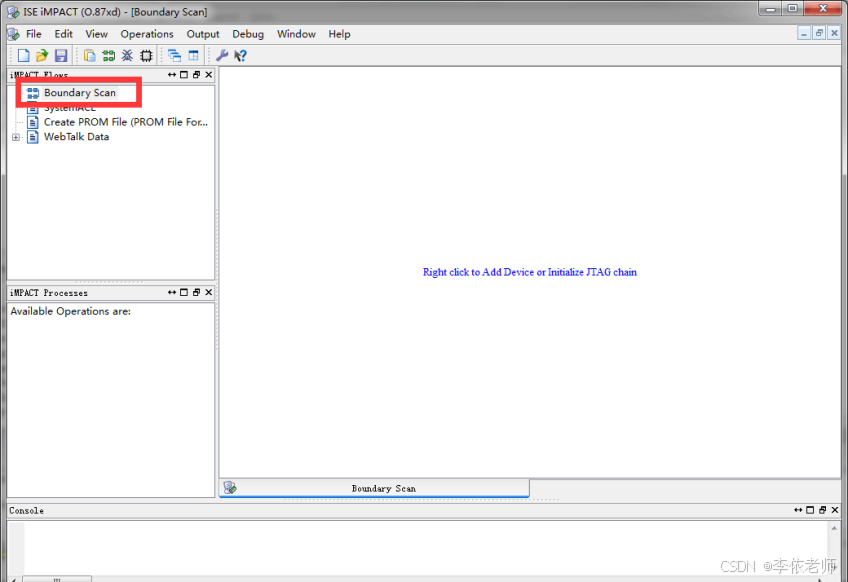

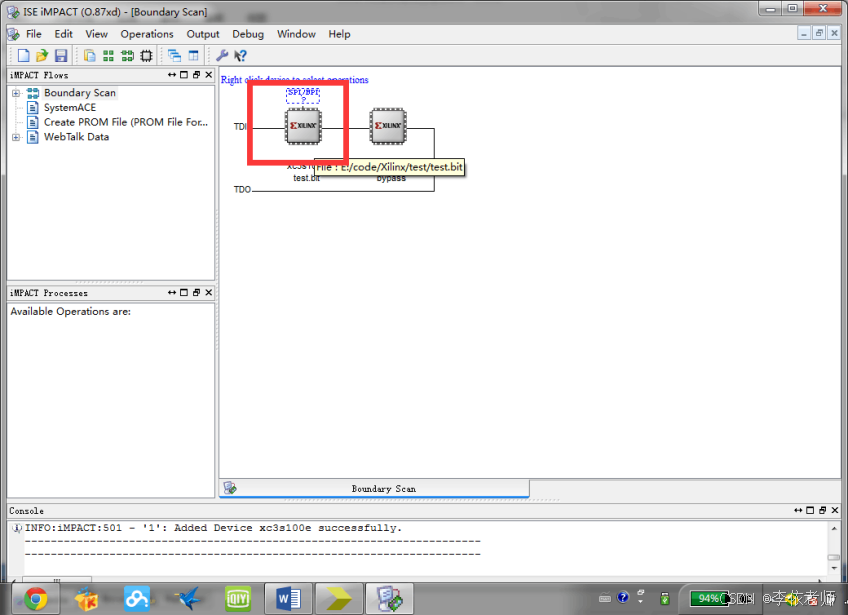

進入下載界面后,雙擊“Boundary Scan”,在右側區域內右擊鼠標,在下拉菜單中選擇“Initialize Chain”。

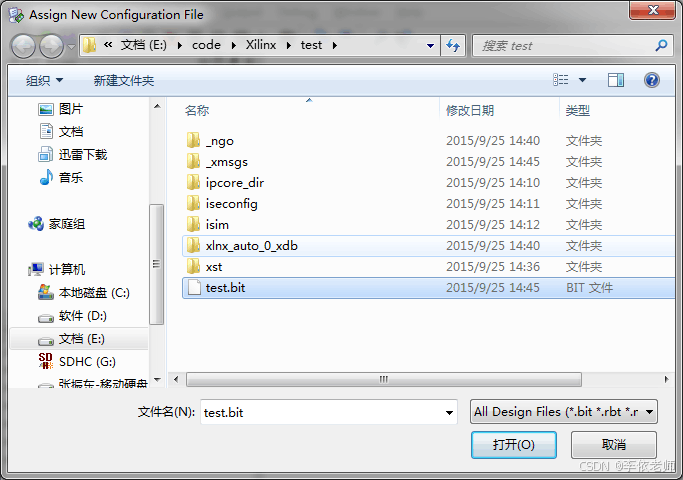

(首先,取消所有彈出的對話框)這時將出現如圖F22所示的界面,然后然后雙擊如圖F22中所框選的芯片,然后選擇已經生成的.bit文件,如圖F23所示。

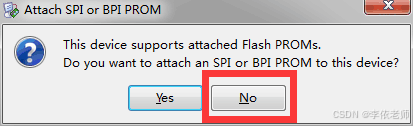

在彈出的對話框中,選擇“No”

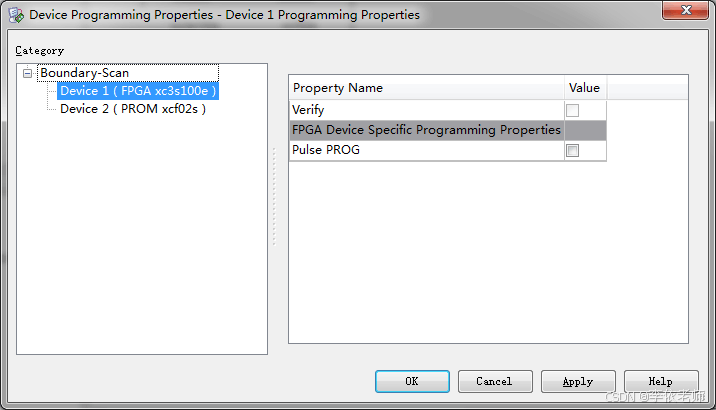

然后,鼠標右鍵選擇圖F22中的芯片,選擇下拉菜單中的“Program”選項。在確認彈出的對話框中的芯片信息后,點擊“OK”進行下載。

BASYS2開發板引腳分配表

引腳名

引腳號 注釋

引腳名 引腳號 注釋

SW[0] P11 撥碼開關

BTN[0] G12 按鍵,按下時對應高電平

SW[1] L3 BTN[1] C11 SW[2] K3 BTN[2] M4 SW[3] B4 BTN[3]

A7 SW[4] G3 CA L14 數碼管對應的字段

SW[5] F3 CB H12 SW[6] E2 CC N14 SW[7] N3 CD N11 LED[0] M5 LED 指示燈,高電平時點亮CE P12 LED[1] M11 CF L13 LED[2] P7 CG

M12 LED[3] P6 DP N13 LED[4] N5 AN[0]

K14 數碼管對應的選通字段 LED[5] N4 AN[1] C11 LED[6] P4 AN[2] M4 LED[7] G1 AN[3]

A7 CLK_50

B8

50M 時鐘輸入

)

】)

實現每 5 分鐘的增量任務)

基本信息查看)