目錄

- 1、前言

- 工程概述

- 免責聲明

- 2、相關方案推薦

- 本博已有的 SDI 編解碼方案

- 本博已有的以太網方案

- 本博已有的FPGA圖像縮放方案

- 1G/2.5G Ethernet PCS/PMA or SGMII架構以太網通信方案

- AXI 1G/2.5G Ethernet Subsystem架構以太網通信方案

- 本方案的縮放應用

- 本方案在Xilinx--Kintex系列FPGA上的應用

- 3、詳細設計方案

- 設計原理框圖

- SDI 輸入設備

- Gv8601a 均衡器

- GTX 解串與串化

- SMPTE SD/HD/3G SDI IP核

- BT1120轉RGB

- 純Verilog圖像縮放模塊詳解

- 純Verilog圖像縮放模塊使用

- 圖像緩存

- UDP協議棧

- UDP視頻發送

- UDP協議棧數據發送

- MAC數據緩沖FIFO組

- IP地址、端口號的修改

- PHY芯片-->以太網網口輸出方案

- Tri Mode Ethernet MAC

- 1G/2.5G Ethernet PCS/PMA or SGMII-->以太網光口輸出方案

- 1G/2.5G Ethernet PCS/PMA or SGMII 簡介

- 1G/2.5G Ethernet PCS/PMA or SGMII 配置

- Tri Mode Ethernet MAC

- AXI 1G/2.5G Ethernet Subsystem-->以太網光口輸出方案

- AXI 1G/2.5G Ethernet Subsystem 簡介

- AXI 1G/2.5G Ethernet Subsystem 配置

- QT上位機和源碼

- 工程源碼架構

- 4、工程源碼1詳解-->PHY芯片以太網輸出方案

- 5、工程源碼2詳解-->1G/2.5G Ethernet PCS/PMA or SGMII以太網輸出方案

- 6、工程源碼3詳解-->AXI 1G/2.5G Ethernet Subsystem以太網輸出方案

- 7、工程移植說明

- vivado版本不一致處理

- FPGA型號不一致處理

- 其他注意事項

- 8、上板調試驗證

- 準備工作

- 輸出視頻演示

- 9、福利:工程代碼的獲取

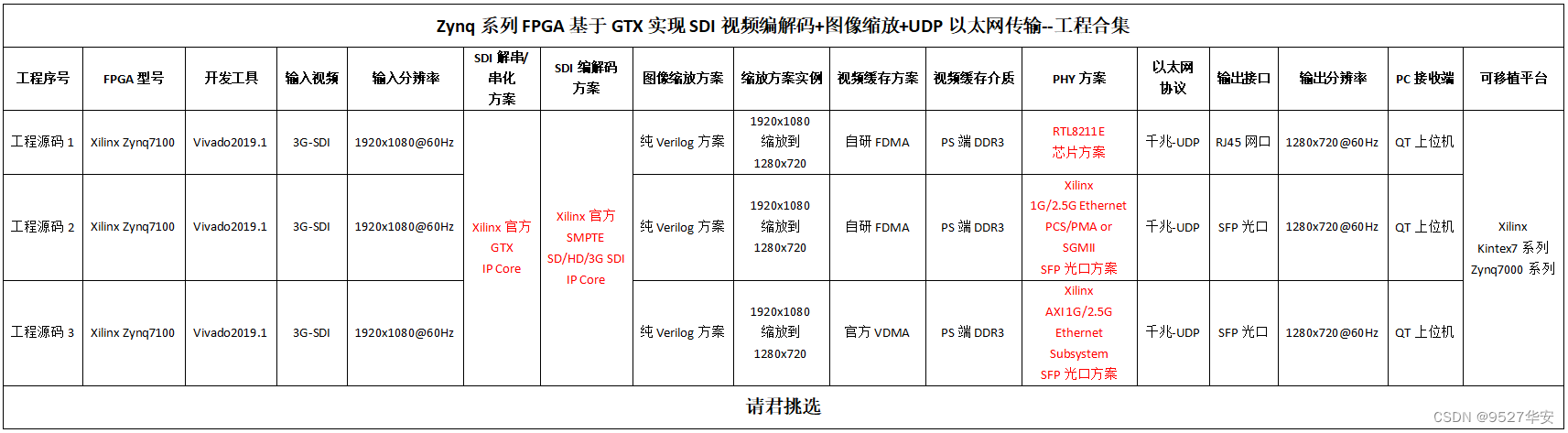

Zynq系列FPGA實現SDI視頻編解碼+UDP以太網傳輸,基于GTX高速接口,提供3套工程源碼和技術支持

1、前言

目前FPGA實現SDI視頻編解碼有兩種方案:一是使用專用編解碼芯片,比如典型的接收器GS2971,發送器GS2972,優點是簡單,比如GS2971接收器直接將SDI解碼為并行的YCrCb422,GS2972發送器直接將并行的YCrCb422編碼為SDI視頻,缺點是成本較高,可以百度一下GS2971和GS2972的價格;另一種方案是使用FPGA邏輯資源部實現SDI編解碼,利用Xilinx系列FPGA的GTP/GTX資源實現解串,利用Xilinx系列FPGA的SMPTE SDI資源實現SDI編解碼,優點是合理利用了FPGA資源,GTP/GTX資源不用白不用,缺點是操作難度大一些,對FPGA開發者的技術水平要求較高。有意思的是,這兩種方案在本博這里都有對應的解決方案,包括硬件的FPGA開發板、工程源碼等等。

工程概述

本設計基于Zynq系列的Zynq7100 FPGA開發板實現SDI視頻編解碼+圖像縮放+UDP以太網傳輸,輸入源為一個3G-SDI相機或者HDMI轉3G-SDI盒子,也可以使用HD-SDI或者SD-SDI相機,因為本設計是三種SDI視頻自適應的;同軸的SDI視頻通過同軸線連接到FPGA開發板的BNC座子,然后同軸視頻經過板載的Gv8601a芯片實現單端轉差分和均衡EQ的功能;然后差分SDI視頻信號進入FPGA內部的GTX高速資源,實現數據高速串行到并行的轉換,本博稱之為解串;解串后的并行視頻再送入Xilinx系列FPGA特有的SMPTE SD/HD/3G SDI IP核,進行SDI視頻解碼操作并輸出BT1120視頻,至此,SDI視頻解碼操作已經完成,可以進行常規的圖像處理操作了;

本設計的目的是做圖像縮放后再以UDP以太網輸出解碼的SDI視頻,針對目前市面上的主流項目需求,本博設計了三種以太網輸出方式,第一種是基于傳統PHY芯片(RTL8211E)輸出,第一種是基于Xilinx官方的1G/2.5G Ethernet PCS/PMA or SGMII+Tri Mode Ethernet MAC架構輸出,第一種是基于Xilinx官方的AXI 1G/2.5G Ethernet Subsystem架構輸出;首先對解碼BT1120視頻進行轉RGB和圖像緩存操作和圖像縮放操作;圖像縮放方案采用純verilog方案將輸入的1920x1080視頻縮放為1280x720;再使用BT1120轉RGB模塊實現視頻格式轉換;再使用本博常用的FDMA圖像緩存架構實現圖像3幀緩存,緩存介質為板載的PS端DDR3;圖像從DDR3讀出后,進入UDP視頻發送模塊,對視頻進行自定義協議編碼;然后送入UDP協議棧進行UDP以太網幀格式編碼;然后輸出給MAC層,再輸出給物理層,最后通過網線輸出給PC上位機;PC端上位機(QT)接收網絡視頻并顯示圖像;本博客提供3套工程源碼,具體如下:

現對上述3套工程源碼做如下解釋,方便讀者理解:

工程源碼1

開發板FPGA型號為Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2;輸入視頻為3G-SDI相機或者HDMI轉3G-SDI盒子,輸入分辨率為1920x1080@60Hz,輸入視頻經過板載的Gv8601a芯片實現單端轉差分和均衡EQ后送入FPGA;再經過GTX將SDI視頻解串為并行數據;再經過SMPTE SDI IP核將SDI解碼BT1120數據;再經過BT1120轉RGB模塊將BT1120轉換為RGB888視頻;再經過自研的純verilog實現的、支持任意比例縮放的圖像縮放模塊,將輸入視頻由1920x1080縮放為1280x720;再經過自研的FDMA圖像緩存方案將視頻寫入PS側DDR3做三幀緩存;再經過UDP視頻發送模塊,對視頻進行自定義協議編碼;再經過UDP協議棧進行UDP以太網幀格式編碼;再經過Xilinx官方的Tri Mode Ethernet MAC實現MAC數據發送,輸出RGMII接口數據;再經過板載的RTL8211E芯片后以RJ45網口輸出;PC端運行QT上位機實時接收視頻數據并顯示出來;該工程運行Zynq軟核;適用于SDI轉網絡(PHY芯片方案)輸出場景;

工程源碼2

開發板FPGA型號為Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2;輸入視頻為3G-SDI相機或者HDMI轉3G-SDI盒子,輸入分辨率為1920x1080@60Hz,輸入視頻經過板載的Gv8601a芯片實現單端轉差分和均衡EQ后送入FPGA;經過GTX將SDI視頻解串為并行數據;再經過SMPTE SDI IP核將SDI解碼BT1120數據;再經過BT1120轉RGB模塊將BT1120轉換為RGB888視頻;再經過自研的純verilog實現的、支持任意比例縮放的圖像縮放模塊,將輸入視頻由1920x1080縮放為1280x720;再經過自研的FDMA圖像緩存方案將視頻寫入PS側DDR3做三幀緩存;再經過UDP視頻發送模塊,對視頻進行自定義協議編碼;再經過UDP協議棧進行UDP以太網幀格式編碼;再經過Xilinx官方的1G/2.5G Ethernet PCS/PMA or SGMII+Tri Mode Ethernet MAC架構實現MAC數據發送,輸出到板載的SFP光口;再經過SFP光口轉網口(電口)后以網線輸出;PC端運行QT上位機實時接收視頻數據并顯示出來;該工程運行Zynq軟核;適用于SDI轉網絡(光口方案)輸出場景;

工程源碼3

開發板FPGA型號為Xilinx–>Xilinx-Zynq7100–xc7z100ffg900-2;輸入視頻為3G-SDI相機或者HDMI轉3G-SDI盒子,輸入分辨率為1920x1080@60Hz,輸入視頻經過板載的Gv8601a芯片實現單端轉差分和均衡EQ后送入FPGA;經過GTX將SDI視頻解串為并行數據;再經過SMPTE SDI IP核將SDI解碼BT1120數據;再經過BT1120轉RGB模塊將BT1120轉換為RGB888視頻;再經過自研的純verilog實現的、支持任意比例縮放的圖像縮放模塊,將輸入視頻由1920x1080縮放為1280x720;再經過自研的FDMA圖像緩存方案將視頻寫入PS側DDR3做三幀緩存;再經過UDP視頻發送模塊,對視頻進行自定義協議編碼;再經過UDP協議棧進行UDP以太網幀格式編碼;再經過Xilinx官方的AXI 1G/2.5G Ethernet Subsystem架構實現MAC數據發送,輸出到板載的SFP光口;再經過SFP光口轉網口(電口)后以網線輸出;PC端運行QT上位機實時接收視頻數據并顯示出來;該工程運行Zynq軟核;適用于SDI轉網絡(光口方案)輸出場景;

免責聲明

本工程及其源碼即有自己寫的一部分,也有網絡公開渠道獲取的一部分(包括CSDN、Xilinx官網、Altera官網等等),若大佬們覺得有所冒犯,請私信批評教育;基于此,本工程及其源碼僅限于讀者或粉絲個人學習和研究,禁止用于商業用途,若由于讀者或粉絲自身原因用于商業用途所導致的法律問題,與本博客及博主無關,請謹慎使用。。。

2、相關方案推薦

本博已有的 SDI 編解碼方案

我的博客主頁開設有SDI視頻專欄,里面全是FPGA編解碼SDI的工程源碼及博客介紹;既有基于GS2971/GS2972的SDI編解碼,也有基于GTP/GTX資源的SDI編解碼;既有HD-SDI、3G-SDI,也有6G-SDI、12G-SDI等;專欄地址鏈接如下:

點擊直接前往

本博已有的以太網方案

目前我這里有大量UDP協議的工程源碼,包括UDP數據回環,視頻傳輸,AD采集傳輸等,也有TCP協議的工程,對網絡通信有需求的兄弟可以去看看,以下是專欄地址:

直接點擊前往

本博已有的FPGA圖像縮放方案

我的主頁目前有FPGA圖像縮放專欄,改專欄收錄了我目前手里已有的FPGA圖像縮放方案,從實現方式分類有基于HSL實現的圖像縮放、基于純verilog代碼實現的圖像縮放;從應用上分為單路視頻圖像縮放、多路視頻圖像縮放、多路視頻圖像縮放拼接;從輸入視頻分類可分為OV5640攝像頭視頻縮放、SDI視頻縮放、MIPI視頻縮放等等;以下是專欄地址:

點擊直接前往

1G/2.5G Ethernet PCS/PMA or SGMII架構以太網通信方案

1G/2.5G Ethernet PCS/PMA or SGMII+Tri Mode Ethernet MAC架構以太網通信方案可實現無PHY芯片的以太網通信,之前專門寫過一篇博客,博客地址鏈接如下:

點擊直接前往

AXI 1G/2.5G Ethernet Subsystem架構以太網通信方案

AXI 1G/2.5G Ethernet Subsystem架構以太網通信方案可實現無PHY芯片的以太網通信,之前專門寫過一篇博客,博客地址鏈接如下:

點擊直接前往

本方案的縮放應用

本方案有縮放版本的應用,只做SDI視頻編解碼,之前專門寫過一篇博客,博客地址鏈接如下:

點擊直接前往

本方案在Xilinx–Kintex系列FPGA上的應用

本方案在Xilinx–Kintex系列FPGA上的也有應用,之前專門寫過一篇博客,博客地址鏈接如下:

點擊直接前往

3、詳細設計方案

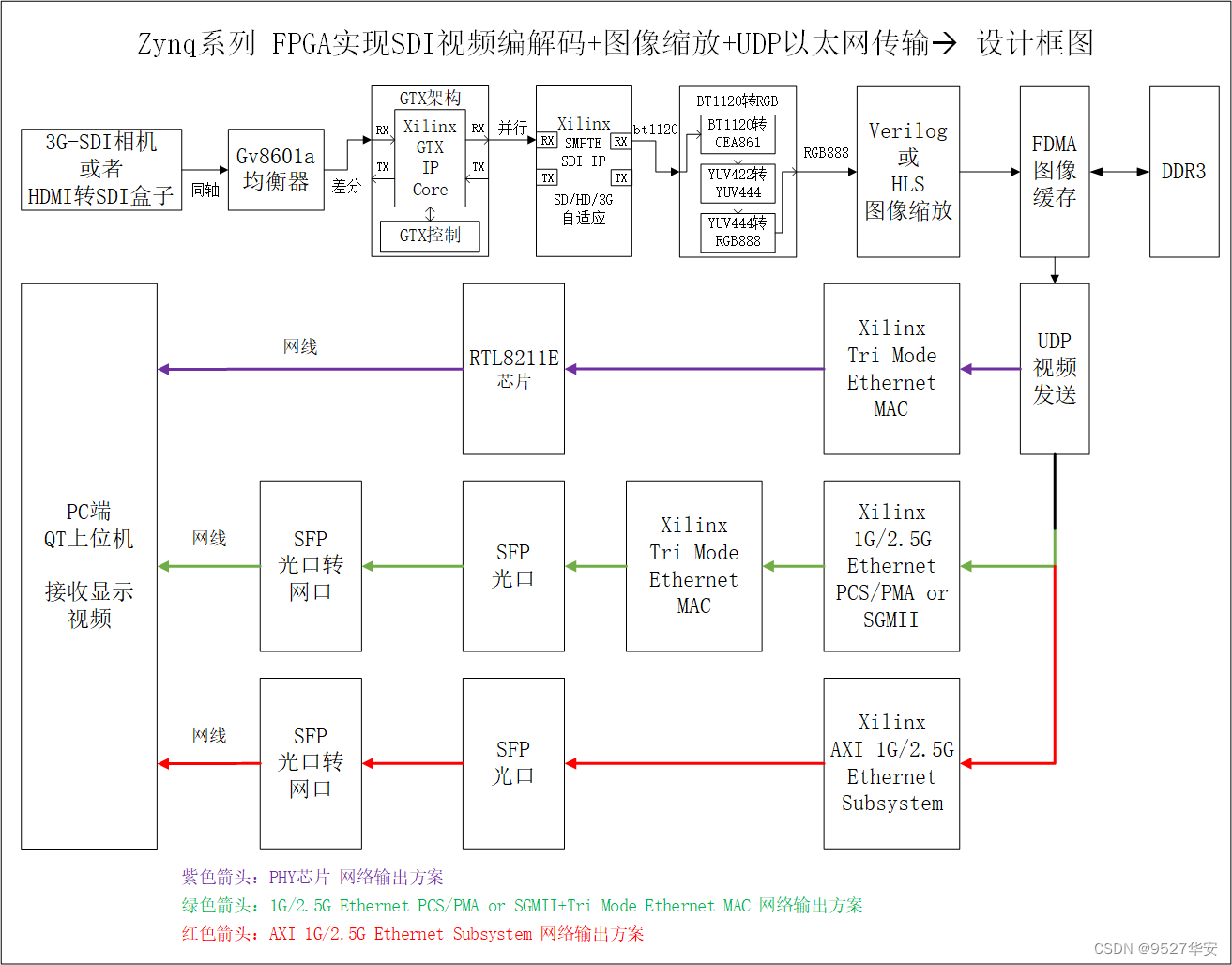

設計原理框圖

設計原理框圖如下:

注意!!!!

注意!!!!

紫色箭頭:PHY芯片的網絡輸出方案,需要外接PHY芯片;

綠色箭頭:1G/2.5G Ethernet PCS/PMA or SGMII+Tri Mode Ethernet MAC架構的網絡輸出方案,不需要外接PHY芯片,由SFP光口輸出;

紅色箭頭:AXI 1G/2.5G Ethernet Subsystem架構的網絡輸出方案,不需要外接PHY芯片,由SFP光口輸出;

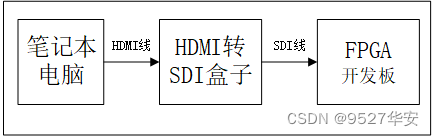

SDI 輸入設備

SDI 輸入設備可以是SDI相機,代碼兼容HD/SD/3G-SDI三種模式;SDI相機相對比較貴,預算有限的朋友可以考慮用HDMI轉SDI盒子模擬SDI相機,這種盒子某寶一百塊左右;當使用HDMI轉SDI盒子時,輸入源可以用筆記本電腦,即用筆記本電腦通過HDMI線連接到HDMI轉SDI盒子的HDMI輸入接口,再用SDI線連接HDMI轉SDI盒子的SDI輸出接口到FPGA開發板,如下:

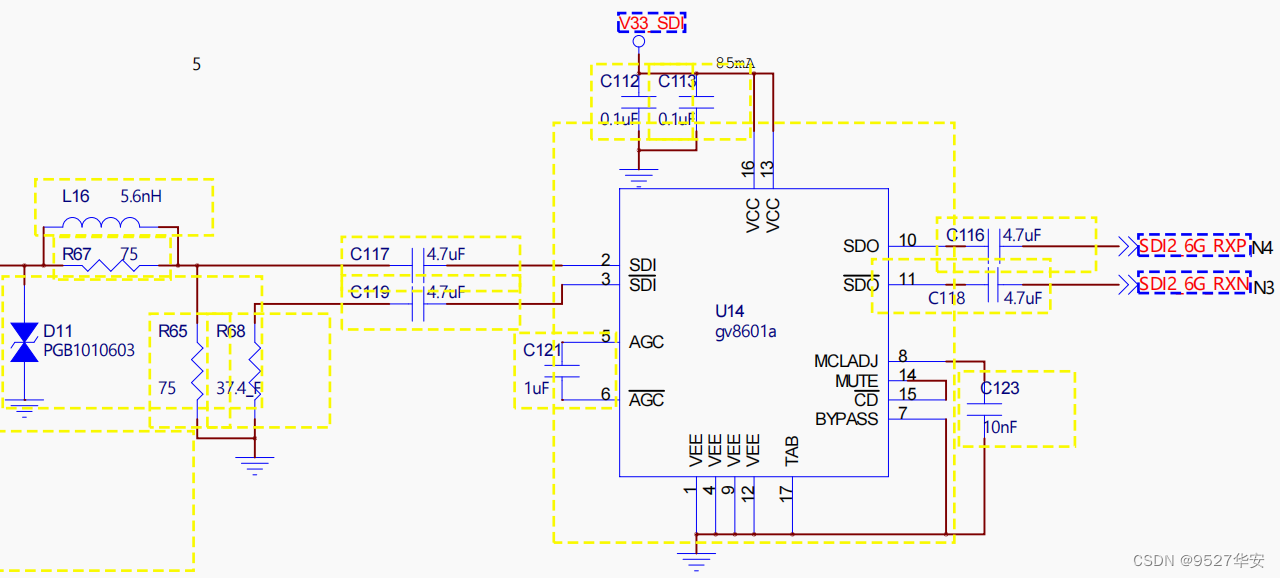

Gv8601a 均衡器

Gv8601a芯片實現單端轉差分和均衡EQ的功能,這里選用Gv8601a是因為借鑒了了Xilinx官方的方案,當然也可以用其他型號器件。Gv8601a均衡器原理圖如下:

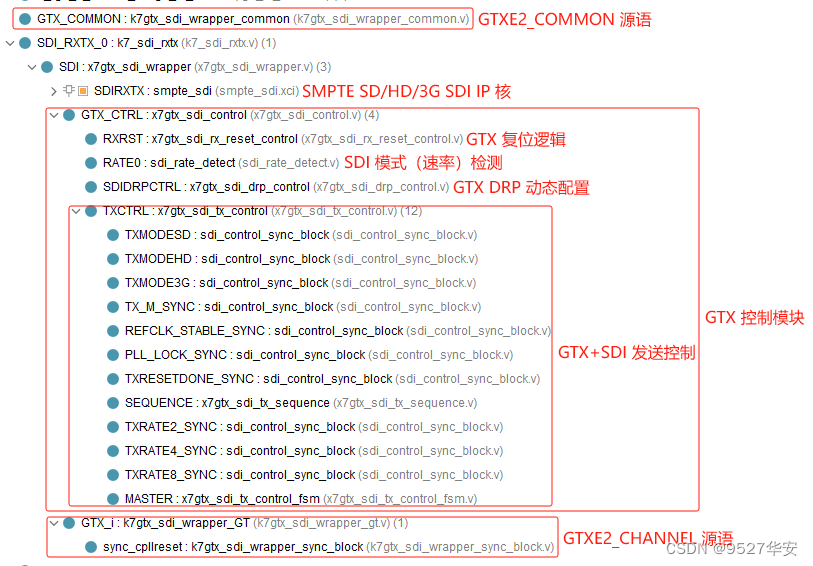

GTX 解串與串化

本設計使用Xilinx特有的GTX高速信號處理資源實現SDI差分視頻信號的解串與串化,對于SDI視頻接收而言,GTX起到解串的作用,即將輸入的高速串行的差分信號解為并行的數字信號;對于SDI視頻發送而言,GTX起到串化的作用,即將輸入的并行的數字信號串化為高速串行的差分信號;GTX的使用一般需要例化GTX IP核,通過vivado的UI界面進行配置,但本設計需要對SD-SDI、HD-SDI、3G-SDI視頻進行自動識別和自適應處理,所以需要使得GTX具有動態改變線速率的功能,該功能可通過DRP接口配置,也可通過GTX的rate接口配置,所以不能使用vivado的UI界面進行配置,而是直接例化GTX的GTXE2_CHANNEL和GTXE2_COMMON源語直接使用GTX資源;此外,為了動態配置GTX線速率,還需要GTX控制模塊,該模塊參考了Xilinx的官方設計方案,具有動態監測SDI模式,動態配置DRP等功能;該方案參考了Xilinx官方的設計;GTX 解串與串化模塊代碼架構如下:

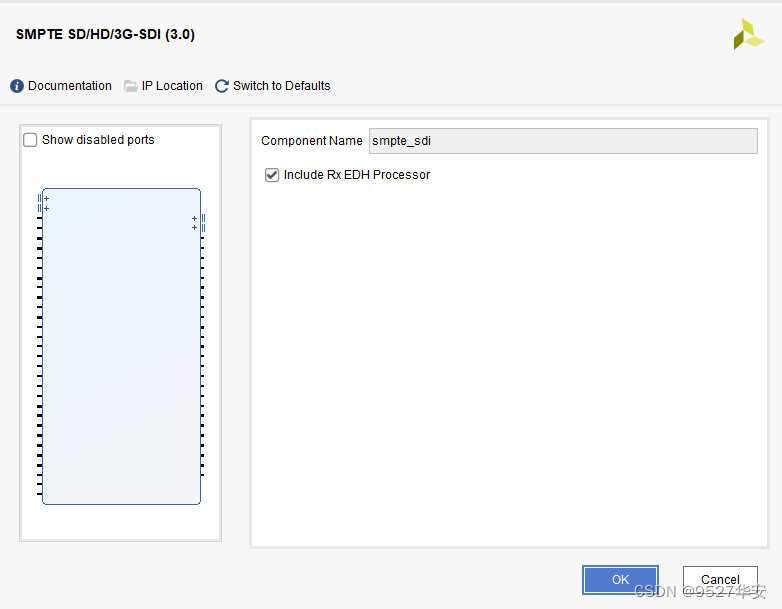

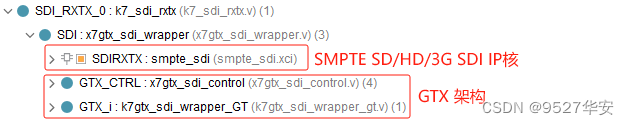

SMPTE SD/HD/3G SDI IP核

SMPTE SD/HD/3G SDI IP核是Xilinx系列FPGA特有的用于SDI視頻編解碼的IP,該IP配置使用非常簡單,vivado的UI界面如下:

SMPTE SD/HD/3G SDI IP核必須與GTX配合才能使用,對于SDI視頻接收而言,該IP接收來自于GTX的數據,然后將SDI視頻解碼為BT1120視頻輸出,對于SDI視頻發送而言,該IP接收來自于用戶側的的BT1120視頻數據,然后將BT1120視頻編碼為SDI視頻輸出;該方案參考了Xilinx官方的設計;SMPTE SD/HD/3G SDI IP核代碼架構如下:

BT1120轉RGB

BT1120轉RGB模塊的作用是將SMPTE SD/HD/3G SDI IP核解碼輸出的BT1120視頻轉換為RGB888視頻,它由BT1120轉CEA861模塊、YUV422轉YUV444模塊、YUV444轉RGB888三個模塊組成,該方案參考了Xilinx官方的設計;BT1120轉RGB模塊代碼架構如下:

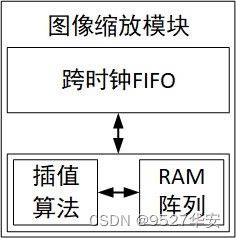

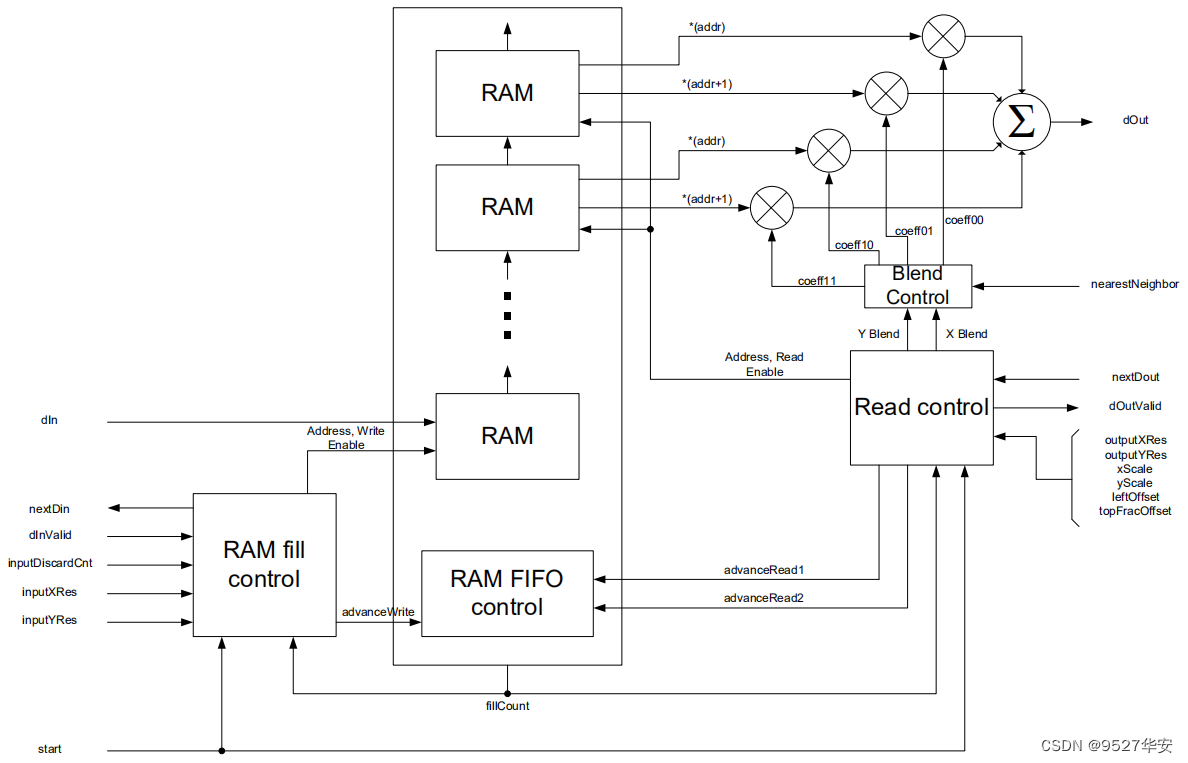

純Verilog圖像縮放模塊詳解

工程源碼1、2的圖像縮放模塊使用純Verilog方案,功能框圖如下,由跨時鐘FIFO、插值+RAM陣列構成,跨時鐘FIFO的目的是解決跨時鐘域的問題,比如從低分辨率視頻放大到高分辨率視頻時,像素時鐘必然需要變大,這是就需要異步FIFO了,插值算法和RAM陣列具體負責圖像縮放算法層面的實現;

插值算法和RAM陣列以ram和fifo為核心進行數據緩存和插值實現,設計架構如下:

圖像縮放模塊代碼架構如下:模塊的例化請參考工程源碼的頂層代碼;

圖像縮放模塊FIFO的選擇可以調用工程對應的vivado工具自帶的FIFO IP核,也可以使用純verilog實現的FIFO,可通過接口參數選擇,圖像縮放模塊頂層接口如下:

module helai_video_scale #(//---------------------------Parameters----------------------------------------parameter FIFO_TYPE = "xilinx", // "xilinx" for xilinx-fifo ; "verilog" for verilog-fifoparameter DATA_WIDTH = 8 , //Width of input/output dataparameter CHANNELS = 1 , //Number of channels of DATA_WIDTH, for color imagesparameter INPUT_X_RES_WIDTH = 11 //Widths of input/output resolution control signals

)(input i_reset_n , // 輸入--低電平復位信號input [INPUT_X_RES_WIDTH-1:0] i_src_video_width , // 輸入視頻--即縮放前視頻的寬度input [INPUT_X_RES_WIDTH-1:0] i_src_video_height, // 輸入視頻--即縮放前視頻的高度input [INPUT_X_RES_WIDTH-1:0] i_des_video_width , // 輸出視頻--即縮后前視頻的寬度input [INPUT_X_RES_WIDTH-1:0] i_des_video_height, // 輸出視頻--即縮后前視頻的高度input i_src_video_pclk , // 輸入視頻--即縮前視頻的像素時鐘input i_src_video_vs , // 輸入視頻--即縮前視頻的場同步信號,必須為高電平有效input i_src_video_de , // 輸入視頻--即縮前視頻的數據有效信號,必須為高電平有效input [DATA_WIDTH*CHANNELS-1:0] i_src_video_pixel , // 輸入視頻--即縮前視頻的像素數據input i_des_video_pclk , // 輸出視頻--即縮后視頻的像素時鐘,一般為寫入DDR緩存的時鐘output o_des_video_vs , // 輸出視頻--即縮后視頻的場同步信號,高電平有效output o_des_video_de , // 輸出視頻--即縮后視頻的數據有效信號,高電平有效output [DATA_WIDTH*CHANNELS-1:0] o_des_video_pixel // 輸出視頻--即縮后視頻的像素數據

);

FIFO_TYPE選擇原則如下:

1:總體原則,選擇"xilinx"好處大于選擇"verilog";

2:當你的FPGA邏輯資源不足時,請選"xilinx";

3:當你圖像縮放的視頻分辨率較大時,請選"xilinx";

4:當你的FPGA沒有FIFO IP或者FIFO IP快用完了,請選"verilog";

5:當你向自學一下異步FIFO時,,請選"verilog";

6:不同FPGA型號對應的工程FIFO_TYPE參數不一樣,但選擇原則一樣,具體參考代碼;

2種插值算法的整合與選擇

本設計將常用的雙線性插值和鄰域插值算法融合為一個代碼中,通過輸入參數選擇某一種算法;

具體選擇參數如下:

input wire i_scaler_type //0-->bilinear;1-->neighbor

通過輸入i_scaler_type 的值即可選擇;

輸入0選擇雙線性插值算法;

輸入1選擇鄰域插值算法;

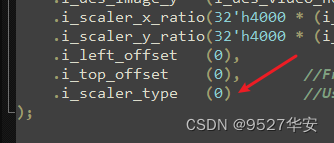

代碼里的配置如下:

純Verilog圖像縮放模塊使用

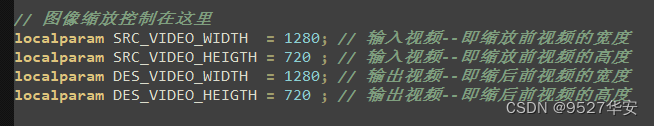

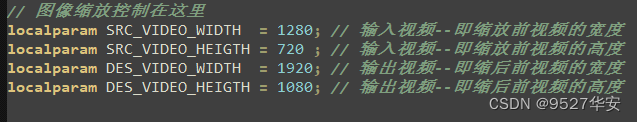

圖像縮放模塊使用非常簡單,頂層代碼里設置了四個參數,舉例如下:

上圖視頻通過圖像縮放模塊但不進行縮放操作,旨在掌握圖像縮放模塊的用法;如果需要將圖像放大到1080P,則修改為如下:

當然,需要修改的不僅僅這一個地方,FDMA的配置也需要相應修改,詳情請參考代碼,但我想要證明的是,圖像縮放模塊使用非常簡單,你都不需要知道它內部具體怎么實現的,上手就能用;

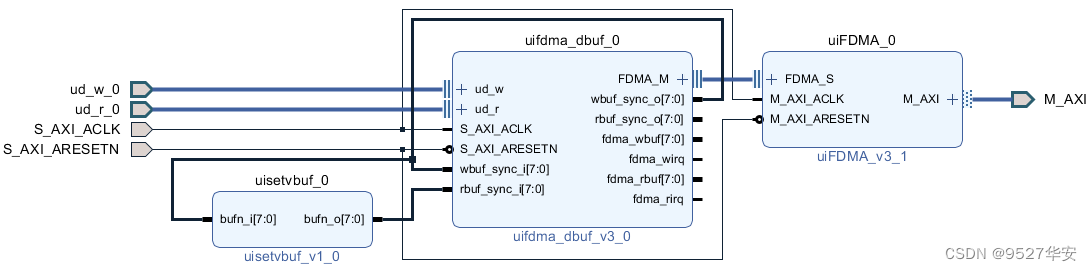

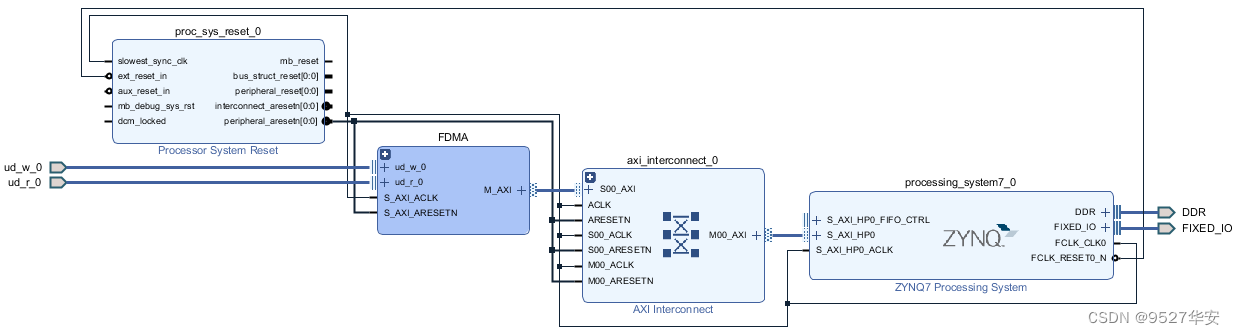

圖像緩存

使用本博常用的的FDMA圖像緩存架構;緩存介質為PS端DDR3;FDMA圖像緩存架構由FDMA、FDMA控制器、緩存幀選擇器構成;圖像緩存使用Xilinx vivado的Block Design設計,如下圖:

關于FDMA更詳細的介紹,請參考我之前的博客,博文鏈接如下:

點擊直接前往

需要注意的是,為了適應UDP視頻傳輸,這里的FDMA已被我修改,和以往版本不同,具體參考代碼;

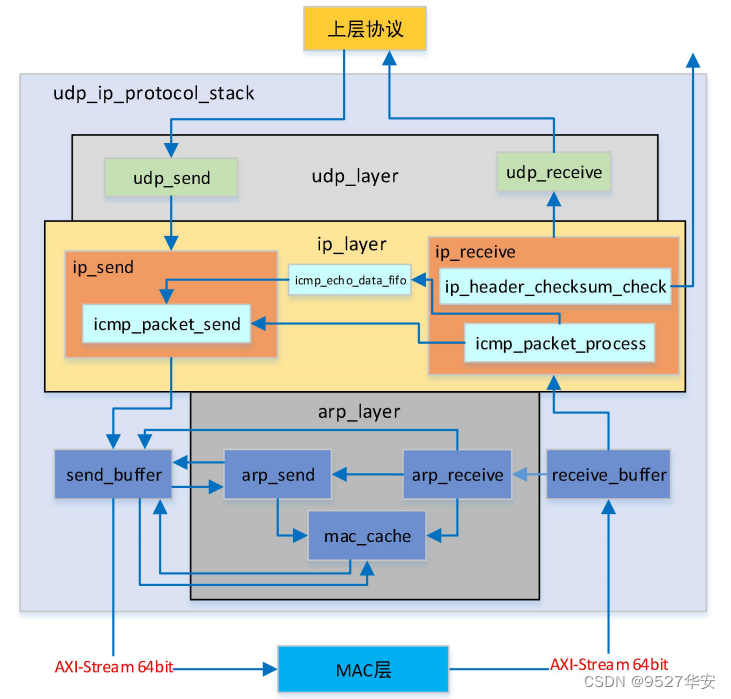

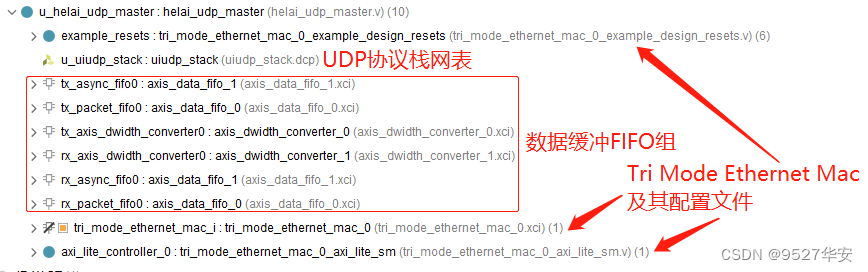

UDP協議棧

本UDP協議棧使用UDP協議棧網表文件,該協議棧目前并不開源,只提供網表文件,雖看不見源碼但可正常實現UDP通信,但不影響使用,該協議棧帶有用戶接口,使得用戶無需關心復雜的UDP協議而只需關心簡單的用戶接口時序即可操作UDP收發,非常簡單;協議棧架構如下:

協議棧性能表現如下:

1:支持 UDP 接收校驗和檢驗功能,暫不支持 UDP 發送校驗和生成;

2:支持 IP 首部校驗和的生成和校驗,同時支持 ICMP 協議中的 PING 功能,可接收并響應同一個子網內部設備的 PING 請求;

3:可自動發起或響應同一個子網內設備的 ARP 請求,ARP 收發完全自適應。ARP 表可保存同一個子網內部256 個 IP 和 MAC 地址對;

4:支持 ARP 超時機制,可檢測所需發送數據包的目的 IP 地址是否可達;

5:協議棧發送帶寬利用率可達 93%,高發送帶寬下,內部仲裁機制保證 PING 和 ARP 功能不受任何影響;

6:發送過程不會造成丟包;

7:提供64bit位寬AXI4-Stream形式的MAC接口,可與Xilinx官方的千兆以太網IP核Tri Mode Ethernet MAC,以及萬兆以太網 IP 核 10 Gigabit Ethernet Subsystem、10 Gigabit Ethernet MAC 配合使用;

有了此協議棧,我們無需關心復雜的UDP協議的實現了,直接調用接口即可使用。。。

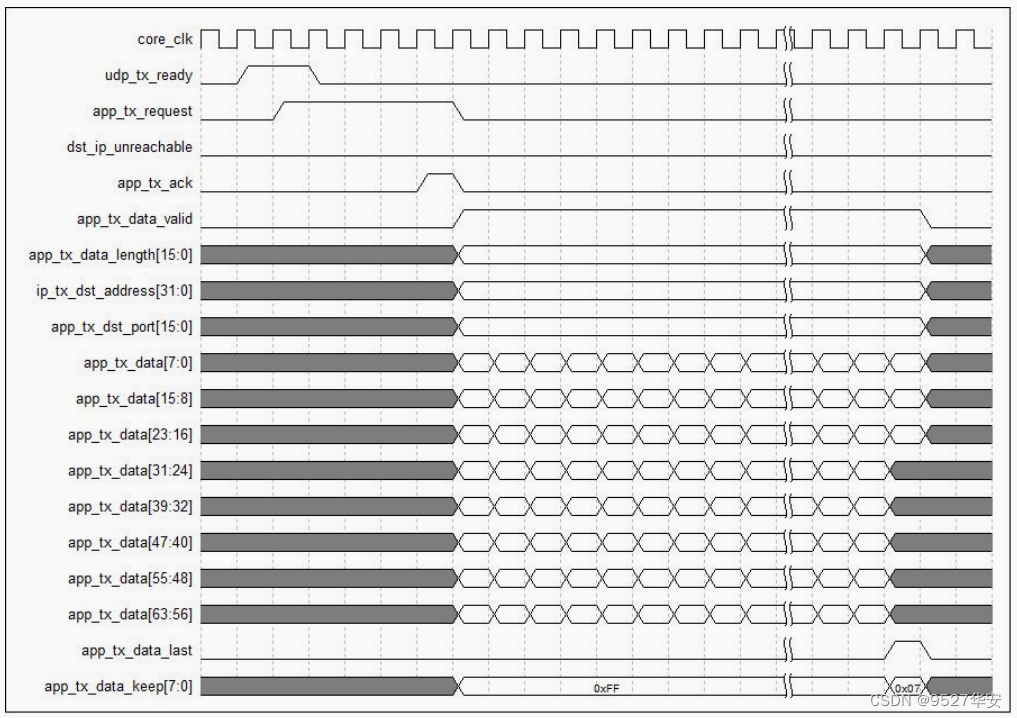

本UDP協議棧用戶接口發送時序如下:

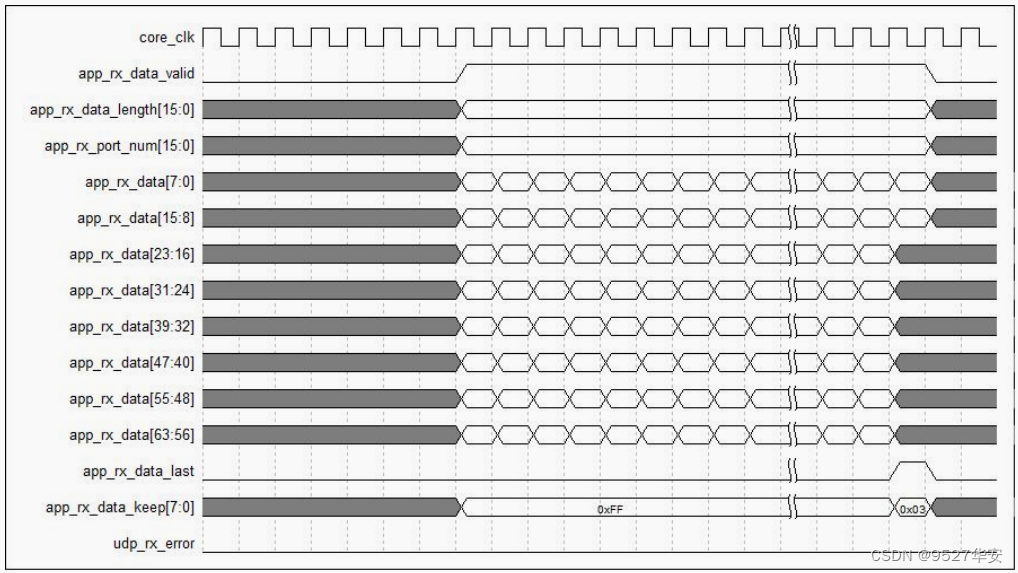

本UDP協議棧用戶接口接收時序如下:

UDP視頻發送

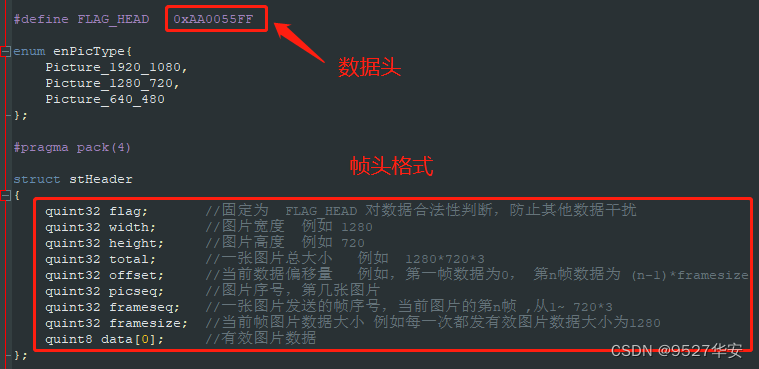

UDP視頻發送實現UDP視頻數據的組包,UDP數據發送必須與QT上位機的接受程序一致,上位機定義的UDP幀格式包括幀頭個UDP數據,幀頭定義如下:

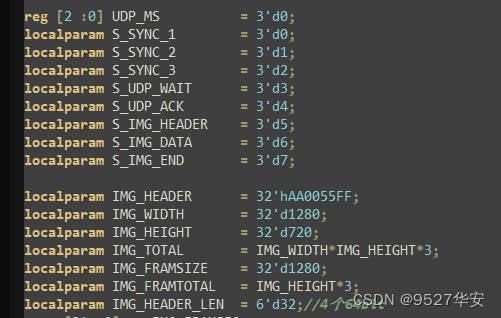

FPGA端的UDP數據組包代碼必須與上圖的數據幀格式對應,否則QT無法解析,代碼中定義了數據組包狀態機以及數據幀,如下:

另外,由于UDP發送是64位數據位寬,而圖像像素數據是24bit位寬,所以必須將UDP數據重新組合,以保證像素數據的對齊,這部分是整個工程的難點,也是所有FPGA做UDP數據傳輸的難點;

UDP協議棧數據發送

UDP協議棧具有發送和接收功能,但這里僅用到了發送,此部分代碼架構如下:

UDP協議棧代碼組我已經做好,用戶可直接拿去使用;

MAC數據緩沖FIFO組

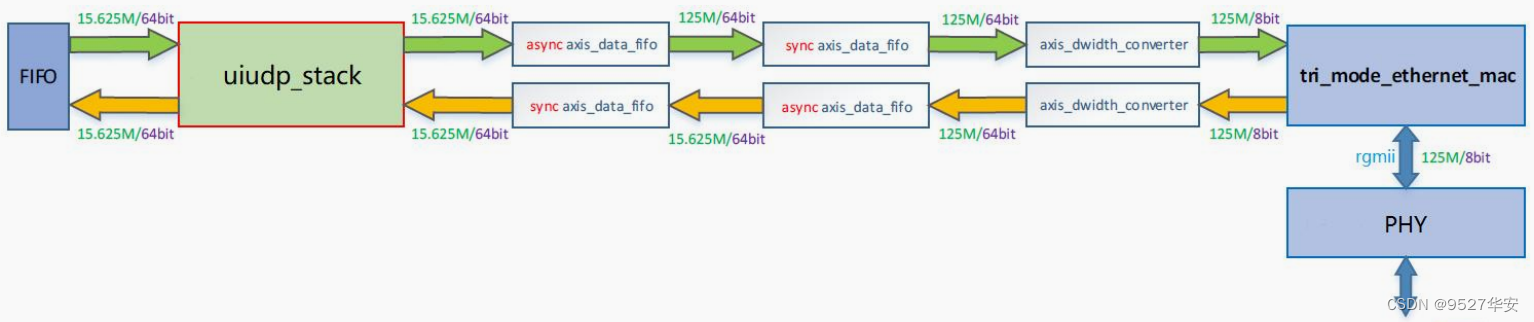

這里對代碼中用到的數據緩沖FIFO組做如下解釋:

由于 UDP IP 協議棧的 AXI-Stream 數據接口位寬為 64bit,而 Tri Mode Ethernet MAC 的 AXI-Stream數據接口位寬為 8bit。因此,要將 UDP IP 協議棧與 Tri Mode Ethernet MAC 之間通過 AXI-Stream 接口互聯,需要進行時鐘域和數據位寬的轉換。實現方案如下圖所示:

收發路徑(本設計只用到了發送)都使用了2個AXI-Stream DATA FIFO,通過其中1個FIFO實現異步時鐘域的轉換,1個FIFO實

現數據緩沖和同步Packet mode功能;由于千兆速率下Tri Mode Ethernet MAC的AXI-Stream數據接口同步時鐘信號為125MHz,此時,UDP協議棧64bit的AXI-Stream數據接口同步時鐘信號應該為125MHz/(64/8)=15.625MHz,因此,異步

AXI-Stream DATA FIFO兩端的時鐘分別為125MHz(8bit),15.625MHz(64bit);UDP IP協議棧的AXI-Stream接口經過FIFO時鐘域轉換后,還需要進行數據數據位寬轉換,數據位寬的轉換通過AXI4-Stream Data Width Converter完成,在接收路徑中,進行 8bit 到 64bit 的轉換;在發送路徑中,進行 64bit 到 8bit 的轉換;

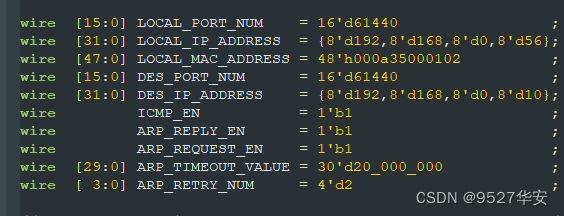

IP地址、端口號的修改

UDP協議棧留出了IP地址、端口號的修改端口供用戶自由修改,位置如下:

PHY芯片–>以太網網口輸出方案

PHY芯片網絡輸出架構以Tri Mode Ethernet MAC為核心,以PHY芯片為載體,優點是FPGA邏輯設計較為簡單,缺點是硬件設計較為復雜,硬件成本會相應提高;本設計采用RTL8211E芯片,工作于延時模式,RGMII接口;關于該方案的以太網輸出詳細設計文檔,請參考我之前的博客,博客鏈接如下:

直接點擊前往

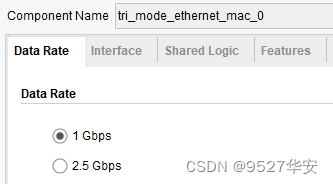

Tri Mode Ethernet MAC

Tri Mode Ethernet MAC主要是為了適配PHY芯片,因為后者的輸入接口是GMII,而Tri Mode Ethernet MAC的輸入接口是AXIS,輸出接口是GMII,Tri Mode Ethernet MAC配置如下:

提供Tri Mode Ethernet MAC使用教程和移植教程,如下:

1G/2.5G Ethernet PCS/PMA or SGMII–>以太網光口輸出方案

1G/2.5G Ethernet PCS/PMA or SGMII+Tri Mode Ethernet MAC網絡輸出架構不需要外接PHY芯片,網絡數據直接通過SFP光口輸出,優點是硬件設計較為簡單,硬件成本會相應較低,缺點是FPGA邏輯設計較為復雜;關于該方案的以太網輸出詳細設計文檔,請參考我之前的博客,博客鏈接如下:

直接點擊前往

該方案需要一個SFP轉網口(電口)接網線輸出到PC端,可以到某寶購買該類電口,30多塊錢,如下:

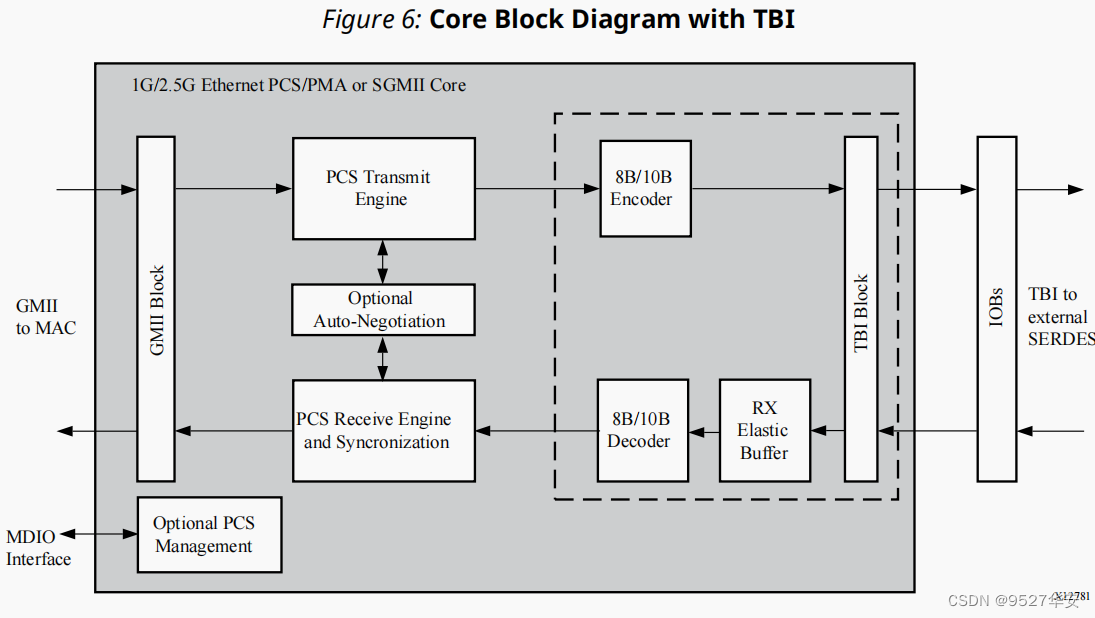

1G/2.5G Ethernet PCS/PMA or SGMII 簡介

1G/2.5G Ethernet PCS/PMA or SGMII實現了類似于網絡PHY芯片的功能,其功能框圖如下:

接收端:

數據首先經過GT資源解串,將串行數據解為并行數據;然后經過彈性Buffer做數據緩沖處理,主要是為了去頻偏,使板與板之間的數據穩定,然后進行8b/10b解碼,恢復正常數據;然后經過PCS接收同步器,對數據進行跨時鐘處理,同步到GMII時序下;最后將數據放入GMII總線下輸出;

發送端:

發送端則簡單得多,輸入時序為GMII;然后進入PCS發送引擎;然后對數據進行8b/10b編碼;最后放入GT串化后輸出;

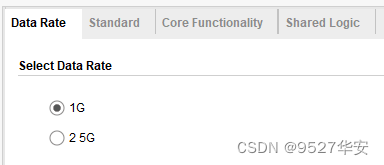

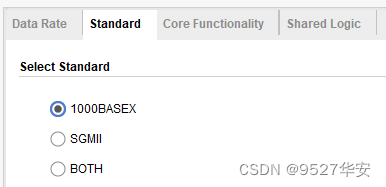

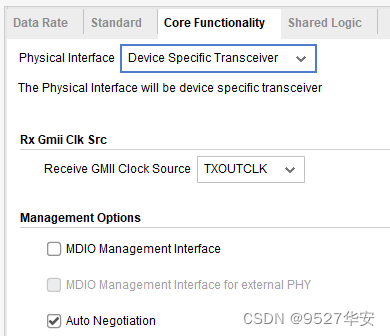

1G/2.5G Ethernet PCS/PMA or SGMII 配置

1G/2.5G Ethernet PCS/PMA or SGMII配置為1G,其與MAC的接口為GMII,配置如下:

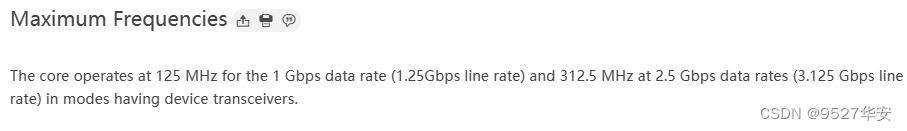

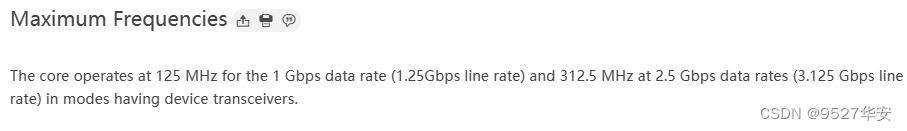

1G/2.5G Ethernet PCS/PMA or SGMII可運行于1G和2.5G線速率,對GT時鐘有嚴格研究,按照官方數據手冊,運行1G線速率時,GT差分時鐘必須為125M,運行2.5G線速率時,GT差分時鐘必須為312.5M,如下:

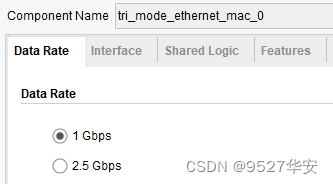

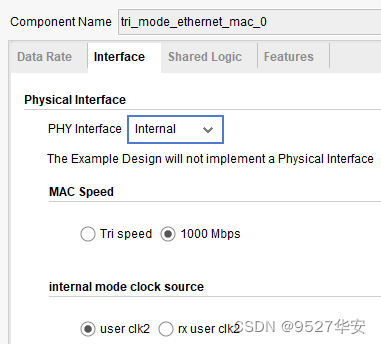

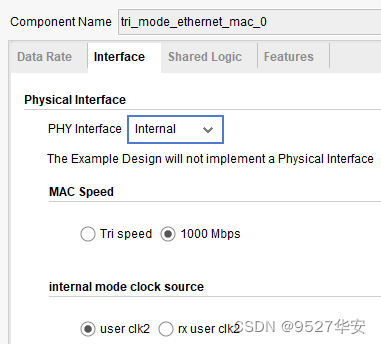

Tri Mode Ethernet MAC

Tri Mode Ethernet MAC主要是為了適配1G/2.5G Ethernet PCS/PMA or SGMII,因為后者的輸入接口是GMII,而Tri Mode Ethernet MAC的輸入接口是AXIS,輸出接口是GMII,Tri Mode Ethernet MAC配置如下:

AXI 1G/2.5G Ethernet Subsystem–>以太網光口輸出方案

AXI 1G/2.5G Ethernet Subsystem網絡輸出架構不需要外接PHY芯片,網絡數據直接通過SFP光口輸出,優點是硬件設計較為簡單,硬件成本會相應較低,缺點是FPGA邏輯設計較為復雜;關于該方案的以太網輸出詳細設計文檔,請參考我之前的博客,博客鏈接如下:

直接點擊前往

該方案需要一個SFP轉網口(電口)接網線輸出到PC端,可以到某寶購買該類電口,30多塊錢,如下:

AXI 1G/2.5G Ethernet Subsystem 簡介

AXI 1G/2.5G Ethernet Subsystem的權威官方手冊為《pg138-axi-ethernet》,請自行下載閱讀,該IP是Xilinx官方將1G/2.5G Ethernet PCS/PMA or SGMII和Tri Mode Ethernet MAC封裝在一起組成的全新IP,目的是簡化FPGA實現以太網物理層的設計難度,直接調用這一個IP即可使用,該IP展開后如下:

接收端:

數據首先經過1G/2.5G Ethernet PCS/PMA or SGMII解串,將串行數據解為并行數據;然后經過彈性Buffer做數據緩沖處理,主要是為了去頻偏,使板與板之間的數據穩定,然后進行8b/10b解碼,恢復正常數據;然后經過PCS接收同步器,對數據進行跨時鐘處理,同步到GMII時序下然后輸出給Tri Mode Ethernet MAC進行數據合適轉換,最后以AXI4-Stream輸出;

發送端:

發送端則簡單得多,用戶側UDP MAC數據首先給到Tri Mode Ethernet MAC進行數據合適轉換,以GMII數據輸出給1G/2.5G Ethernet PCS/PMA or SGMII,后者進行以太網物理層處理,以差分信號輸出;

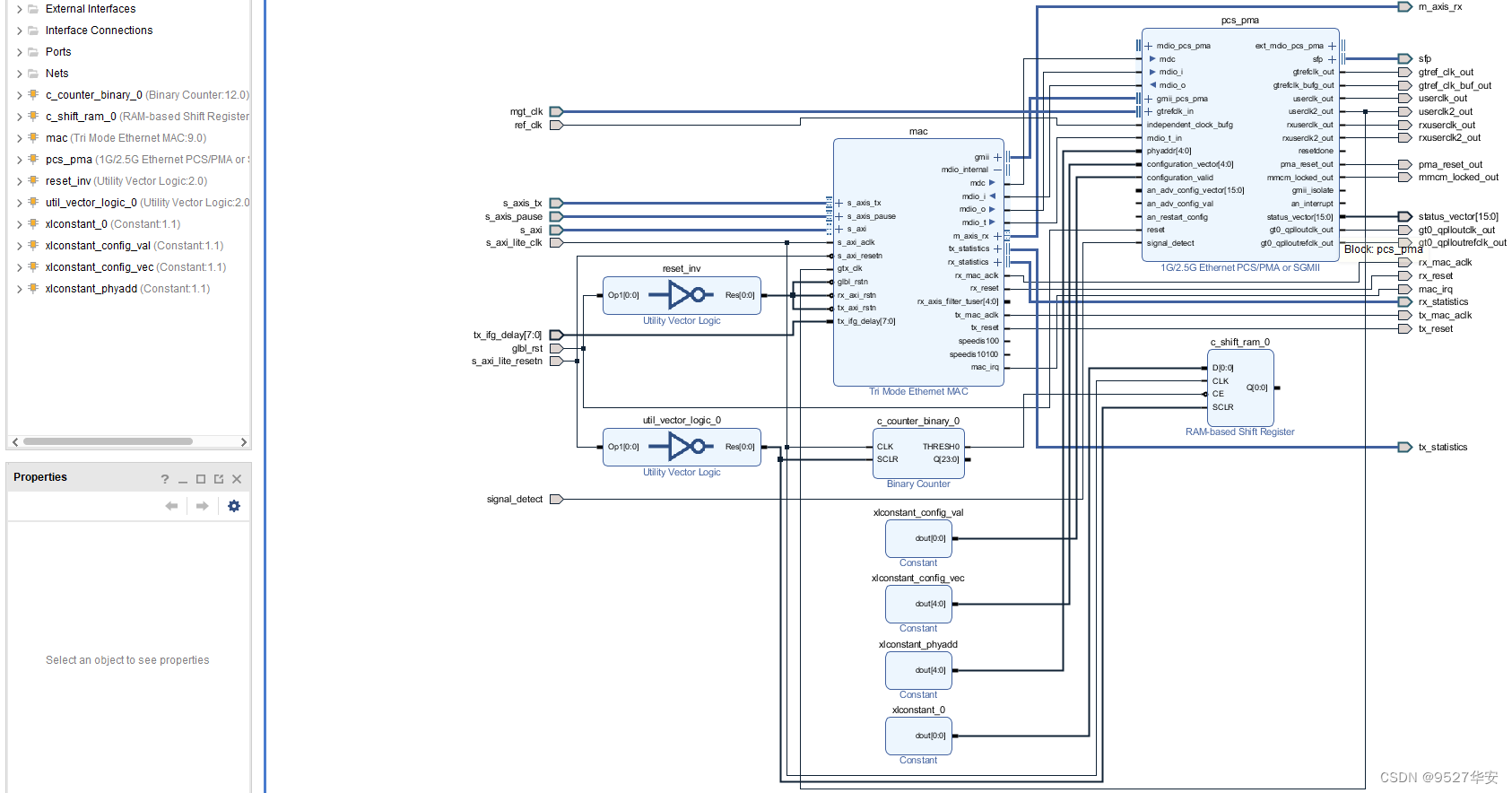

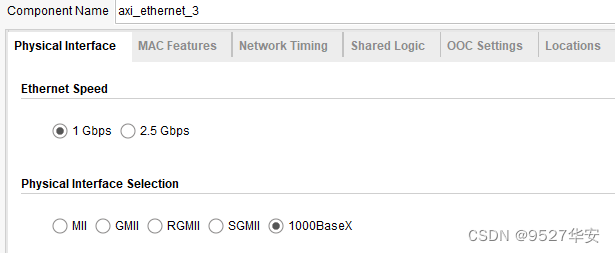

AXI 1G/2.5G Ethernet Subsystem 配置

AXI 1G/2.5G Ethernet Subsystem配置為1G,如下:

AXI 1G/2.5G Ethernet Subsystem可運行于1G和2.5G線速率,對GT時鐘有嚴格研究,按照官方數據手冊,運行1G線速率時,GT差分時鐘必須為125M,運行2.5G線速率時,GT差分時鐘必須為312.5M,如下:

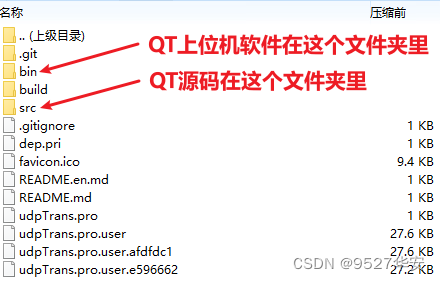

QT上位機和源碼

PC端接收網絡視頻,并運行QT上位機接收顯示視頻;我們提供和UDP通信協議相匹配的QT抓圖顯示上位機及其源代碼,目錄如下:

我們的QT目前僅支持1280x720分辨率的視頻抓圖顯示,但同時預留了1080P接口,對QT開發感興趣的朋友可以嘗試修改代碼以適應1080P,因為QT在這里只是驗證工具,不是本工程的重點,所以不再過多贅述;

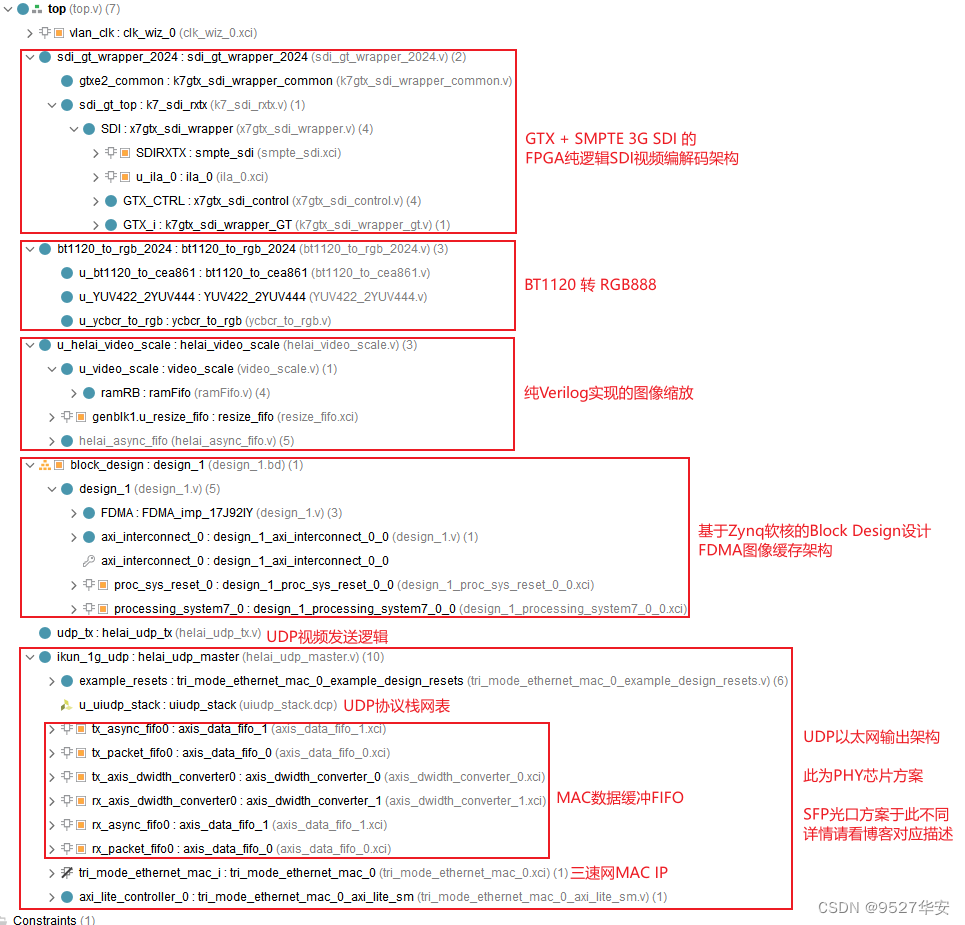

工程源碼架構

本博客提供3套工程源碼,以工程源碼1為例,vivado Block Design設計如下,其他工程與之類似,Block Design設計為圖像緩存架構的部分:

以工程源碼1為例,使工程源碼架構如下,其他工程與之類似:

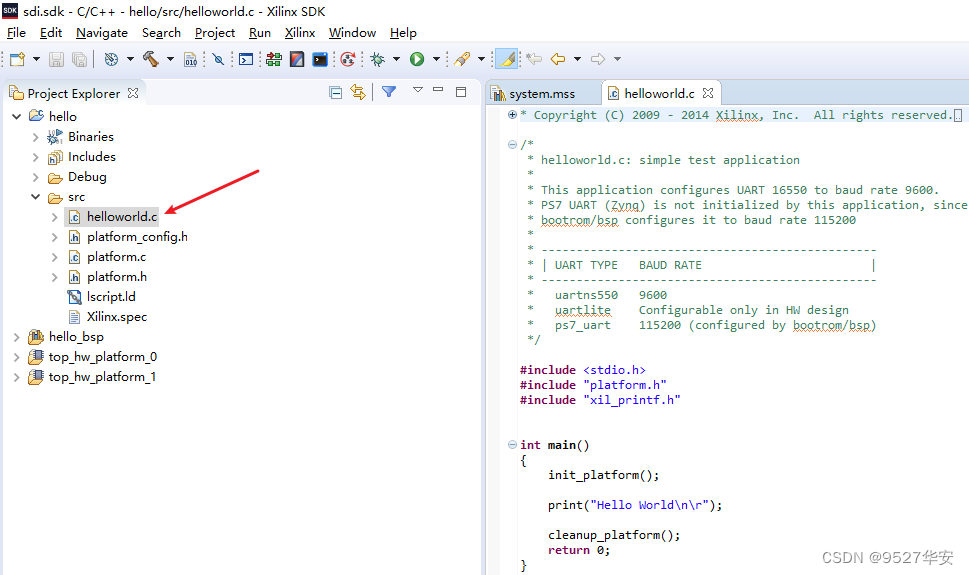

FDMA圖像緩存架構雖然不需要SDK配置,但FDMA的AXI4接口時鐘由Zynq提供,所以需要運行SDK程序才能啟動Zynq,從而為PL端邏輯提供時鐘;由于不需要SDK配置,所以SDK軟件代碼就變得極度簡單,只需運行一個“Hello World”即可,如下:

4、工程源碼1詳解–>PHY芯片以太網輸出方案

開發板FPGA型號:Xilinx-Zynq7100–xc7z100ffg900-2;

開發環境:Vivado2019.1;

輸入:3G-SDI相機或HDMI轉SDI盒子,分辨率1920x1080@60Hz;

輸出:RJ45網口,分辨率1280x720@60Hz;

圖像縮放方案:自研純Verilog圖像縮放;

圖像縮放實例:1920x1080縮放到1280x720;

圖像緩存方案:自研FDMA方案;

圖像緩存介質:PS端DDR3;

以太網輸出方案:PHY芯片以太網輸出;

PHY芯片:RTL8211E,延時模式,RGMII接口;

PC端接收方案:QT上位機;

工程作用:此工程目的是讓讀者掌握Zynq系列FPGA實現SDI轉網口的設計能力,以便能夠移植和設計自己的項目;

工程Block Design和工程代碼架構請參考第3章節的《工程源碼架構》小節內容;

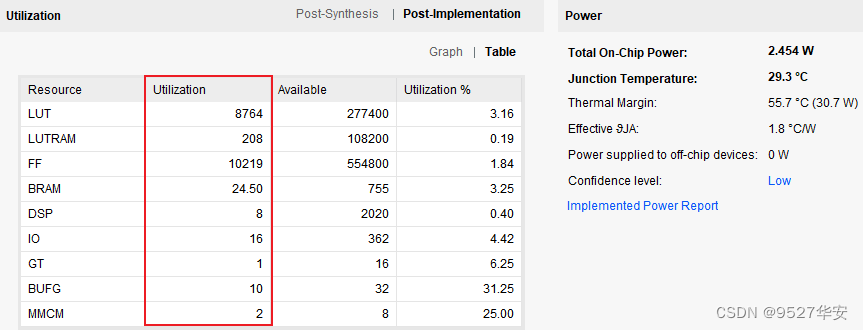

工程的資源消耗和功耗如下:

5、工程源碼2詳解–>1G/2.5G Ethernet PCS/PMA or SGMII以太網輸出方案

開發板FPGA型號:Xilinx-Zynq7100–xc7z100ffg900-2;

開發環境:Vivado2019.1;

輸入:3G-SDI相機或HDMI轉SDI盒子,分辨率1920x1080@60Hz;

輸出:SFP光口,分辨率1280x720@60Hz;

圖像縮放方案:自研純Verilog圖像縮放;

圖像縮放實例:1920x1080縮放到1280x720;

圖像緩存方案:自研FDMA方案;

圖像緩存介質:PS端DDR3;

以太網輸出方案:1G/2.5G Ethernet PCS/PMA or SGMII+Tri Mode Ethernet MAC以太網輸出;

PC端接收方案:QT上位機;

工程作用:此工程目的是讓讀者掌握Zynq系列FPGA實現SDI轉網口的設計能力,以便能夠移植和設計自己的項目;

工程Block Design和工程代碼架構請參考第3章節的《工程源碼架構》小節內容;

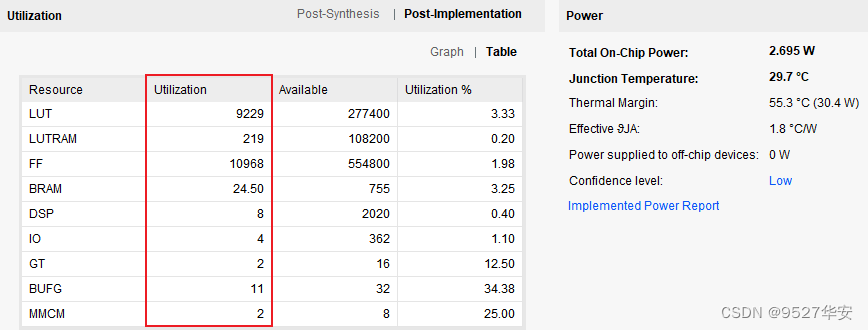

工程的資源消耗和功耗如下:

6、工程源碼3詳解–>AXI 1G/2.5G Ethernet Subsystem以太網輸出方案

開發板FPGA型號:Xilinx-Zynq7100–xc7z100ffg900-2;

開發環境:Vivado2019.1;

輸入:3G-SDI相機或HDMI轉SDI盒子,分辨率1920x1080@60Hz;

輸出:SFP光口,分辨率1280x720@60Hz;

圖像縮放方案:自研純Verilog圖像縮放;

圖像縮放實例:1920x1080縮放到1280x720;

圖像緩存方案:自研FDMA方案;

圖像緩存介質:PS端DDR3;

以太網輸出方案:AXI 1G/2.5G Ethernet Subsystem以太網輸出;

PC端接收方案:QT上位機;

工程作用:此工程目的是讓讀者掌握Zynq系列FPGA實現SDI轉網口的設計能力,以便能夠移植和設計自己的項目;

工程Block Design和工程代碼架構請參考第3章節的《工程源碼架構》小節內容;

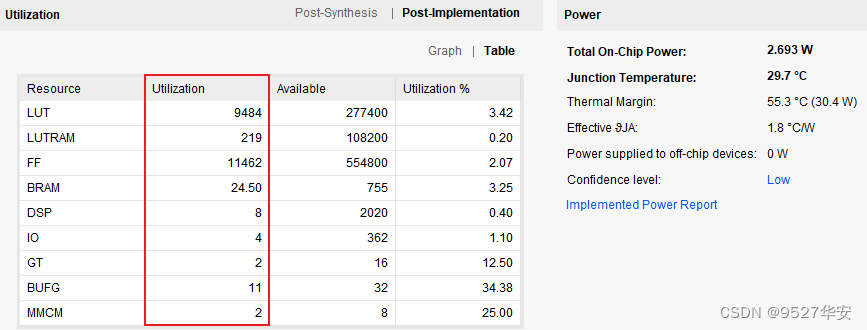

工程的資源消耗和功耗如下:

7、工程移植說明

vivado版本不一致處理

1:如果你的vivado版本與本工程vivado版本一致,則直接打開工程;

2:如果你的vivado版本低于本工程vivado版本,則需要打開工程后,點擊文件–>另存為;但此方法并不保險,最保險的方法是將你的vivado版本升級到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解決如下:

打開工程后會發現IP都被鎖住了,如下:

此時需要升級IP,操作如下:

FPGA型號不一致處理

如果你的FPGA型號與我的不一致,則需要更改FPGA型號,操作如下:

更改FPGA型號后還需要升級IP,升級IP的方法前面已經講述了;

其他注意事項

1:由于每個板子的DDR不一定完全一樣,所以MIG IP需要根據你自己的原理圖進行配置,甚至可以直接刪掉我這里原工程的MIG并重新添加IP,重新配置;

2:根據你自己的原理圖修改引腳約束,在xdc文件中修改即可;

3:純FPGA移植到Zynq需要在工程中添加zynq軟核;

8、上板調試驗證

準備工作

需要準備的器材如下:

FPGA開發板;

SDI攝像頭或HDMI轉SDI盒子;

SFP轉網口模塊(電口);

網線;

我的開發板了連接如下:

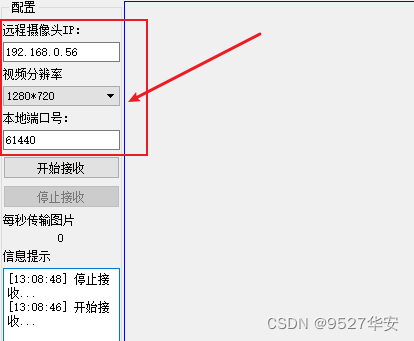

QT上位機配置如下:

輸出視頻演示

以工程1,3G-SDI輸入圖像縮放轉網絡輸出為例,輸出如下:

3G-SDI輸入圖像縮放轉網絡輸出

9、福利:工程代碼的獲取

福利:工程代碼的獲取

代碼太大,無法郵箱發送,以某度網盤鏈接方式發送,

資料獲取方式:私,或者文章末尾的V名片。

網盤資料如下:

此外,有很多朋友給本博主提了很多意見和建議,希望能豐富服務內容和選項,因為不同朋友的需求不一樣,所以本博主還提供以下服務:

異常)

. This can occur if either\n)

093)