題目匯總版--鏈接:?

【硬件-筆試面試題】硬件/電子工程師,筆試面試題匯總版,持續更新學習,加油!!!-CSDN博客

【硬件-筆試面試題-81】硬件/電子工程師,筆試面試題(知識點:詳細講講同步時鐘與異步時鐘通信)

1、題目

詳細講講同步時鐘與異步時鐘通信

2、解答

在數字系統中,時鐘是協調電路工作的 “時間基準”。根據通信雙方是否使用同一時鐘源,可分為同步時鐘通信和異步時鐘通信,二者在時序控制、數據傳輸方式和適用場景上有顯著差異。

一、同步時鐘通信(Synchronous Communication)

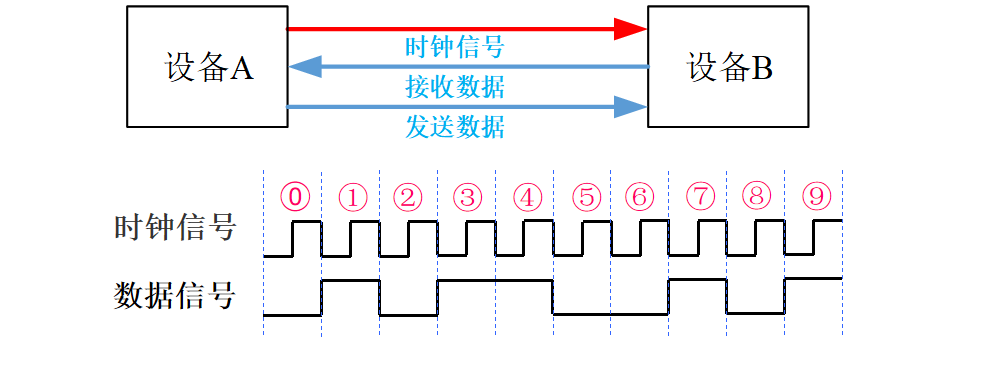

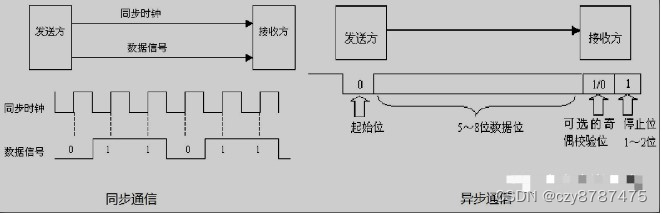

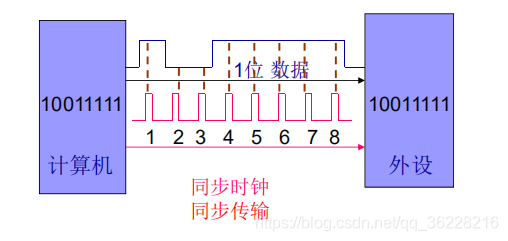

同步時鐘通信中,發送方和接收方使用同一個時鐘信號(或嚴格同步的時鐘信號),數據傳輸的節奏由該時鐘統一控制。

1. 核心特點

- 共享時鐘源:發送方和接收方的時鐘信號由同一振蕩器產生,或通過時鐘同步機制(如 PLL 鎖相環)保持嚴格相位對齊(相位差固定,頻率相同)。

- 數據連續傳輸:數據以固定速率連續發送,無需額外的 “起始 / 停止” 信號標記幀邊界,時鐘信號直接定義每一位數據的采樣時刻。

- 時序嚴格對齊:發送方在時鐘的上升沿 / 下降沿發送數據,接收方在相同(或固定延遲)的時鐘沿采樣數據,確保數據被正確讀取。

2. 典型工作流程

- 發送方和接收方通過硬件線路共享時鐘(如單獨的 CLK 線),或接收方從發送方的信號中提取時鐘(如曼徹斯特編碼的自同步)。

- 數據在時鐘的驅動下按固定周期傳輸,例如:時鐘頻率為 100MHz 時,每 10ns 傳輸 1 位數據。

- 接收方根據時鐘邊沿判斷數據位的起始和結束,直接采樣數據線上的電平(高 / 低代表 1/0)。

3. 優勢

- 傳輸效率高:無需額外的同步開銷(如起始位、停止位),數據幀可連續傳輸,帶寬利用率高。

- 速度快:適合高頻、高速場景(如 GHz 級),因為時鐘同步確保了精確的采樣時機。

- 電路實現簡單:接收方無需復雜的時鐘恢復邏輯,只需按固定時鐘采樣即可。

4. 劣勢

- 時鐘同步要求高:時鐘信號的延遲、抖動(Jitter)或噪聲可能導致采樣錯誤(如建立時間 / 保持時間違規)。長距離傳輸時,時鐘信號衰減或相位偏移更明顯,同步難度大。

- 布線約束嚴格:在 PCB 設計中,時鐘線和數據線需嚴格等長(減少延遲差),增加布線復雜度。

- 靈活性低:通信雙方必須嚴格同步,若一方時鐘異常,整個通信鏈路會失效。

5. 典型應用

- 高速總線:如 SPI(Serial Peripheral Interface,有單獨 CLK 線)、I2C(雖無專用 CLK 線,但 SCL 時鐘由主設備提供,從設備嚴格跟隨)、DDR 內存(雙數據率同步時鐘)。

- 芯片內部互連:CPU 與緩存、FPGA 內部邏輯塊之間的通信(片內時鐘同步性好)。

二、異步時鐘通信(Asynchronous Communication)

異步時鐘通信中,發送方和接收方使用各自獨立的時鐘源,時鐘頻率可不同(或允許一定偏差),數據傳輸的同步不依賴共享時鐘,而是通過信號本身的特征(如起始位、停止位)實現。

1. 核心特點

- 獨立時鐘源:發送方和接收方的時鐘由各自的振蕩器產生,頻率可存在誤差(通常允許 ±5%~±10% 偏差),無需同步。

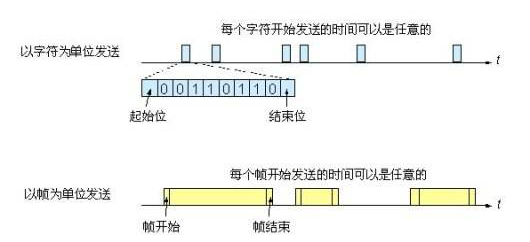

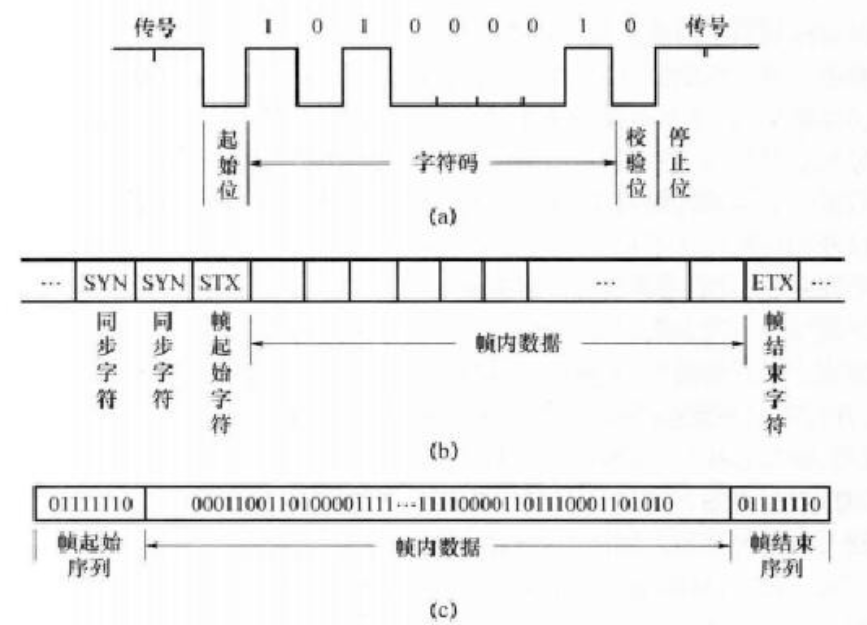

- 幀格式帶同步信息:每幀數據包含起始位(標記數據開始)、數據位(有效信息)、校驗位(可選,用于錯誤檢測)和停止位(標記數據結束),通過這些信號實現接收方的同步。

- 采樣依賴信號邊沿:接收方通過檢測起始位的邊沿(如從高電平到低電平的跳變)觸發內部時鐘,開始對后續數據位采樣。

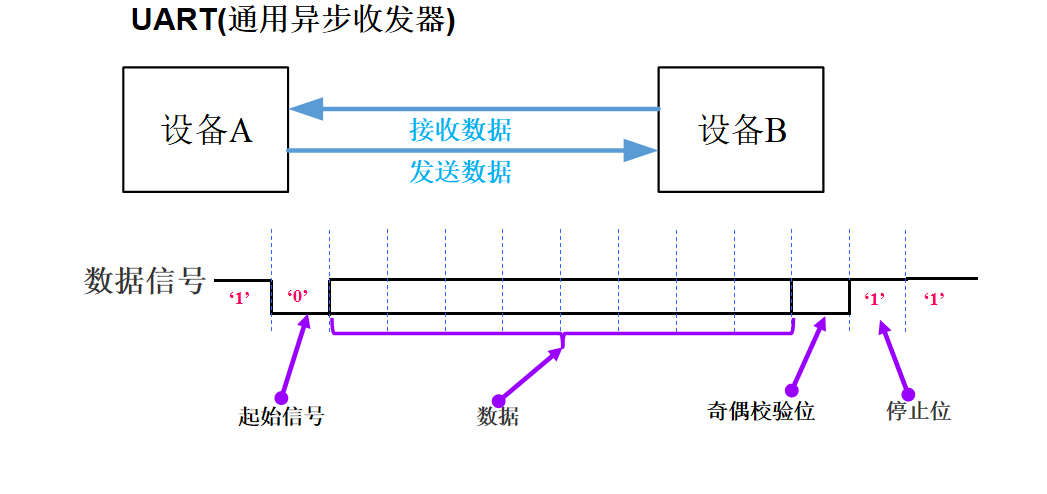

2. 典型工作流程(以 UART 為例)

- 發送方要傳輸數據時,先發送 1 個 “起始位”(低電平),通知接收方 “數據即將到來”。

- 接收方檢測到起始位后,啟動內部時鐘(頻率通常是數據率的 16 倍),在每一位數據的 “中間時刻”(避免邊沿抖動影響)采樣電平,判斷是 0 還是 1。

- 數據位傳輸完成后,發送方發送 1~2 個 “停止位”(高電平),表示一幀數據結束。接收方檢測到停止位后,確認幀傳輸完成,可準備接收下一幀。

3. 優勢

- 無需共享時鐘:發送方和接收方時鐘獨立,降低硬件連接復雜度(如 UART 只需 TX/RX 兩根線)。

- 抗干擾性強:長距離傳輸時,即使時鐘有偏差,通過起始位和中間采樣可修正誤差(只要偏差在允許范圍內)。

- 靈活性高:適用于不同設備間的通信(如電腦與傳感器),無需嚴格同步時鐘源。

4. 劣勢

- 傳輸效率低:每幀數據包含起始位、停止位等額外開銷(如 UART 每 8 位數據需 1 位起始位 + 1 位停止位,開銷占 20%),不適合高速、大數據量傳輸。

- 對時鐘精度有要求:接收方時鐘頻率需與數據率匹配(允許小偏差),否則采樣時刻會偏移,導致數據錯誤(偏差過大會錯過正確采樣點)。

- 電路設計復雜:接收方需要邊沿檢測、位同步(找到每一位的中間時刻)等邏輯,尤其在高速場景下實現難度更高。

5. 典型應用

- 低速串行通信:如 UART(通用異步收發傳輸器)、RS-232/RS-485(工業控制中常用,抗干擾,適合長距離)。

- 簡單設備交互:如單片機與傳感器、藍牙模塊的通信(對速度要求不高,注重連接簡便)。

三、關鍵區別對比

| 維度 | 同步時鐘通信 | 異步時鐘通信 |

|---|---|---|

| 時鐘源 | 共享同一時鐘(或嚴格同步) | 各自獨立時鐘(允許頻率偏差) |

| 同步方式 | 依賴時鐘信號邊沿同步 | 依賴起始位 / 停止位等幀內信號同步 |

| 傳輸效率 | 高(無額外開銷) | 低(含起始 / 停止位等開銷) |

| 速度 | 適合高速(如 GHz 級) | 適合低速(如 kbps~Mbps 級) |

| 抗干擾與距離 | 短距離抗干擾好,長距離時鐘易偏移 | 長距離抗干擾較好(依賴信號本身同步) |

| 硬件復雜度 | 時鐘布線嚴格,接收邏輯簡單 | 無需時鐘線,接收邏輯復雜(需位同步) |

| 典型應用 | SPI、I2C、DDR 內存、片內互連 | UART、RS-232/RS-485、簡單設備交互 |

四、混合場景:跨時鐘域通信

在復雜系統中(如 SOC 芯片),常存在多個獨立時鐘域(如 CPU 核用 1GHz 時鐘,外設用 100MHz 時鐘),此時同步時鐘和異步時鐘可能需要交互,稱為 “跨時鐘域通信”。

- 核心問題:異步信號進入同步時鐘域時,可能因 “亞穩態”(信號在時鐘沿附近跳變,導致采樣結果不確定)引發錯誤。

- 解決方法:通過 “同步器”(如兩級觸發器)、“握手協議”(如 req/ack 信號)或 “FIFO 緩沖” 等機制,確保數據在不同時鐘域間可靠傳輸。

總結

- 同步時鐘通信依賴共享時鐘,效率高、速度快,適合短距離、高速、高帶寬場景,但對時鐘同步要求嚴格;

- 異步時鐘通信無需共享時鐘,靈活性高、適合長距離和低速場景,但效率低,依賴幀內同步信號;

- 實際系統中,二者常結合使用,跨時鐘域通信需特殊設計以避免數據錯誤。

題目匯總--鏈接:

【硬件-筆試面試題】硬件/電子工程師,筆試面試題匯總版,持續更新學習,加油!!!-CSDN博客

報錯,不顯示驗證碼)

-結構理解與其它)

)