????????此文介紹了利用先楫半導體(hpm)官方hpm5e00_evk開發板使用的主控芯片的一些原理性知識,無實驗內容展示,主要匯總了先楫半導體hpm5e00主控芯片的中斷、定時器、pwm、usart等功能,主要內容來源于B站“HPM_FAE”的視頻和官方的數據手冊,如有整理不正確的地方還望指正。

????????至于為啥整理上面幾個外設,因為上面幾個外設是本人工作項目中,用到的最基本的內容,把上面外設跑通了就可以實現國產替代,當然還有一些深入的功能,待后續研究。

1、中斷

先楫半導體(HPMicro)的微控制器中斷系統,是其高性能MCU的重要組成部分,它基于RISC-V內核,并借鑒了現代中斷控制的先進理念。其核心在于高效管理多種事件源(如外部設備、內部外設、軟件事件),確保關鍵任務能得到及時響應。

1.1、中斷定義與原理

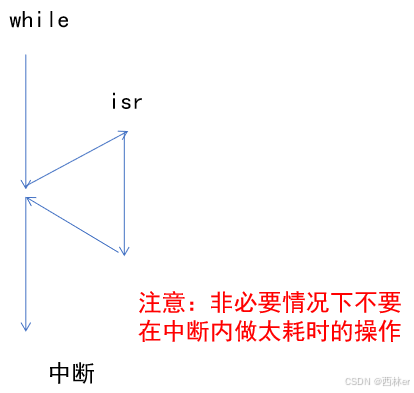

中斷是一種允許微控制器暫停當前正在執行的程序,轉去處理緊急事件,待處理完成后再返回原程序繼續執行的機制。在先楫半導體的微控制器中,中斷系統主要用于:

? 提高實時性:對外部事件(如按鍵、傳感器信號變化)或內部事件(如定時器溢出、通信數據到達)做出快速響應。

? 提升效率:避免了CPU不斷輪詢檢查事件是否發生,節省了寶貴的計算資源,使其能專注于主要任務,只有在需要時才通過中斷介入處理。

? 處理故障:為硬件故障、運算異常(如除零錯誤)等提供了處理機制。

????????中斷可以是硬件中斷(由外部硬件信號觸發,如GPIO、定時器)或軟件中斷(由特定的軟件指令觸發)。中斷系統的工作原理與流程,中斷處理通常包含以下步驟:

中斷請求:中斷源(例如外設或軟件)通過發出中斷請求信號向CPU申請服務。

中斷判優與響應:中斷控制器(如果存在類似NVIC的模塊)會根據預設的優先級對多個同時發生的中斷請求進行裁決,選擇當前最高優先級的請求向CPU響應。CPU在執行完當前指令后,若中斷未被全局屏蔽,則會響應此中斷。

保護現場:CPU在跳轉執行中斷服務程序前,會自動保存當前的程序計數器(PC)和狀態寄存器等關鍵信息,以便中斷處理后能正確恢復。

執行中斷服務程序:CPU通過查詢中斷向量表(一個存儲了各個中斷服務程序入口地址的表格)跳轉到對應的中斷服務程序(ISR) 執行。開發者需要在此函數中編寫處理特定中斷事件的代碼。

恢復現場與返回:ISR執行完畢后,通過特定的中斷返回指令,CPU會恢復之前保存的現場信息,并返回到被中斷的主程序繼續執行。

1.2、先楫MCU中斷

????????先楫MCU中斷分為本地中斷與外部中斷,常用的本地中斷包括機器定時器中斷與軟件中斷。先楫MCU支持8個中斷優先級設置,設置值0~7,優先級設置值越大中斷優先級越高,0代表關閉中斷。

針對先楫MCU中斷:

????????沒有硬件壓棧,進出中斷耗時略長一些,但是hpm主頻一般ARM類的MCU主頻高很多,進出中斷其實也還好;

????????支持中斷優先級和中斷嵌套,當多個中斷同時發生時,優先級高的中斷會優先得到響應,允許高優先級中斷打斷正在處理的低優先級中斷;

????????支持中斷嵌套與中斷向量,中斷嵌套可保證CPU始終在處理優先級最高的中斷,中斷向量則可簡化中斷處理流程,提高中斷響應速度

????????另外尤其要注意的是:本地中斷可打斷外部中斷,外部中斷無法打斷本地中斷。

1.3、中斷使用注意

????????項目之初,在設計中斷的是時候,需要特別注意一下事項:

? 避免中斷過長:長時間的中斷會阻塞系統對其他事件的響應,影響實時性。

? 謹慎處理中斷嵌套:過深或設計不當的中斷嵌套會增加系統復雜性,并可能引起優先級倒置等問題。

? 及時清除中斷標志:這是最常見的錯誤之一,忘記清除標志位會導致程序行為異常。