EDA斷供危機下的冷思考:中國芯片設計軟件的破局之道優雅草卓伊凡

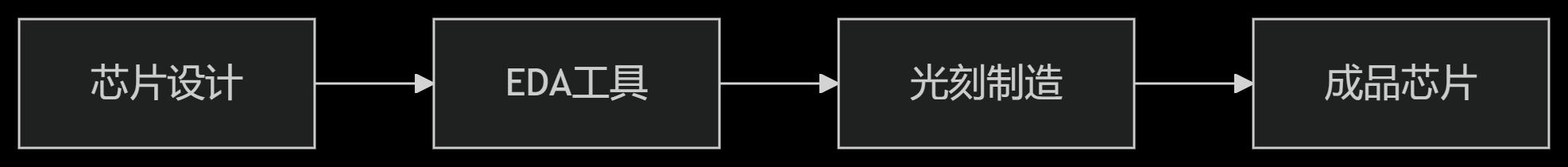

一、EDA是什么?芯片行業的”隱形基石”

1.1 EDA技術解析

EDA(Electronic Design Automation,電子設計自動化)是用于設計和驗證集成電路的軟件工具鏈,主要包括:

- 前端設計:邏輯設計、電路仿真(如Cadence Virtuoso)

- 后端實現:物理布局、布線(如Synopsys IC Compiler)

- 驗證工具:DRC(設計規則檢查)、LVS(版圖對比)

1.2 國內EDA使用現狀

| 指標 | 國際三巨頭 | 國產EDA |

| 市占率 | 90%+(Synopsys/Cadence/Mentor) | <10% |

| 工藝支持 | 3nm及以下 | 14nm主流,7nm在研 |

| 工具鏈完整度 | 全流程覆蓋 | 點工具突破 |

| 生態綁定 | 與臺積電/ASML深度協同 | 本土代工廠適配中 |

典型依賴場景:

某國產GPU設計企業若被斷供Cadence工具:

- 現有設計文件可能無法打開

- 無法生成GDSII格式的掩膜版圖

- 與臺積電的PDK(工藝設計套件)兼容性斷裂

二、三個比喻:理解EDA與芯片制造的關系

比喻1:EDA如建筑師的CAD軟件

- 沒有EDA ≈ 讓建筑師手繪摩天大樓圖紙

- 現實差距:現代芯片包含百億級晶體管,相當于規劃一座超大型城市的供水/供電/交通網絡

比喻2:EDA如芯片的”編譯器和調試器”

- 寫C++需要Visual Studio → 設計芯片需要EDA

- 但EDA還要解決:

-

- 晶體管級的”內存泄漏”(漏電流優化)

- 納米級的”多線程沖突”(信號串擾)

比喻3:EDA生態如手機操作系統

- Android/iOS 需要開發者適配 → EDA 需要代工廠提供PDK

- 臺積電的3nm PDK只完整支持Synopsys工具鏈,如同某些APP僅限iOS

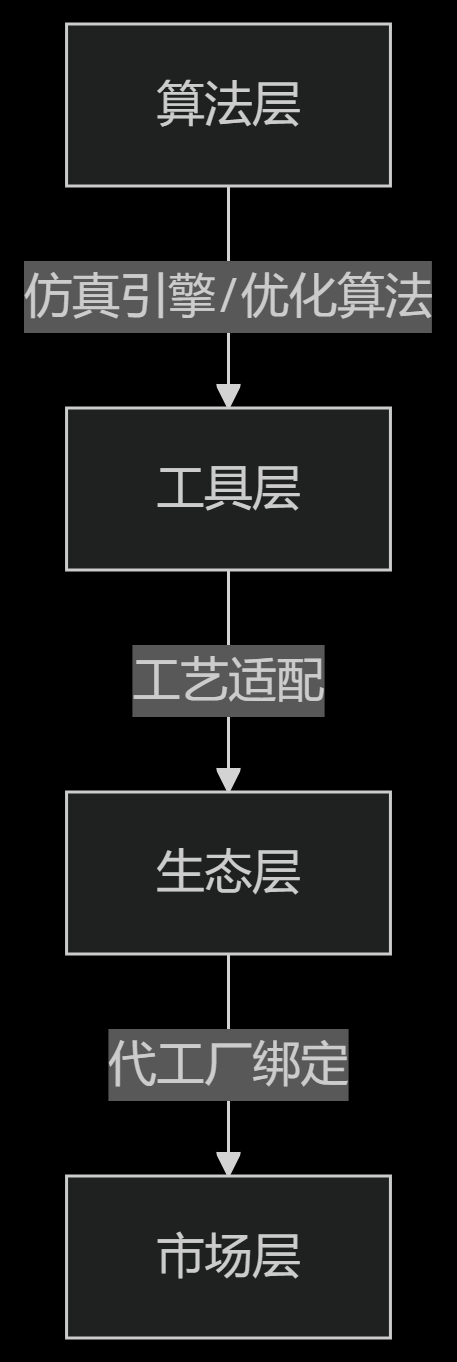

三、國產EDA的突圍難點

3.1 技術壁壘金字塔

- 算法層:

-

- 電磁場求解器需要計算數學突破

- 時序分析依賴圖論算法優化

- 生態層:

-

- 中芯國際的PDK對國產EDA支持度不足

- 設計師習慣國際工具(學習成本阻礙遷移)

3.2 數據對比:國內外研發投入

| 公司 | 年度研發費用 | EDA相關專利 |

| Synopsys | 15億美元 | 2.3萬+ |

| 華大九天 | 1.2億美元 | 800+ |

| 概倫電子 | 0.8億美元 | 300+ |

四、卓伊凡的核心觀點:營商環境>技術本身

4.1 歷史教訓:為什么過去國產EDA起不來?

- 市場端:

-

- 芯片設計公司不敢用國產工具(擔心影響流片)

- 代工廠優先服務國際EDA客戶

- 政策端:

-

- 專項經費”撒胡椒面”,缺乏持續投入

- 知識產權保護不足,企業不愿共享工藝數據

4.2 杭州模式的啟示

成功要素:

- 人才集聚:阿里系培養了大量基礎軟件人才

- 資本耐心:地方政府引導基金允許10年回報周期

- 場景開放:城市大腦等項目給國產軟件試錯機會

EDA需要:

- 中芯/長鑫等龍頭開放PDK接口

- 政府采購強制國產EDA比例

- 建立芯片-EDA協同創新中心

結語:信心比黃金更重要

回顧歷史:

- 1956年中國造不出晶體管 → 2023年長江存儲實現232層NAND

- 2003年阿里云被嘲”忽悠” → 2023年亞太市場份額第一

卓伊凡堅信:

“EDA斷供不是終點,而是國產基礎軟件的覺醒時刻。

只要守住三條底線——

- 讓工程師體面生活(杜絕”造原子彈不如賣茶葉蛋”)

- 給企業試錯空間(允許三年不盈利)

- 構建開放生態(芯片廠-EDA公司數據互通)

中國一定能長出自己的Synopsys。”

這不是技術問題,而是決心問題——當原創者的每一行代碼都能獲得尊重,當勞動者的每一滴汗水都能兌現價值,EDA的自主可控便水到渠成。

”)

)

——清晰題解)