- Ad9268芯片

? ? AD9268是一款雙通道、16位、80 MSPS/105 MSPS/125 MSPS模數轉換器(ADC)。AD9268旨在支持要求高性能、低成本、小尺寸和多功能的通信應用。雙通道ADC內核采用多級差分流水線架構,集成輸出糾錯邏輯。每個ADC都具有寬帶寬、差分采樣保持模擬輸入放大器,支持各種用戶可選的輸入范圍。集成基準電壓源簡化了設計考慮。占空比穩定器用于補償ADC時鐘占空比的變化,使轉換器保持出色的性能。ADC輸出數據可以直接路由至兩個外部16位輸出端口。這些輸出可以設置為1.8 V CMOS或LVDS。有靈活的關斷選項可以顯著省電。設置和控制編程利用三線式SPI兼容型串行接口完成。

? AD9643管腳與AD9268相同,故一般都兼容設計。AD9643的最高采樣率為250Msps,分辨率為14bit。

2.調試環境

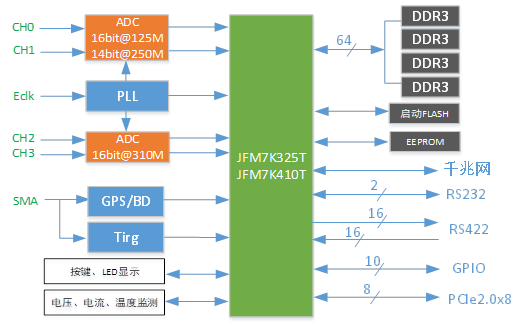

使用UD LAN-402信號處理模塊,軟件配置如下:

硬件框圖如下:

硬件框圖如下:

LAN-402的主要特點是支持4通道A/D(可以分別用于短波、超短波和雷達),對外支持16路雙向差分RS422接口(可用作波控),也有千兆網和PCIe2.0x8接口,fpga可以完成信號處理任務。

3.調試過程

AD9268對外的接口支持LVDS接口、CMOS接口兩種模式,通過SPI可以配置芯片使用哪種接口、是否開啟測試模式等等。

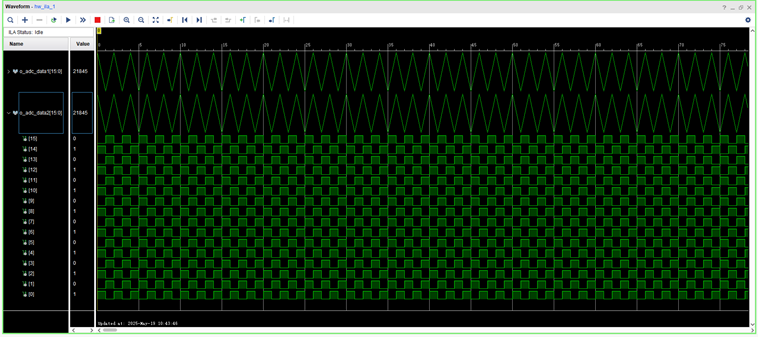

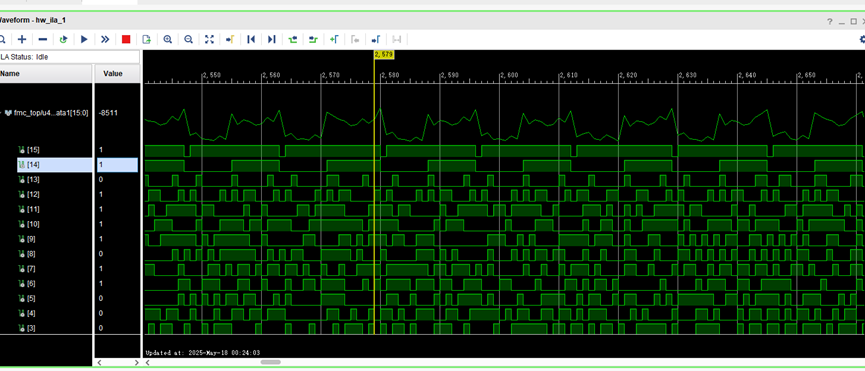

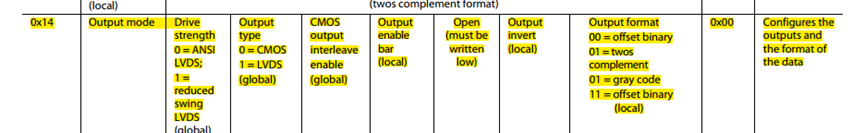

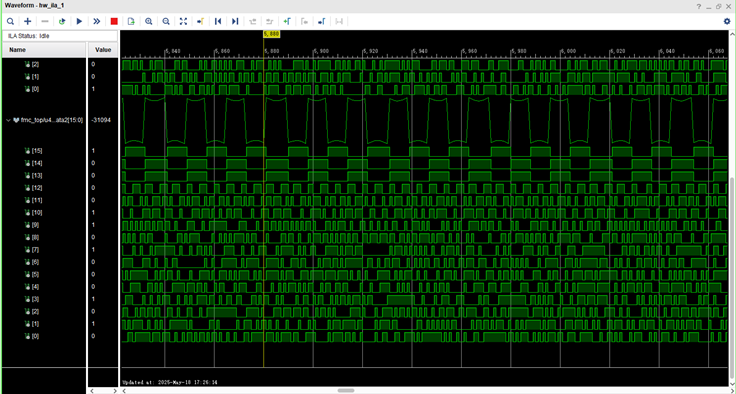

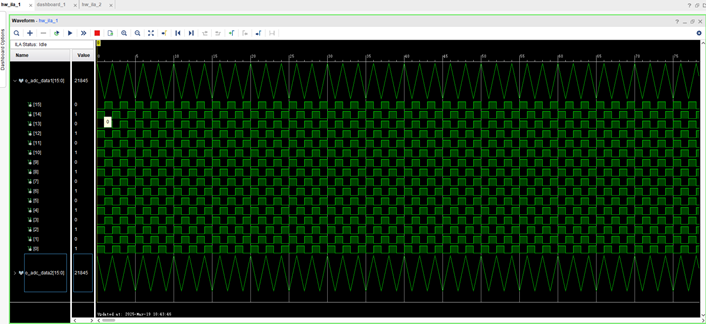

調試中時,可以先通過SPI對ADC芯片進行配置為累加數測試模式(用于測試硬件連接是否正常),效果如下:

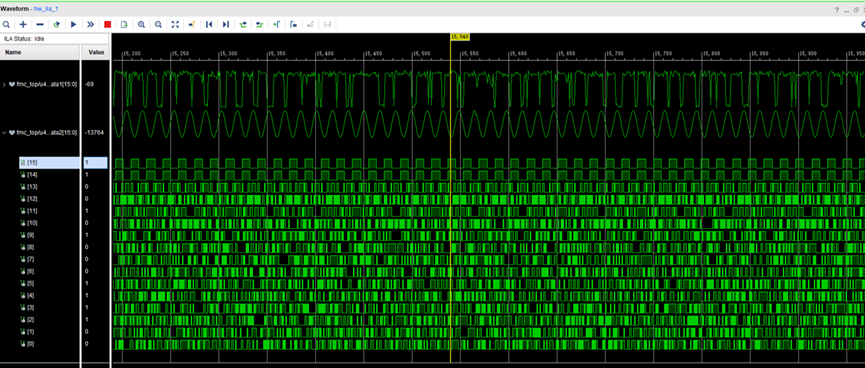

再配置為PN碼測試模式,用于校驗相位和測誤碼,效果如下:

4.調試遇到的問題

4.調試遇到的問題

-

- 調試時遇到的問題記錄

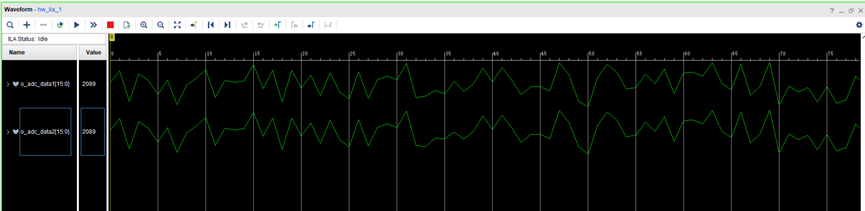

- 通道1的ADC數據無法呈現正常的正弦波脈絡,表現如下

- 調試時遇到的問題記錄

-

-

-

- 分析猜測1:可能是通道1和2數據隔離沒做好,導致ADC數據混合

-

-

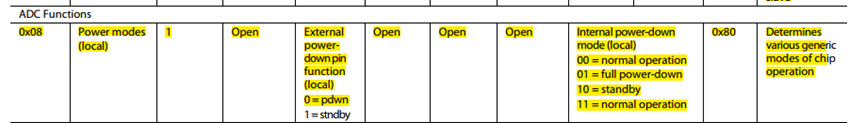

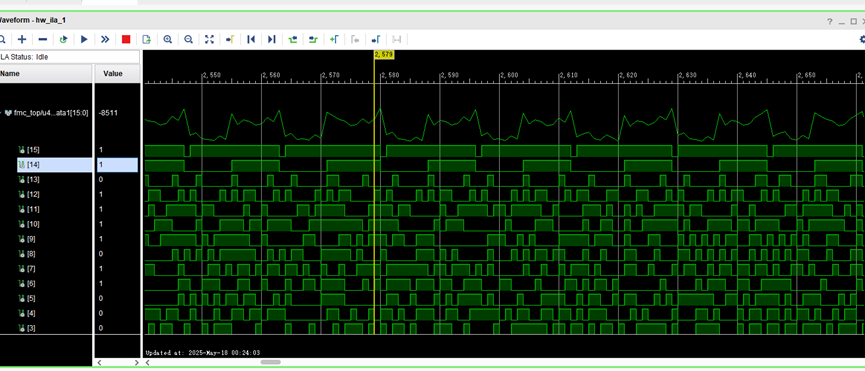

嘗試測試與實驗:配置寄存器將通道2設置未完全斷電模式:

結果仍然不正確:

-

-

-

- 分析猜測2:ADC寄存器配置錯誤,導致ADC數據輸出有

- 分析猜測2:ADC寄存器配置錯誤,導致ADC數據輸出有

-

-

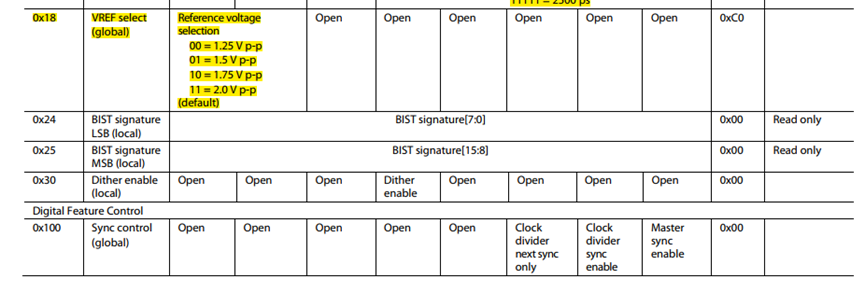

1;嘗試修改數據輸出格式:

二進制補碼:

偏移二進制

結果仍不正確

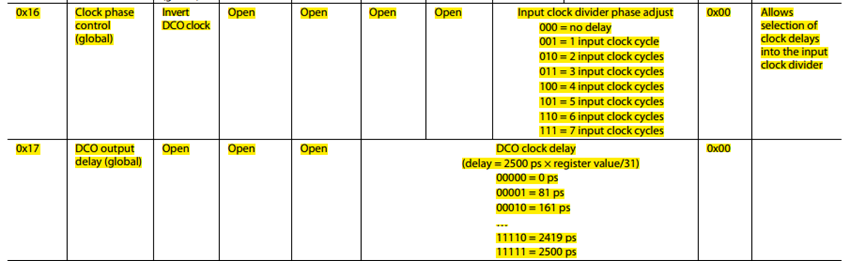

2;嘗試配置輸入輸出延時

3;打開deither_enable

4;測試寄存器配置表

配置完成后,表現變好;但仍然不正確

-

-

-

- 分析猜測3:ADC數據輸出后在FPGA內部DDR采樣時出問題

-

-

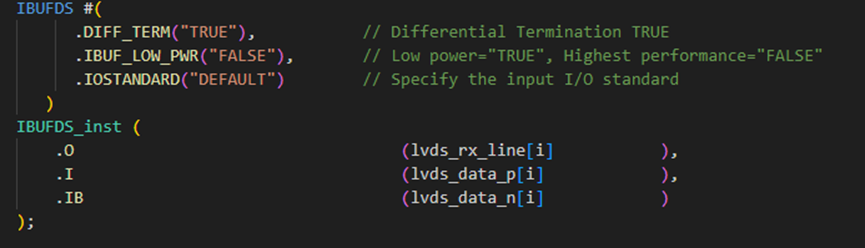

將DDR采樣時 差分終結設置為TRUE,設置為高性能表現模式。

-

-

-

- 分析猜測4:ADC數據輸出后在FPGA內部DDR采樣時時鐘未對齊(延遲)

-

-

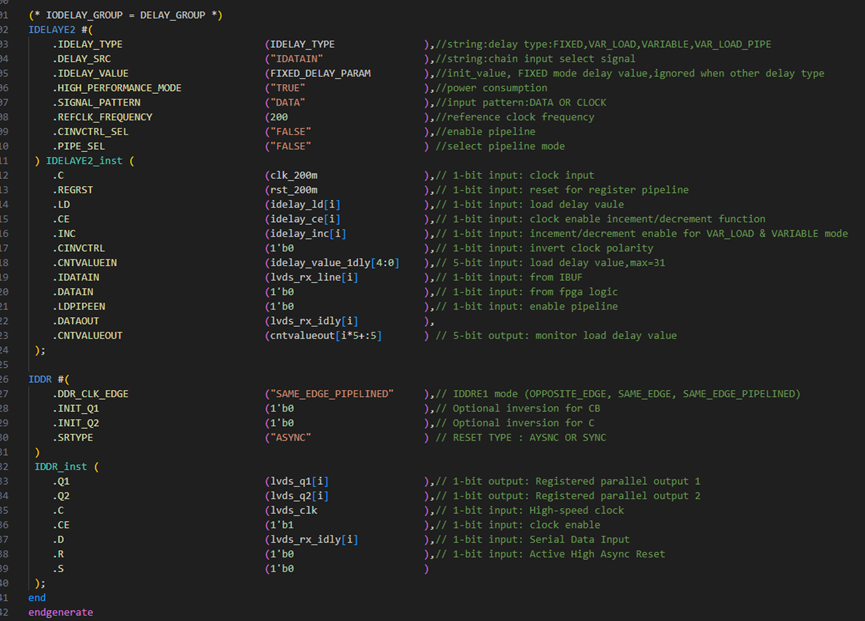

給DDR的數據線的時鐘添加延時

-

-

-

- 分析猜測5:ADC芯片未焊接好,導致LVDS模式下P/N某個腳無數據

-

-

1;在FPGA內部將ADC數據輸出的電平約束改為LVCMOS,發現通道2數據完全正確,但通道1仍不正確

2;在使用FPGA內部測試模式,輸出一個累加數據,發現ADC芯片通道1的bit15,13,12一直沒有數據,通道2正確

-

-

-

- 最終問題定位為ADC芯片通道1的15,13,12三個管腳未焊接好

-

-

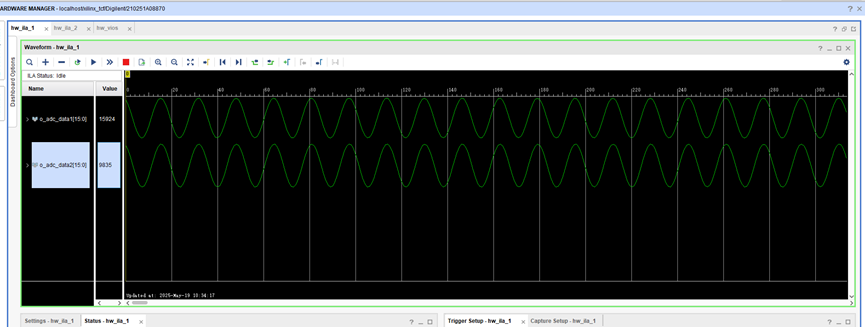

再次焊接后,輸入70MHz中頻,雙通道最終數據采集結果與環境記錄。

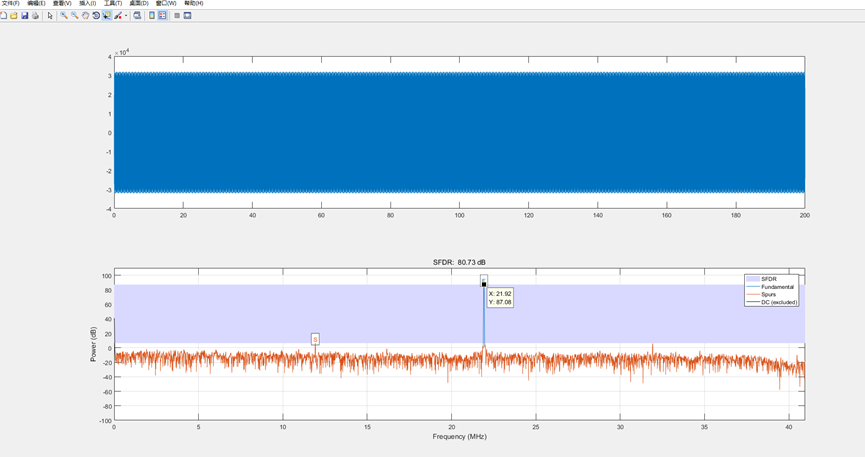

數據導入matlab,查看頻譜圖,分析信噪比:

以上頻譜可以看出,輸入70MHz中頻時,有兩個雜散,導致SFDR才80.73dB,還沒有達到datasheet的性能指標,還需要繼續調試。

這兩個雜散分布為主信號的左右兩側,且對稱,頻率為10MHz。模塊中,使用10MHz的晶振給PLL供時鐘,應該是這個10MHz泄露產生的。今天沒時間來調試了,請關注后續文章,來解決此問題的記錄。

)

)

)

)