5.8 約束規則的應用

5.8.1 層次化約束關系

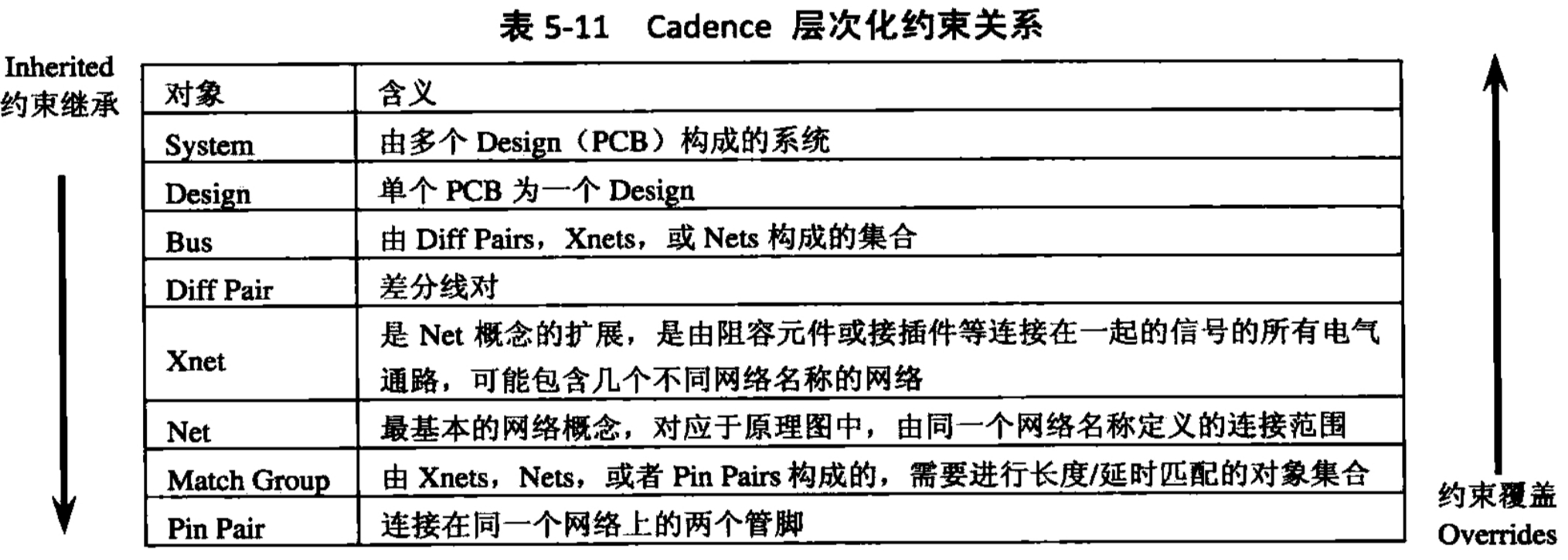

在應用約束規則之前,我們首先要了解這些約束規則是如何作用在 Cadence 設計對象上的。Cadence 中對設計對象的劃分和概念,如表 5-11 所示。

在 Cadence 系統中,把設計對象按層次進行了劃分,從高到低,依次為 System、Design、Bus、Differential Pair、Xnet、Net、Match Group 和 Pin Pair。從這個劃分中不難看出 Pin Pair 是最簡單的網絡連接關系,而 System 是最復雜的連接關系。規則的應用是按照表 5-11 中所示的繼承和覆蓋關系來進行的。例如,如果已經對一個總線定義了約束規則,但是沒有對具體的單個線網進行規則約束,那么屬于這個總線中的所有線網,都自動繼承屬于總線的約束規則。但是如果對某個具體線網定義了一個約束規則,而這個規則和總線中的定義相矛盾,那么這個具體線網的規則就具有更高的優先級,它會覆蓋總線中的這個約束規則,但是對總線中的其他線網沒有影響。

在 Cadence 系統中,把設計對象按層次進行了劃分,從高到低,依次為 System、Design、Bus、Differential Pair、Xnet、Net、Match Group 和 Pin Pair。從這個劃分中不難看出 Pin Pair 是最簡單的網絡連接關系,而 System 是最復雜的連接關系。規則的應用是按照表 5-11 中所示的繼承和覆蓋關系來進行的。例如,如果已經對一個總線定義了約束規則,但是沒有對具體的單個線網進行規則約束,那么屬于這個總線中的所有線網,都自動繼承屬于總線的約束規則。但是如果對某個具體線網定義了一個約束規則,而這個規則和總線中的定義相矛盾,那么這個具體線網的規則就具有更高的優先級,它會覆蓋總線中的這個約束規則,但是對總線中的其他線網沒有影響。

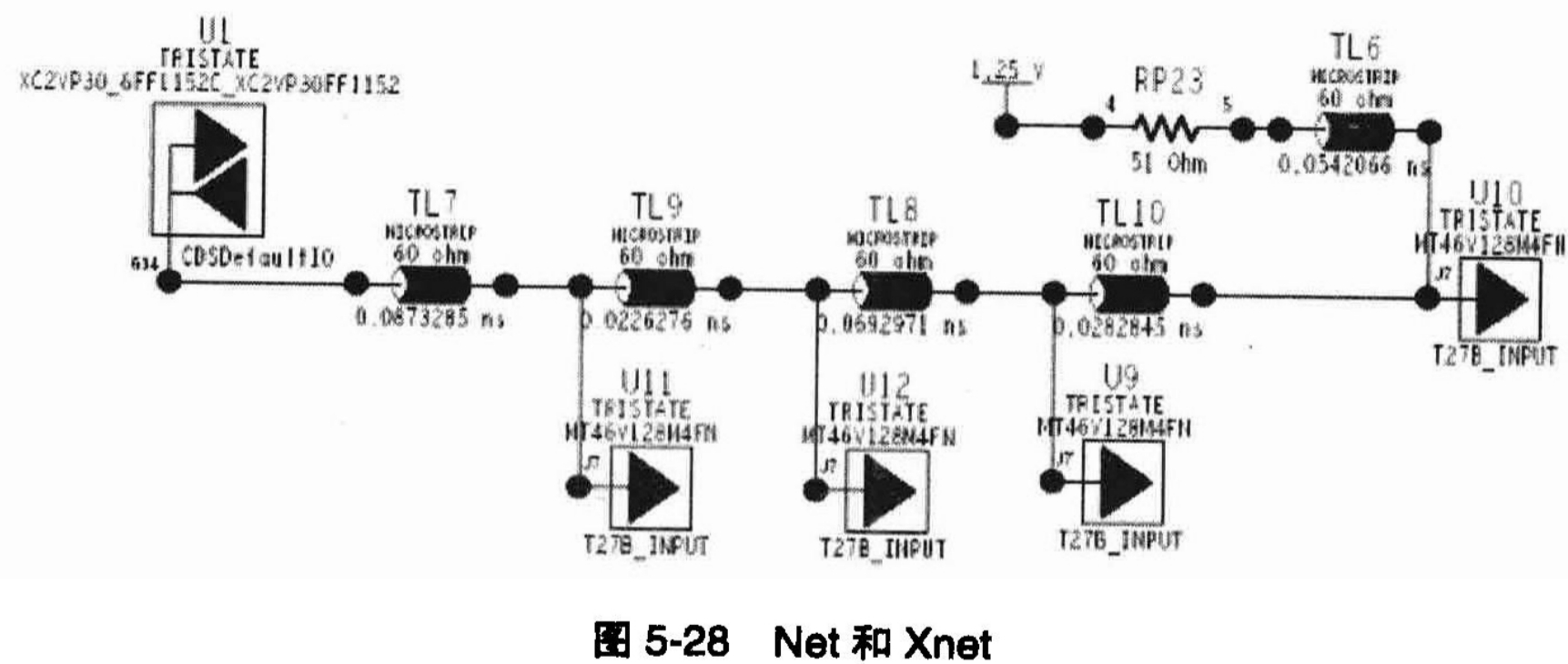

除了對 Xnet 需要進行解釋之外,讀者不難理解其他各個對象的含義和覆蓋范圍。由于 Xnet 是對 Net 對象的擴展,參照我們以前用過的圖,對照 Net 的概念,我們來講解一下 Xnet 的含義。

在圖 5-28 中,是我們對網絡名稱為“DDR1_A<0>”的 Net 進行抽取的結果。那么我們知道,在設計原理圖的時候,對于 DDR1_A<0>這個網絡的設計,是通過 U1、U9、U10、U11 和 U12 的相應管腳上直接定義的同一個線網名稱,從而定義了 DDR1_A<0>這個網絡的連接關系,然后又加了一個上拉電阻 RP23,一端連接在 DDR1_A<0>這個網絡上,而另一端直接連在 1.25V 的電源上。可是為什么我們在對 DDR1_A<0>這個網絡進行抽取的時候,會出現 1.25V 的電源呢(DDR1_A<0>和 1.25V 是完全不同的兩個網絡)?這是因為,實際上是 SigXP 對 DDR1_A<0>這個網絡進行的 Xnet 抽取。如同 Xnet 的定義所講的,只有對整個 Xnet 網絡進行抽取和仿真,才能夠確定 DDR1_A<0>這個網絡的傳輸特性。也就是說 Xnet 才是一個完整的電氣網絡,而我們命名的 DDR1_A<0>的網絡只是我們最感興趣的那個部分,是 Xnet 的一個組成部分,它并不構成一個完整的電氣傳輸路徑。這里請讀者思考一個問題,SigXP 怎么知道哪些 Net 網絡能夠構成一個 Xnet,答案就是對 RP23 這個電阻的模型的定義,也就是說如果我們在抽取之前沒有對 RP23 指定一個合適的器件模型,工具是不會按照這樣的邏輯進行 Xnet 網絡結構抽取的。所以,再次強調,對于器件模型的正確設置,是高速仿真分析工作的基礎。

?5.8.2 約束規則的映射

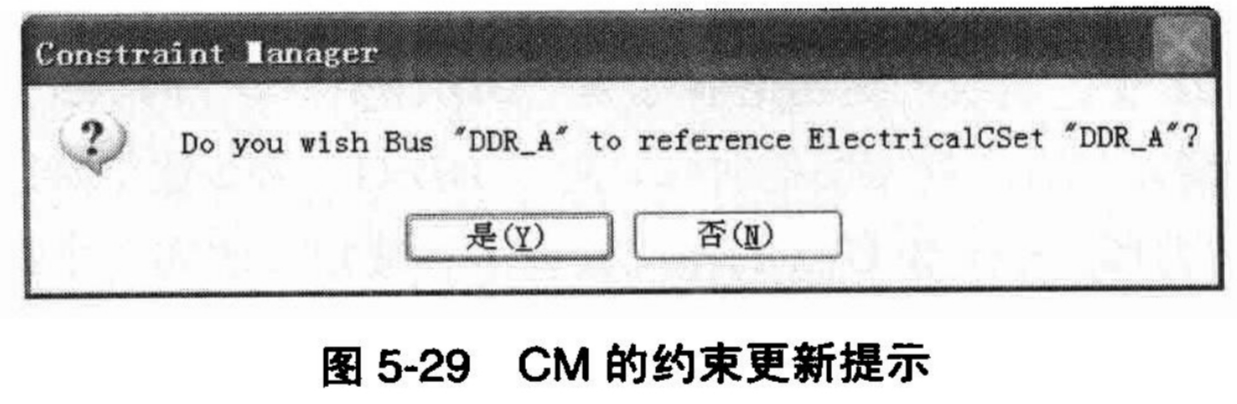

了解了 Cadence 中設計對象的分類及約束規則在這些對象上應用的原則,我們就可以開始使用這些約束來指導布局布線了。在 SigXP 中設置好的約束后,通過菜單中的“File→Update ConstraintManager”命令或者通過單擊工具欄上“Update CM”按鈕就可以將設置好的約束導入到 Constraint Manager 中。此時,返回到 CM 約束管理器工作環境中(也就是之前對網絡進行抽取的工作環境),會出現如圖 5-29 所示的提示對話框。

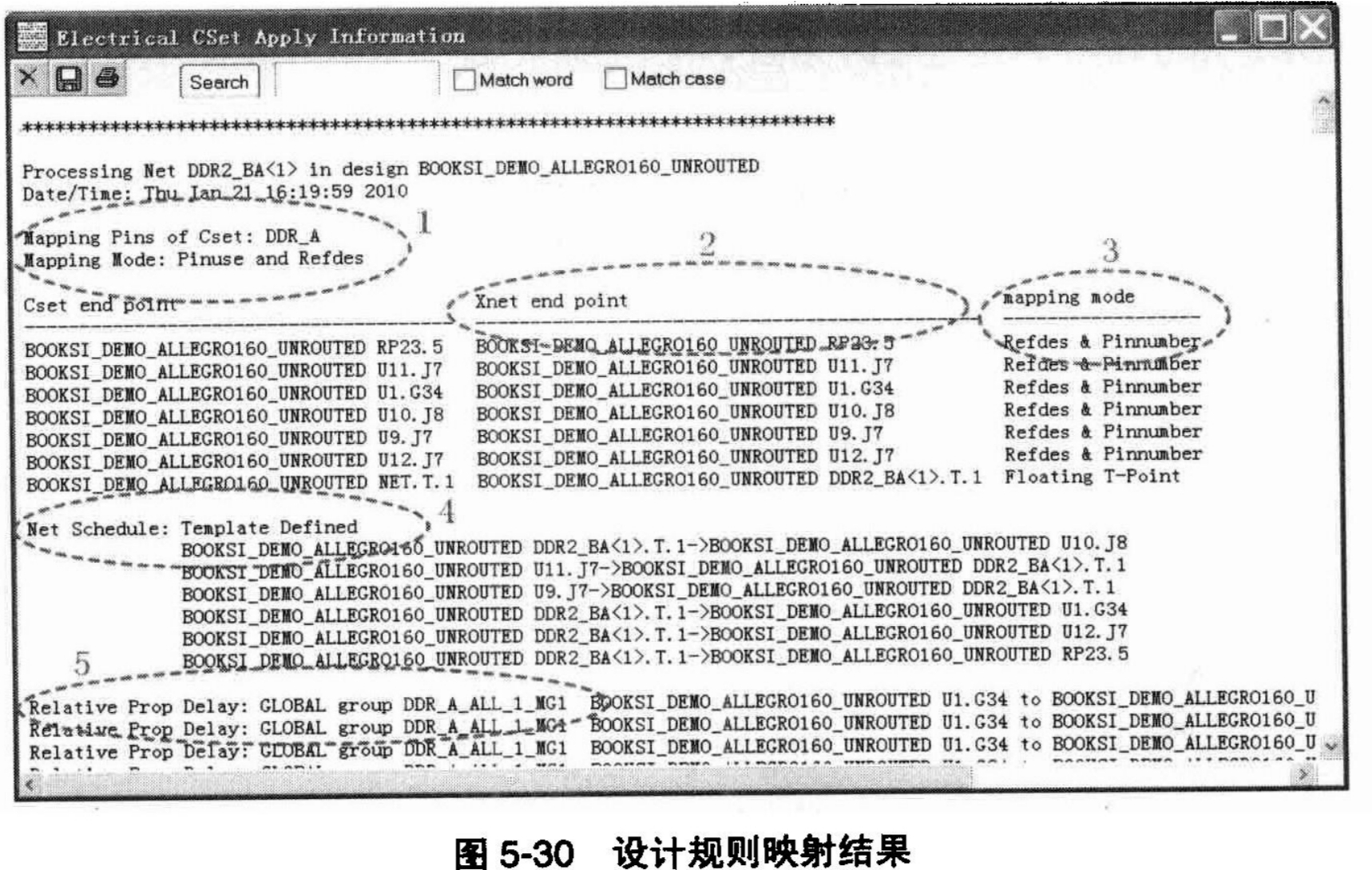

?單擊“Yes”按鈕接受約束更新,這時在 CM 的約束管理器中會出現該約束條件在系統中的映射情況,如圖 5-30 所示。

?要仔細閱讀一下這個 LOG 文件,檢查一下從 SigXP 中返回的約束及約束在 CM 約束管理器中的映射情況,例如,上面的 LOG 文件中,我們大致可以看到五個方面的內容,如圖 5-30 中的五個虛線圈的標記所示。

1. SigXP 生成的約束名稱和映射方式;

2. 該約束拓撲結構中所包含的網絡要素;

3. 拓撲結構的映射方式;

5.8.3 Constraint Manager 的使用

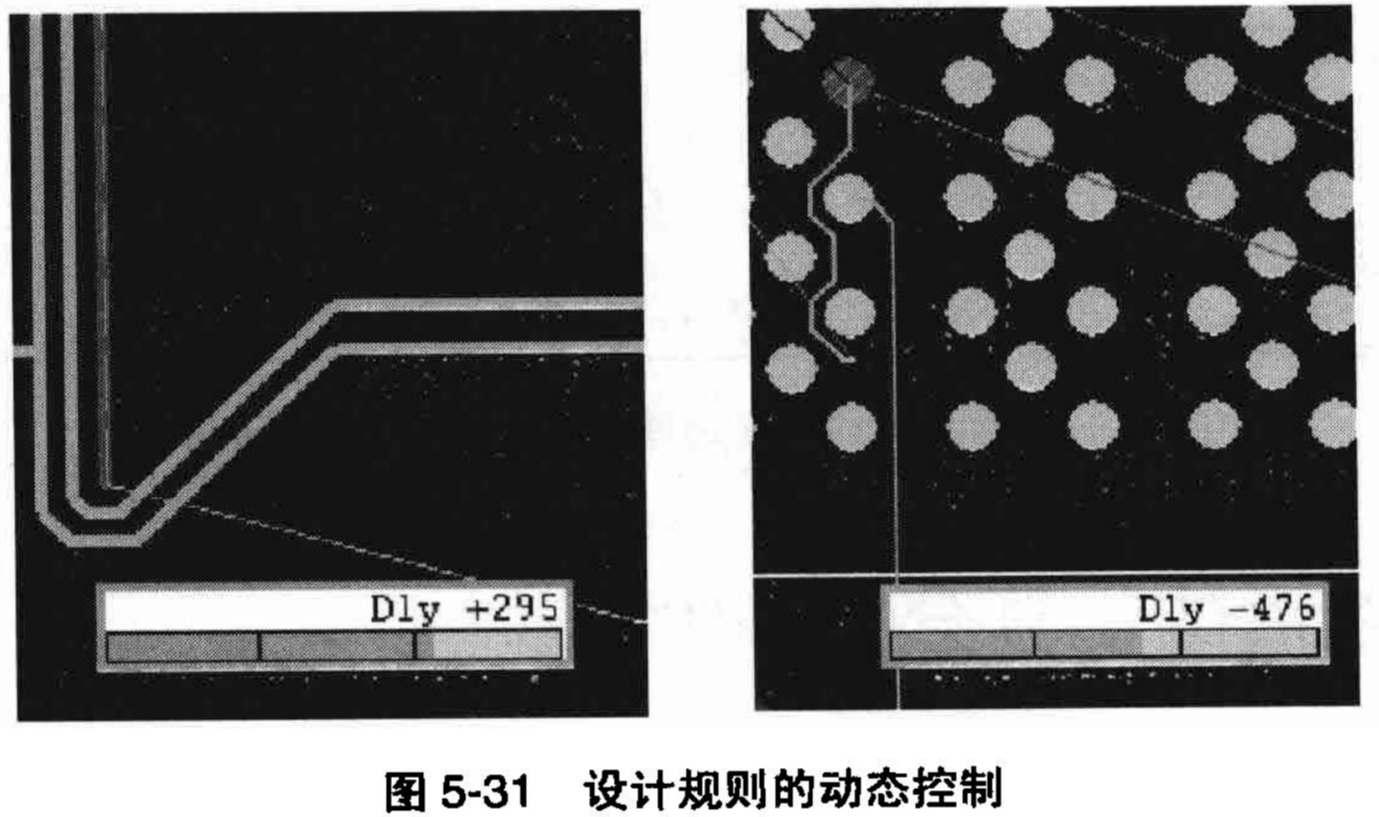

當約束規則被正確映射到 CM 約束管理器中的設計對象后,在 Allegro 中進行布局布線時,CM 約束管理器會實時檢查這些約束規則的執行情況,并以如圖 5-31 所示的提示框形式顯示這些信息。

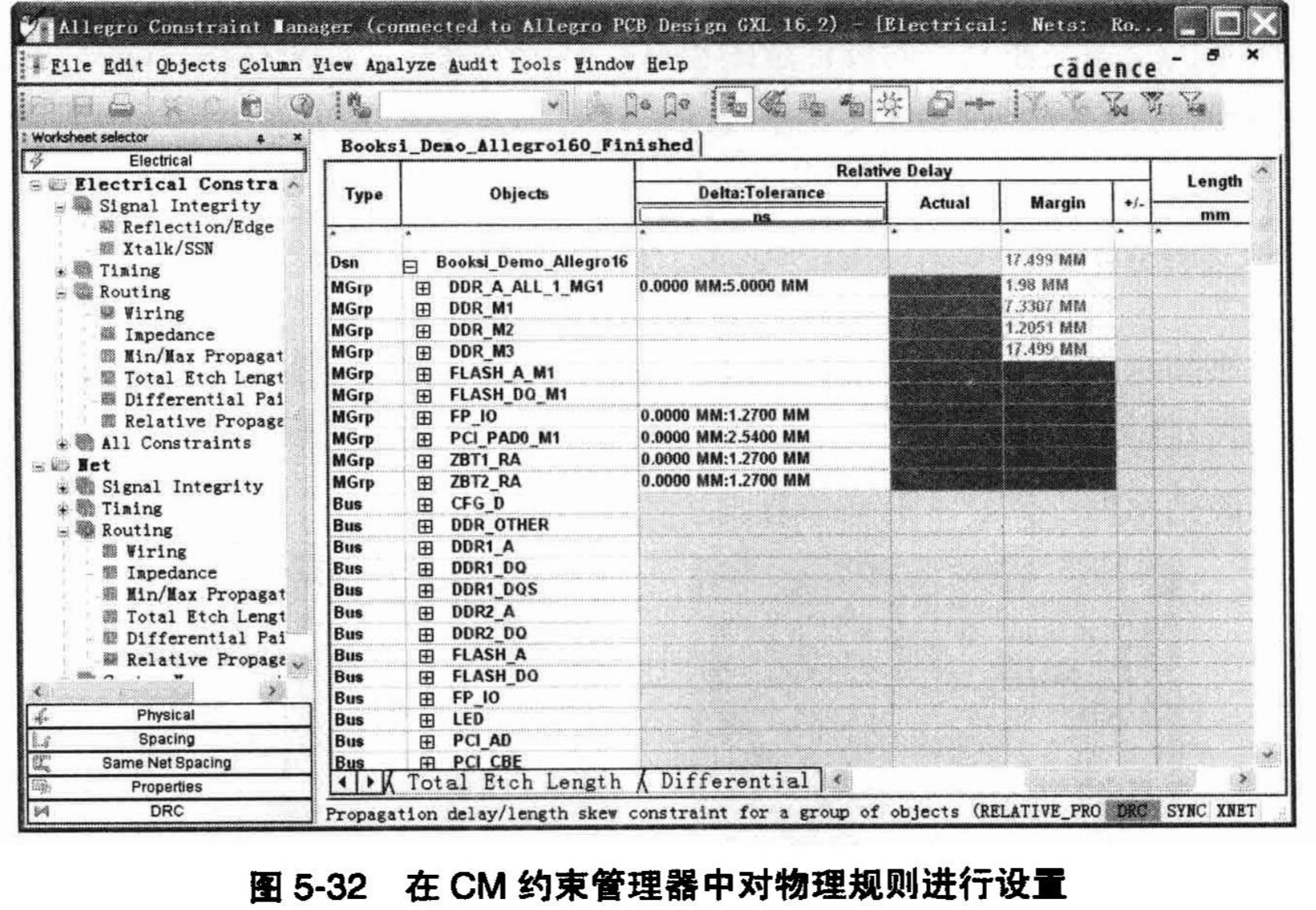

?另一方面,在設計過程中或者設計結束后,也可以通過打開 CM 的約束管理器,從總體上來觀察所有約束的執行情況。如果規則得到正確的執行,該項規則的執行結果及所有被該規則約束的設計對象會以綠色顯示;如果設計中違反了某個規則,那么該規則的執行結果及違反了該規則的設計對象會以紅色顯示,如圖 5-32 所示的例子,通過 CM 的約束管理器中這些明顯的標記,可以非常直觀并快速地對設計問題進行定位。

CM 的約束管理器不僅可以通過仿真來設置電氣規則,也可以根據實際的設計需要,直接設置一些物理規則。如圖 5-32 右下部分所示,在 CM 的約束管理器中可以直接對物理規則進行設置,如位于某層的線間距、線寬及過孔數量等。除此之外還有直接對網絡和器件屬性進行編輯管理的功能。總之,CM 的約束管理器是 Cadence 高速設計系統中,功能非常豐富和強大的設計規則管理工具。掌握好 CM 約束管理器的使用方法,對于提高高速系統設計的效率和正確性有很大的幫助。

除了這些基本的使用方法,為了用戶方便地進行約束管理及團隊合作的需求,CM 約束管理器還提供的約束規則的導入和導出功能,這樣就可以在同一個設計的基礎上,不同設計團隊之間,比如 SI 工程師和 PCB Layout 工程師之間,非常方便地直接進行約束和執行結果的信息交換。

5.9 布線后的仿真分析和驗證

在約束規則的指導下完成布局布線后,對于高速設計流程而言,就剩下了最后一步,那就是后仿真。很多工程師對這一步不太理解,因此也就不加以重視。但是,后仿真在實際工作中具有非常重要的作用。

5.9.1 布線后仿真的必要性

我們先來談一下后仿真的必要性。首先我們來考慮一種情況,那就是在前仿真時我們所使用的模型參數,包括傳輸線參數、過孔模型,以及關鍵信號的串擾等,這些參數值都是來自仿真假設或者理論計算,它并不是一個布線后系統的真實反映。我們的設計規則是在前仿真的基礎上得到的,那么在布線后就會有兩種可能,一種可能是由于前仿真的參數偏差實際值太遠,導致前仿真得出的設計規則沒有方法在實際布線中得到執行;另一種可能是,即使前仿真的設計約束得到了執行,但是由于布線后的系統參數發生了變化,很有可能出現一些前仿真時沒有考慮到的情況,以至于使得前仿真的結果可信度變差,甚至根本不再適用。這些問題的出現,使我們不得不在布線后再做一次仿真,一方面是解決前仿真中所設定的不恰當的規則定義導致的問題,另一方面根據后仿真的參數,來驗證來自前仿真的規則在布線執行后的可信度。

還有一些情況在前仿真時無論如何也考慮不到的,比如串擾分析和關鍵信號的 EMI。在前仿真時所做的串擾分析,只是針對某個具體的線網對串擾的承受能力進行分析,按照這個分析結果來做出一些預防性的設計措施。按照這個“預防性”的串擾約束進行布線,并不見得能夠達到預期的目標,但是在布局布線之后,所有的網絡都已經有了固定的位置,線網之間的并行距離和間距都是真實可見的,這個時候所做的串擾分析就是實際情況的真實反映了。對于布線后仿真 EMI 的真實性和作用,相信讀者更能夠理解,當關鍵信號網絡處在真實的布線環境中和真實的參考平面下,所做出的 EMI 分析才是正確的。而這些真實的環境,對于前仿真中的 EMI 是無法做到的,因此幾乎沒有人會在前仿真的流程中去做 EMI 分析。

5.9.2 布線后仿真流程

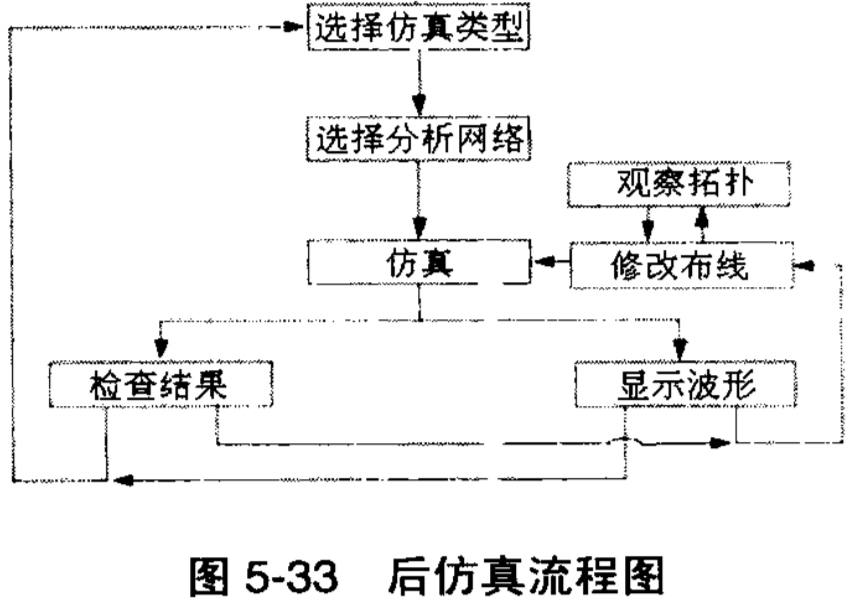

如上一節所述,后仿真的作用不僅僅是作為高速設計中 SI 工作 Sign-off 的一個步驟,更重要的是要在后仿真階段,處理在前仿真過程中沒有預料到的情況,以及完成那些不可能在前仿真中完成的任務。因此,在后仿真流程中,首先要進行比較全面的仿真,然后針對仿真中發現的問題,對問題進行定位,選擇相關的網絡進行仿真并解決問題。后仿真的流程如圖 5-33 所示。

?由于在前仿真中,我們已經按照層次化的設計方法對信號完整性問題進行了分類仿真,并按約束規則驅動進行了布局布線,這樣使得在后仿真中發現的問題成為可控并可精確定位的。根據作者的經驗,解決在后仿真中發現的問題,一般要以前仿真的工作結果為基礎。這是因為,后仿真中發現的問題,一般都是在布局布線中,由于物理參數的改變而引入的新問題,應該著重從多個網絡之間的物理關系入手尋找解決方案,而不是輕易去否定前仿真中對單個網絡所做的優化設計,除非有足夠的理由這樣做。從這里也可以看出,前仿真中所做的工作越充分可靠,后仿真的工作量和壓力就越小,即使發現新的問題,也容易定位和解決。

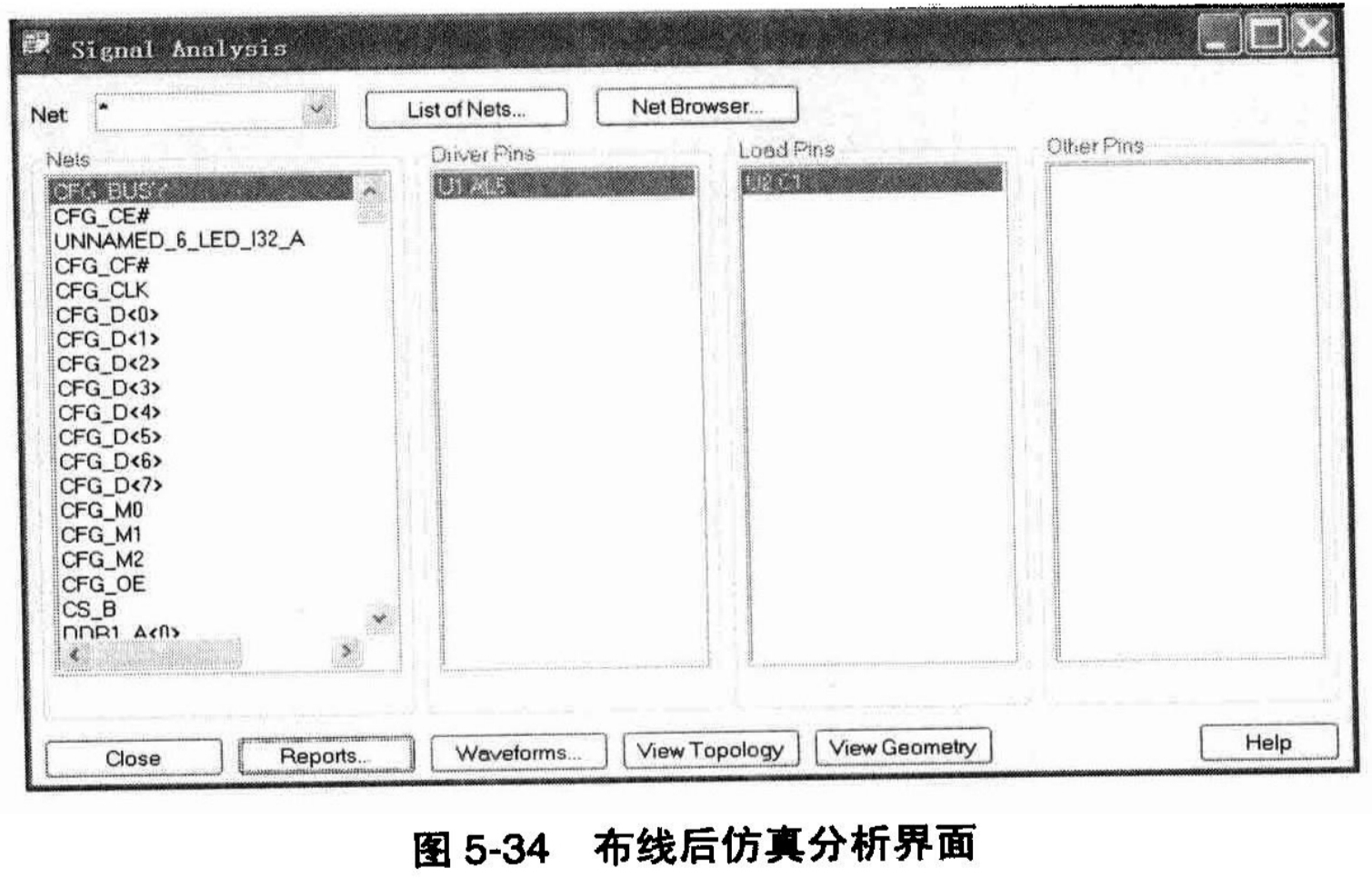

后仿真的執行步驟和前仿真的步驟有些差別,但是其基本原理和計算引擎還是一致的。在 PCB 設計環境的菜單中,選擇“Analyze→SVEMI→Prob”命令,啟動后仿真界面,如圖 5-34 所示。

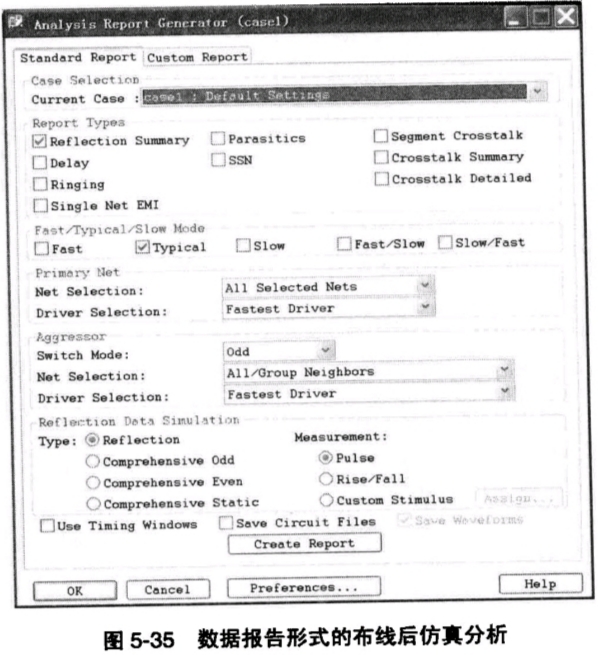

?在圖 5-34 中,可以通過設置網絡名稱的匹配模式,來選擇網絡進行分析。可以選擇單個網絡,也可以選擇多個網絡,然后單擊“Reports”按鈕,就進入了后仿真分析的參數設計界面,如圖 5-35 所示。

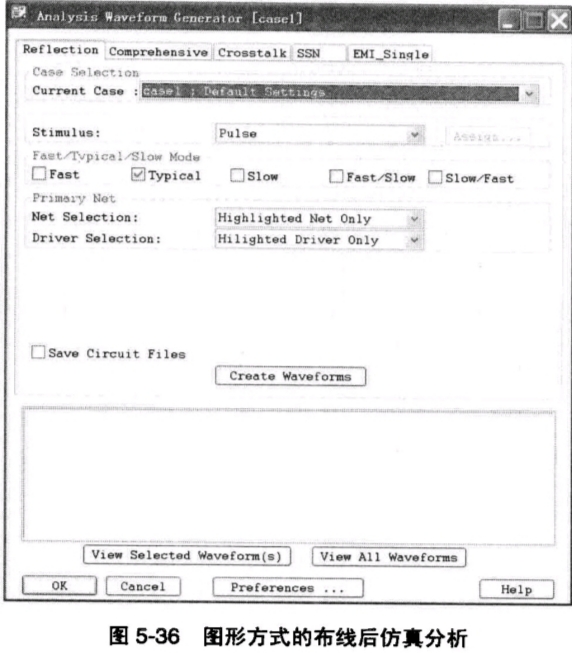

?我們已經做過前仿真的流程,所以對這里出現的參數和含義不再詳細講解,相信讀者(或通過“Help”文檔)能夠理解這些參數的設置含義及作用。需要說明的是雖然后仿真的結果通常以數據表格的方式給出,但是用戶還是可以選擇查看圖形方式的仿真結果。例如在上一步中,不去單擊“Reports”按鈕,而是選擇單擊“Waveforms”按鈕,就會出現如圖 5-36 所示的關于 Waveforms 的參數設置界面。

?不論用戶選擇哪種后的仿真形式,Cadence 系統中所運行的軟件都是一樣的,SigNoise 分析引擎,當然結果數據也是一樣的,只是 Reports 提供給用戶的是數據報告,而 Waveforms 提供的是圖形。之所以 Cadence 會以數據報告的方式提供后仿真結果,這是因為方法學的問題。在前仿真中,我們一般去仿真具有典型意義的網絡,然后把這個網絡的分析結果設置為規則,應用到同類型或者類似的網絡中。而在后仿真中,沒有哪個網絡具有高于其他網絡的典型意義,每個網絡在布線后的系統中都需要同等對待,加以重視。

舉個例子,在系統中有 DDR 的地址總線,DDR_A<13..0>,前仿真時,因為此時系統中存在的只是邏輯關系,并沒有連接的物理信息,所以我們可以隨意抽取其中的一根信號線,比如 DDR_A<0>,來代表 DDR_A 總線加以分析,并把得出的約束規則應用到 DDR_A 這個總線上進行布線。經過布線后,在 DDR_A 這個總線中,沒有哪兩個信號線所處的實際物理環境是相同的,沒有哪個網絡具有典型意義,我們必須在后仿真中對 DDR_A 中的所有信號線加以驗證。這個時候,如果再像前仿真時候那樣,逐個抽取圖形化的網絡表示,然后逐個繪制仿真波形,會顯得十分煩瑣,在實際操作中也是不太現實的。一個是浪費很多時間來繪圖,另一個是對用戶來講,逐個對比波形圖不如直接讀取數據進行對比更方便和高效。

如果在數據報告形式的后仿真分析結果中發現某些性能沒有達到設計目的,那么就需要對個別網絡進行特殊處理。這時可以使用類似前仿真中的流程,單獨對該網絡進行拓撲結構抽取,進行仿真驗證,甚至修改約束及重新布線。但作者推薦,在后仿真中發現問題后,首先要去檢查相關網絡的約束是否合理,一般來講,在約束合理的情況下,對沒有達到性能要求的網絡進行單獨的優化和調整,很快就能夠達到約束要求。

在沒有得到 SI 工程師確認和許可的情況下,不要輕易去修改約束要求,以使得后仿真結果變得“好看些”。對設計約束的修改非常危險,因為這樣做通常會影響到很多網絡,造成更加不可預期的后果。后仿真遇到最多的問題是串擾超標,因為在前仿真時,是沒有辦法對線網周圍的情況進行考慮得非常完善周全的。通過適當調整布線能夠解決大部分的問題。

5.10 電源完整性設計

盡管在 Cadence 的高速設計流程中沒有顯示 PI 這個環節,但是作為一個真正的高速系統設計,PI 是必不可少的內容。在這一節中,我們先來談談 Cadence 中對于電源完整性設計的思路和理念,然后介紹在 Cadence 設計工具中,如何實現電源完整性設計。

需要讀者注意的是,一個完整的電源完整性設計需要設計者充分了解電源完整性涉及的各個元素,并逐個對設計元素進行精確建模。這里所說的不僅是對靜態設計元素,如系統中所使用的疊層結構、電源/地平面及所使用的去耦電容器件的建模,還需要對系統的動態行為進行建模,如系統中每一個電源路徑上的所有負載在某個時刻的 I/O 行為對電源系統的需求等。對于系統設計者而言,目前還缺乏對這些設計元素進行精確建模的方法。而從另外一個角度講,即使有了這些建模的方法和資料,要完成這些模型的設計并應用到實際的電源完整性分析中,所獲得的收益與付出的勞動時間成本相比也是不劃算的。因此,在這里再一次體現了貫穿于仿真分析工作中的一個方法學問題,那就是時間和效率的均衡問題。在有限的時間內,在一定的設計和生產成本控制范圍內,完成設計是工程師所關心的最終目標。因此,在以下的 Cadence 電源完整性設計環境中,也是按照工程學的方法(相對于科學研究而言)在一定條件下進行“精確”仿真,來完成電源系統設計。

5.10.1 電源完整性設計方法

隨著現代高速信號的速率越來越高,信號邊緣越來越陡,而芯片的供電電壓持續下降,使得設計一個干凈穩定的電源供電系統越來越具有挑戰性,對于電源系統的分析也越來越難以控制。為了應對高速設計的挑戰,在沒有 PI 仿真的保證下,工程師們不得不在設計中使用更多的電容,期望通過“過度的設計”(Over Design)來確保電源系統的安全。而事實上,這種電容數量上的增加,是非常盲目的,它并不能保證電源系統的安全性,與此同時也不可避免地增加了系統設計和生產成本,影響產品的市場競爭力。

Cadence 的 PI 仿真環境為電源系統的設計并提供了一套完整的工具和設計流程。使用這套工具和流程,用戶可以輕松解決高速電源系統中所面臨的兩大難題。

? 對于一個特定的設計而言,應該使用哪一類電容,以及每類電容的數量如何配置?

? 在布局布線設計中,如何確定電容的確切位置,以達到最佳設計效果?

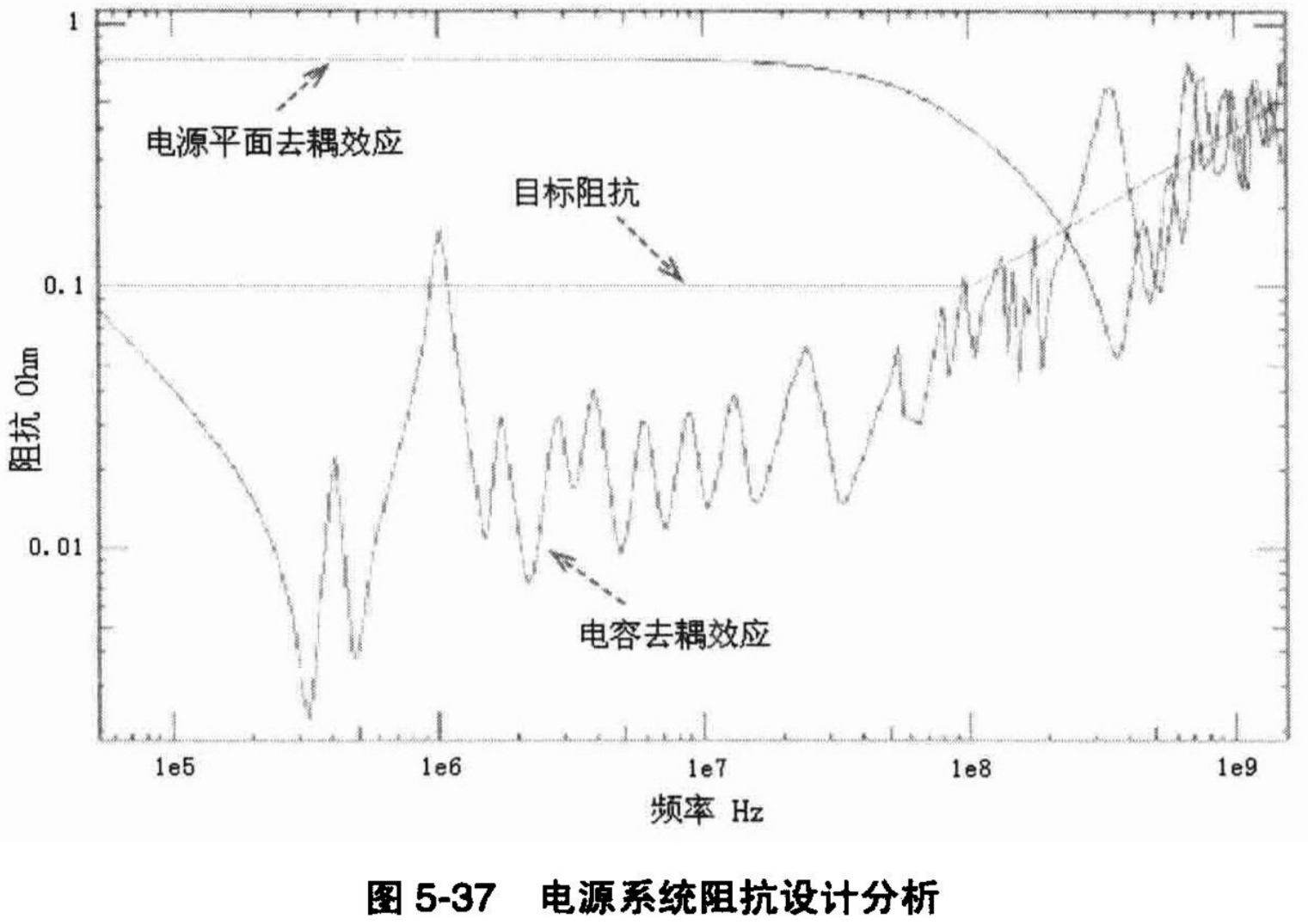

通過第 3 章的學習,我們已經了解到,對于電源系統的設計,其設計目標就是要使整個電源系統阻抗足夠小,能夠滿足在瞬間為系統中的功能部件提供所需的電流,并保持一定的電壓紋波。由于在一個系統中,所有的功能部件并不是工作在同一時刻域下的,即使是同一個時鐘域下的功能部件也不一定就在同一時刻對電源系統有供電要求。因此沒有辦法精確地知道所有功能部件對電源系統的確切需求。那么我們就必須進行保守設計,為系統中所有的可能工作頻段設計出一個較低的目標阻抗。如圖 5-37 所示的中間位置是目標阻抗曲線,如果我們能夠設計出系統的阻抗在整個工作頻段內都低于目標阻抗,那么就可以說這樣的設計是成功的。(作者注:事實上,這里提到的關于電源完整性的保守設計,也是一種“過度的設計”。正如前面所說,到目前為止,所有的電源完整性分析軟件都沒有辦法完全復制一個產品中電源系統的所有行為,那么只能通過設計一個在任何時刻、任何頻率下都滿足要求的電源系統,則一定能夠滿足該產品對電源系統的需求。只是這種在仿真軟件指導下進行的“過度的設計”比純粹的盲目設計更近了一步,至少根據去耦電容的特性和數量進行了有目的的設計,已經在設計安全性和生產成本中取得很大的優勢,這是我們使用電源完整性設計的主要原因。)

又如我們在第 3 章中所學到的,穩定的電源系統設計,包含多種設計因素的綜合結果,這些因素包括:電源供電模塊、供電系統的去耦電容、PCB 疊層的電源—地平面結構,以及 IC 芯片的封裝和 IC 芯片內部的電源去耦結構設計。而在這些因素中,電源供電模塊和 IC 芯片的特性,對于系統設計者而言是沒有能力進行干預的。因此,對于系統設計者而言只能從供電系統的去耦電容和 PCB 疊層中的電源—地平面結構這兩個方面入手。在進行實際的設計之前,我們有必要了解這兩個因素對整個電源系統阻抗的影響。根據研究結果,在電源供電系統中分布的去耦電容,它們的諧振效應對降低電源系統阻抗主要體現在幾百 KHz 到幾百 MHz 的頻段之間,如圖 5-37 中下部的 Capacitor 諧振曲線所示;而疊層結構中的電源—地平面的諧振效應主要體現在幾百 MHz 到 GHz 的頻段之間。這個結論告訴我們,在進行系統阻抗設計時,應該依據各設計因素的諧振特性,進行分頻段獨立的設計。

?有了這樣的設計理念,我們可以先進行去耦電容的選型和數量的設計研究,而暫時不去考慮電源—地平面的諧振影響,在確定去耦電容的選型和配置策略之后,再考慮如何優化電源—地平面結構。但是如果當電源—地平面足夠大的時候,有可能電源—地平面的諧振點和一些高頻電容的有效去耦頻段會重合,這時要精心選擇適合的高頻去耦電容,以便消除電源—地平面諧振點的影響。

為了方便讀者對 Cadence 電源系統的設計方法進行理解和掌握,我們還是按照 Cadence 的 PI 設計流程對如何進行電源完整性設計進行講解。在學習過程中,讀者可以體會 Cadence 的 PI 設計方法如何解決本節開始提出的高速電源系統中面臨的兩個難題。

在 Cadence 的 PI 設計方法中,可以分為如下幾個階段。

? 設置電源完整性仿真參數數據庫;

? 定義目標阻抗;

? 單節點仿真分析;

? 多節點仿真分析。

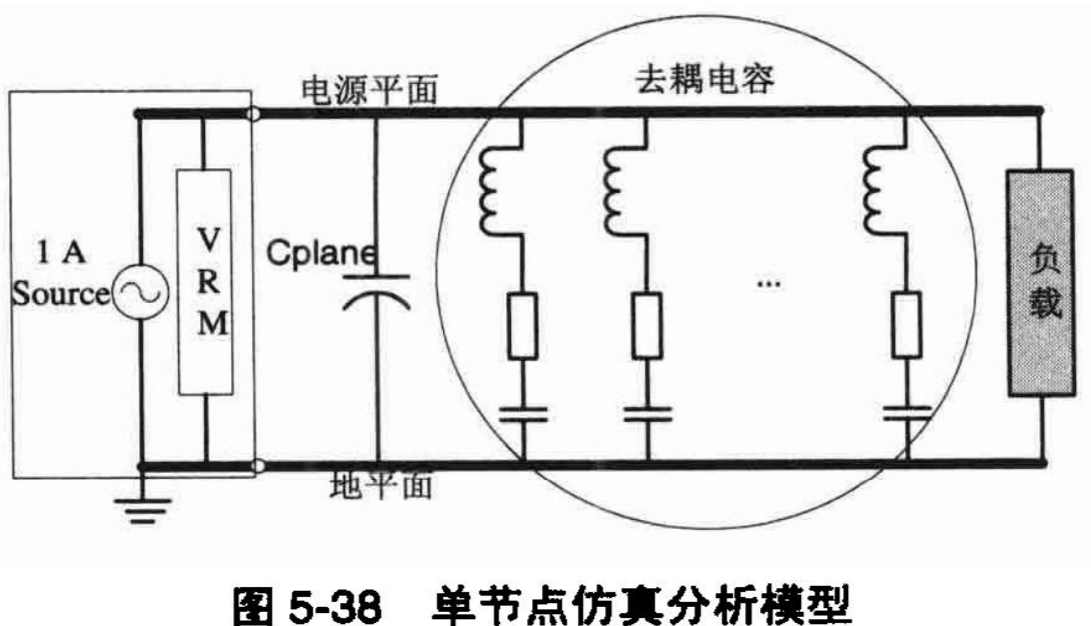

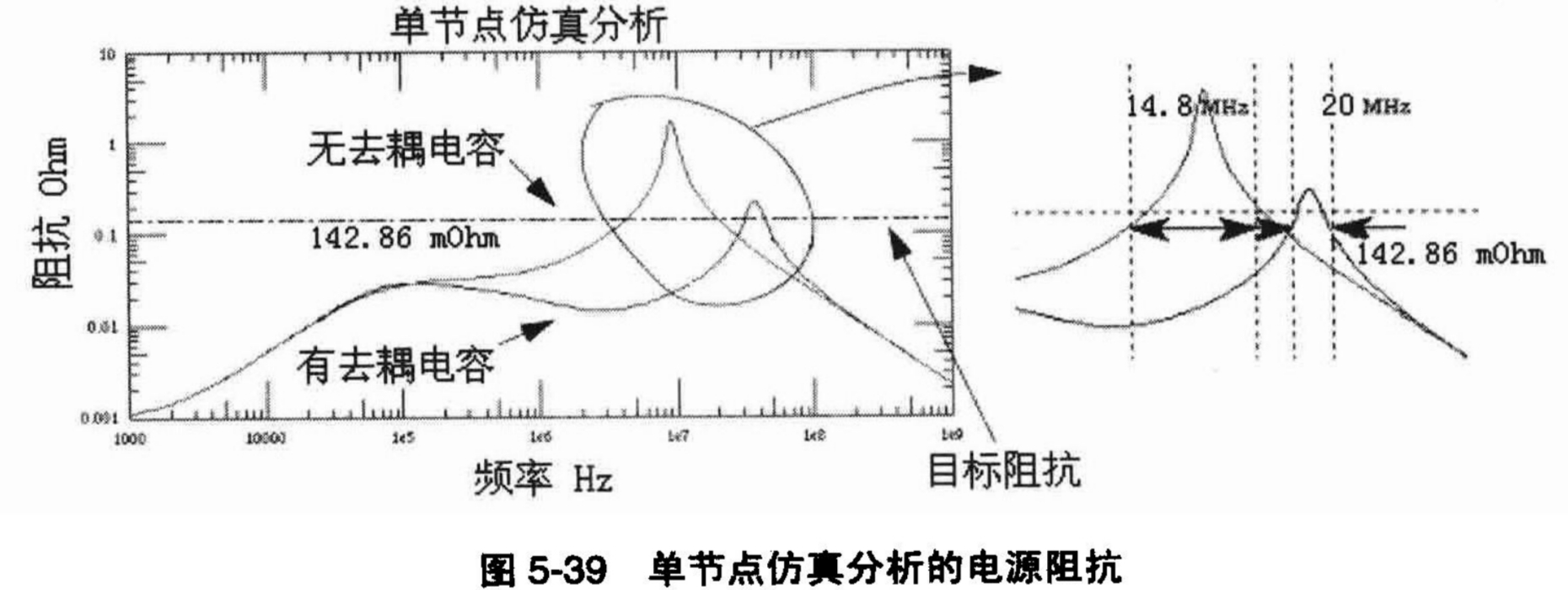

前兩個步驟顯而易見,是為了仿真分析做準備,對仿真進行參數設置。而后面的兩個步驟是對電源進行仿真分析的兩種形式,也是完成電源仿真分析的兩個步驟,單節點仿真分析是為了驗證系統中所使用的電容數量和種類能否滿足要求頻段內的阻抗,因此它不考慮電容在 PCB 中的具體物理位置。單節點仿真分析的電路模型如圖 5-38 所示。

?在單節點的模型中,假設所有的電容都連接在一起,電源調壓模塊 VRM、仿真激勵源、1A 的電源和電容并聯在一起。顯而易見,在這個模型中,忽略掉了電源系統中各元素實際的物理連接性(也即忽略了實際的連接阻抗)。通過單節點仿真分析,我們可以知道所選擇的電容種類和數量是否能夠滿足電源分配系統的阻抗要求。如圖 5-39 所示是一個例子,在這個例子中,加入電容以后的電源分配系統的阻抗明顯降低了,但是諧振頻率仍然在 21MHz 左右,阻抗超出了目標阻抗,因此可以判斷,在這個設計中仍然要加入一個去耦電容,并且它的諧振頻率應該在 21MHz 左右,用來降低電源系統的阻抗。

?讀者應該注意到,盡管單節點仿真分析可以確定去耦電容的種類和數量,但實際的電源系統阻抗不僅取決于去耦電容的種類和數量,還取決于電容的分布位置。為了獲得更精確的結果,應該按照布局布線后的去耦電容參數,噪聲源及 VRM(Voltage Regulator Module)的實際物理位置,在整個相關頻率范圍內進行多節點仿真。多節點仿真從設計文件的實際布局提取物理參數進行精確仿真,這是多節點仿真和單節點仿真的最大區別。從這點來看,單節點仿真類似于 PI 的前仿真分析,用來確定去耦電容的種類和數量;而多節點仿真就是 PI 的后仿真分析,布局布線后的實際仿真分析,用來優化疊層設計和電容布局。

5.10.2 電源完整性設計分析步驟

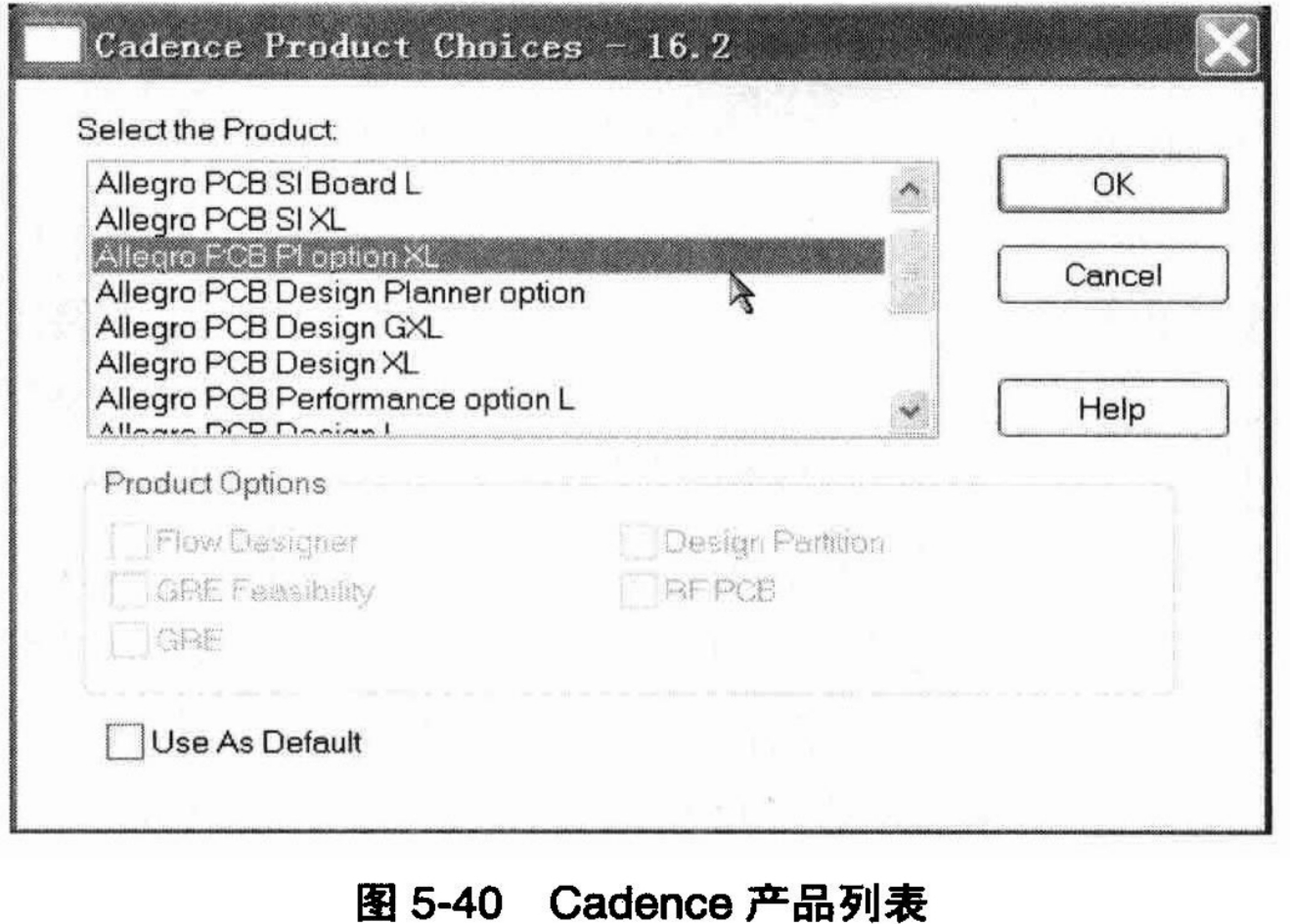

要使用 Cadence 提供的電源完整性分析工具,用戶需要有相應的 License。Cadence 的 PI 工具作為一個單獨的分析模塊,獲得相應的授權后,它會出現在產品選項的列表框中,如圖 5-40 所示。因此,要進行電源完整性分析,首先必須改變當前所使用的 Cadence 產品選項,然后選擇“Allegro PCB PI option XL”選項。

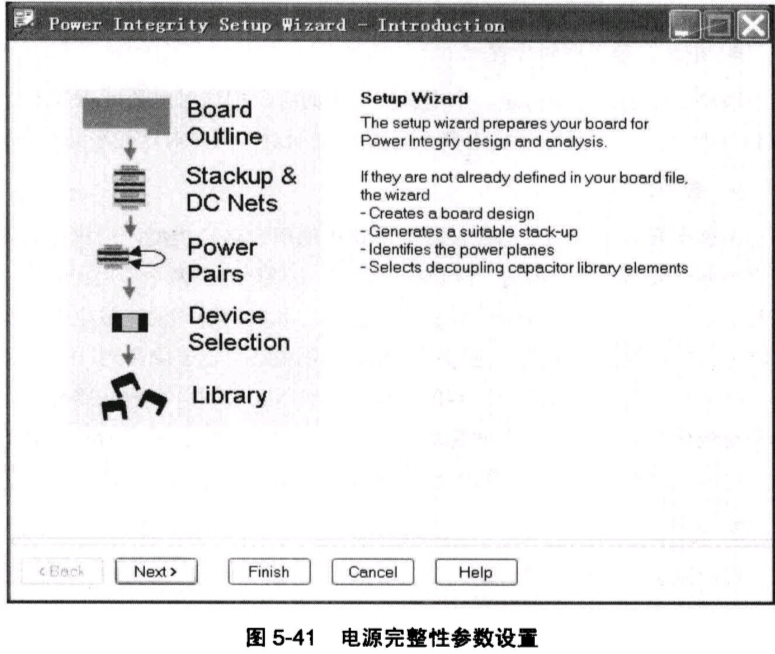

?如前一節內容所述,進入到 Cadence 的電源完整性設計環境后,第一次使用 PI 工具進行仿真分析之前,需要對設計環境進行參數設置。這個過程和對高速信號進行仿真分析前的參數設置非常類似,相信使用過信號完整性分析工具的讀者能夠很快適應這個 PI 的參數設置過程。在菜單中選擇“Analyze→Power Integrity...”命令,如果用戶是第一次在設計中啟動 PI 工具,那么系統會自動彈出參數設置界面,如圖 5-41 所示。

從這個“Power Integrity Setup Wizard—Introduction”界面看,它會引導用戶按照界面左邊的流程一步一步完成設計環境所需參數的設置。這些參數包括如下幾種。

? 板形外框設置;

? 疊層設計和電源電壓設置;

? 器件選擇;

? 器件庫選擇。

?這些參數中有一些與高速信號仿真分析的 SI 參數設置中的參數相同,有些是電源分析中所特有的。為方便讀者理解,這里對每個參數設計過程及其對電源完整性分析的含義做個介紹。

? 板形外框設置

PI 的仿真工具需要完整的板框信息進行電源平面的參數抽取和器件布局,PI 仿真環境會自動讀取設計文件中已有的板框信息,一般無須修改。但需要注意的是,這個板框的定義和實際設計文件中的板框有些不同,原則上 PI 仿真工具需要一個方形的區域進行仿真分析。所以,用戶可以指定一個區域,作為“板框”,它只是用來做 PI 仿真,并不是真正的板框。用戶可以根據自己的仿真需要定義這個仿真區域。

? 疊層設計和電源電壓設置

對于電源完整性設計,讀者不難理解這個參數的必要性。同樣,PI 仿真環境會自動讀取設計文件中已有的疊層信息,以及在各個電源平面中已經存在的電源平面劃分和相關網絡的指定。設計者需要核對在這個參數設置界面中所顯示的信息,一般沒有錯誤,無須修改。PI 仿真分析工具會根據這些信息進行電源平面的參數抽取。注意,并不是所有的電源平面劃分都可以進行 PI 分析,如果所劃分的電源平面面積比較小,那么 PI 將忽略對這個平面的分析。用戶可以在“Power Integrity Control”界面中指定要分析的電源平面的最小面積參數。

? 電源、地平面對設置

用戶通過這個界面指定一個電源和地平面對,把這對電源/地平面對作為接下來的 PI 分析對象。可以一次指定多個電源/地平面對,同時對這些平面對進行仿真。

? 器件選擇

在這個界面中列出了當前設計中所使用的所有電容類型,用戶可以指定哪些電容器件可以參與到當前的 PI 仿真分析中。去耦電容有兩個作用,一方面是集成電路的蓄能電容,提供和吸收該集成電路開門和關門瞬間的充放電能;另一方面旁路掉該器件的高頻噪聲。選取好的高頻去耦電容可以去除高到 1GHz 的高頻成分,陶瓷片電容或多層陶瓷電容的高頻特性較好。在設計印刷線路板時,最好在每個集成電路的電源和地之間都加一個去耦電容,當然要看是否有足夠的物理空間。對電容的種類和數量的配比選擇原則,請參考 3.5 節中的內容。

? 器件庫選擇

用戶既可以從設計文件中提取電容類型,也可以從庫文件中提取電容和電容的器件模型。這樣做的目的是使用戶有機會修改不受當前設計中所包括的電容類型的限制,可以通過添加其他類型的電容來改善電源完整性設計。一般推薦使用該界面下的“Project Library”選項,這樣在 PI 設計中所使用的電容可以和原理圖設計中使用的庫文件同步。如果在這個階段對去耦電容進行了比較大的修改,可以直接反標到原理圖設計中,而如果選擇了其他類型的庫文件,那么這些對去耦電容的修改是不能和原理圖設計同步的。

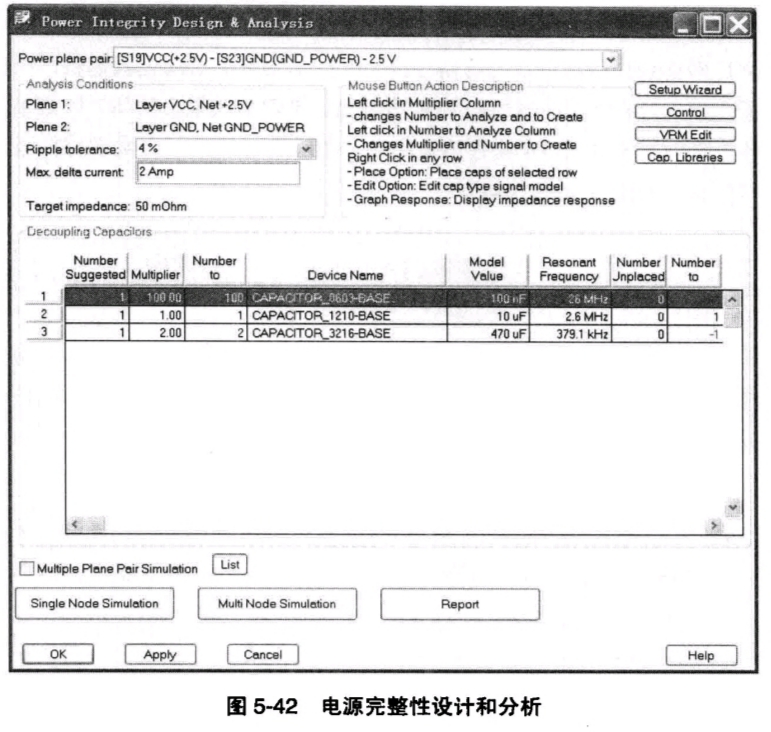

按照流程設置好這些參數之后,最后就會進入到如圖 5-42 所示的電源完整性分析界面。在進行仿真分析之前,用戶還需要在這里對要確認電源完整性分析的平面設置目標阻抗和仿真類型(單節點仿真或多節點仿真)。單節點仿真的設置比較簡單,只需設置目標阻抗參數及選擇所需電容數量即可。對于多節點仿真,由于涉及噪聲源和電容具體的物理位置及電容布線參數,就需要用戶單擊界面中右上角的“Control”按鈕,進行其他一些關于多節點仿真分析的設置。

?5.10.3 多節點仿真分析

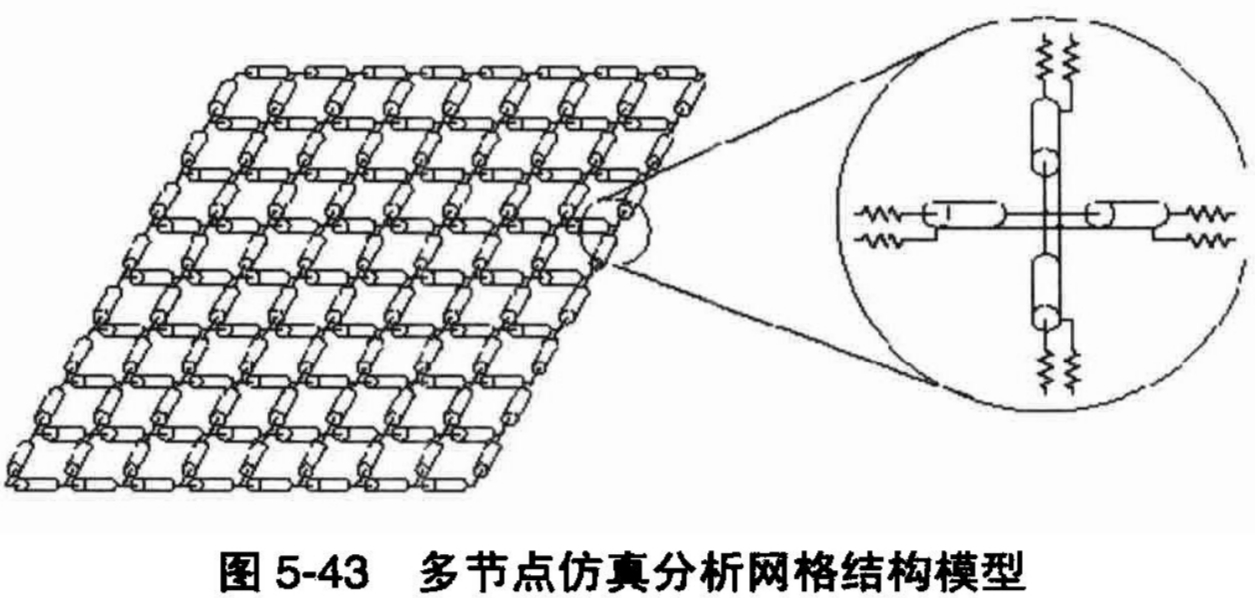

由于分析方法的不同,多節點仿真需要更多的參數及參數控制。在進行這些參數設置之前,我們首先需要了解多節點電源完整性仿真分析的原理。多節點仿真分析是按照用戶定義的網格尺寸,通過將電源/地平面分隔成若干獨立的網格,對每個網格進行 RLC 建模,并將 VRM、噪聲源及去耦電容按其布局中的具體位置連接到合適的節點上,通過確定每個節點附近的阻抗來進行更精確的仿真的。如圖 5-43 所示是電源平面的網格結構模型。

?為使仿真準確,網格尺寸的大小必須大于系統最高頻率所對應波長的 1/10。當然,網格劃分得越細,仿真精度越高,但是仿真的時間也就越長。一般取系統中最高頻對應波長的 1/10,就能得到比較準確的結果。例如,如果系統的最高工作頻率為 133MHz(DDR 存儲模塊的工作頻率),電路板介質材料是 FR-4,介電常數 ε 為 4.5,于是波長如下:Wavelength=光速C/(信號頻率x√介電常數)=3x10^8m/s/(133MHz? x√4.5)=1063.32mm

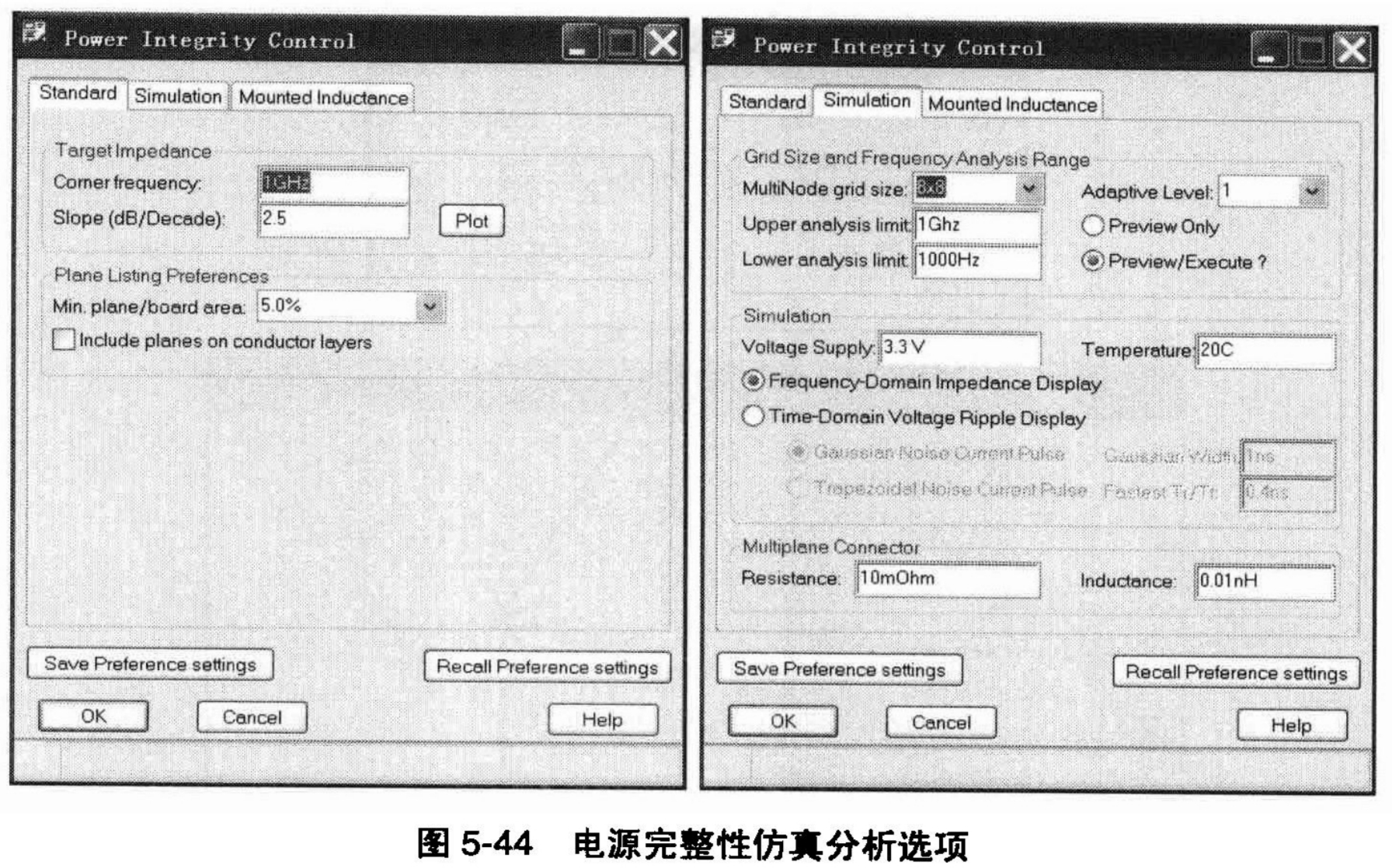

計算完仿真所需的網格尺寸之后,在圖 5-42 中,單擊“Control”按鈕,進行電源完整性仿真分析參數的設置,出現如圖 5-44 所示的“Power Integrity Control”參數設置界面。

在這個參數設置界面中,共有三個選項卡。

? “Standard”選項卡。主要用來設置兩個參數,一個是仿真分析的截止頻段 Corner Frequency,意為 PI 工具只在這個頻率范圍內進行電源完整性仿真分析。如果在這個頻段內能夠滿足阻抗要求,那么就達到設計目的。在超出了這個頻段,電源目標阻抗可以按照 Slope 所定義的斜率變化,實際的電源系統阻抗小于這個斜率,仍然認為是可以滿足設計要求的。另外一個參數就是前面已經提到過的,當所分析的電源 Shape 面積和整個 PCB 的面積比小于一定比例時,PI 工具忽略這個 Shape,不作為電源完整性的分析對象。

? “Simulation”選項卡。在這個界面中主要實現對電源網格建模的設置。按照上面對系統工作頻率所對應的波長的分析,結合當前 PCB 的實際尺寸,從仿真精度和速度兩方面考慮,來設置一個適合的網格尺寸。其中參數“Adaptive Level”是為了提高 PCB 設計中不規則形狀 Shape 的仿真精度而增加的變化因子,讀者可以參考“Allegro PCB PI User Guide.pdf”文件詳細了解該參數的使用方法。對于仿真結果,通常選擇“Frequency Domain Impedance Display”選項作為顯示方式。其他參數含義都比較清楚,在此不再贅述。

? “Mounted Inductance”選項卡。用來設置在多節點仿真中如何提取器件在 PCB 上安裝之后實際的引線電感。這也是多節點仿真中考慮器件實際物理位置的一個體現。由于該選項卡比較簡單,在圖 5-44 中沒有顯示此選項卡內容。

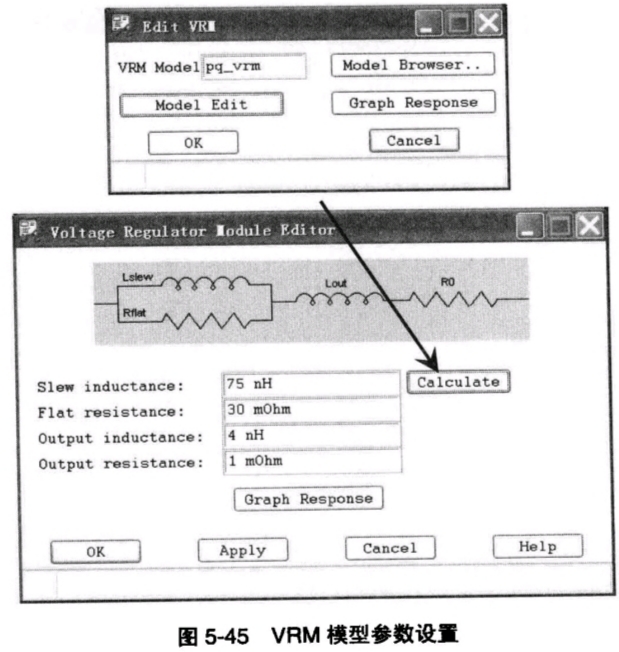

?接下來,為進行多節點分析,還需要加入電源模塊 VRM 模型和噪聲源,在 PI 的設計環境中,單擊鼠標右鍵選擇“Add VRM”和“Add Noise Source”這兩個功能命令即可,在 PCB 上選擇適當的位置,可加入相應的 VRM 和噪聲源。對 VRM 和噪聲源的參數修改可以通過直接在這些元素上單擊鼠標右鍵,選擇“Edit”命令(或者其他如“Move”、“Delete”等命令)。例如,選擇一個 VRM,選擇“Edit”命令之后,將打開圖 5-45 中上面的界面,在這個界面中,再單擊“Model Edit”按鈕,將打開圖下半部的模型參數設置界面。讀者在使用這個 VRM 模型時,需要對這幾個參數有所了解。

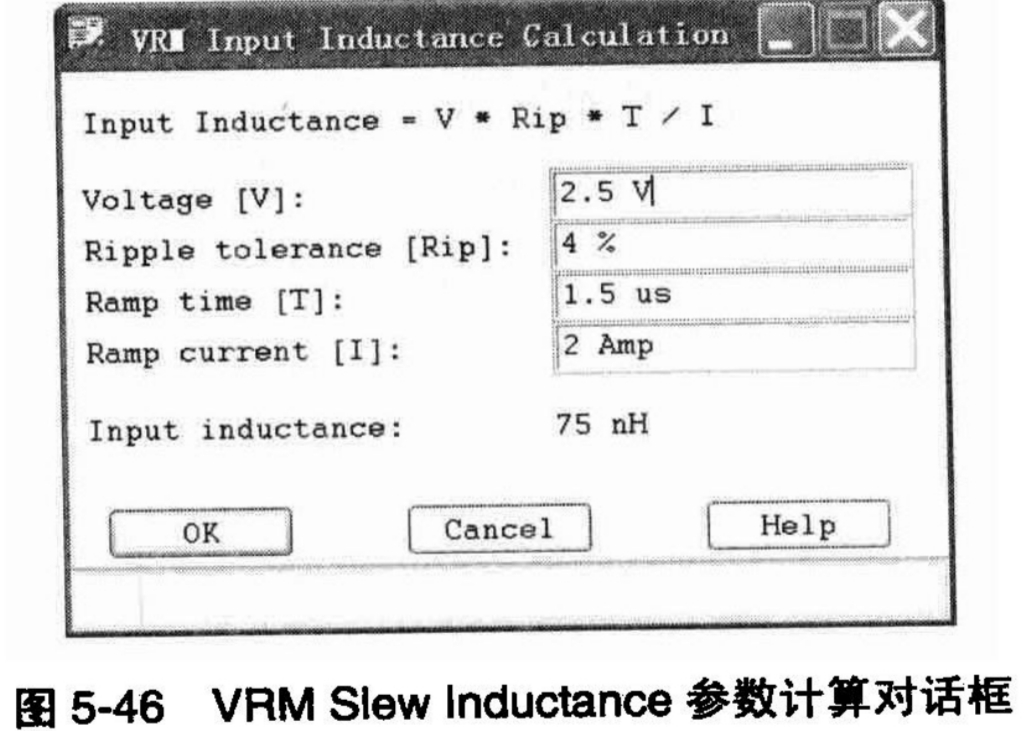

? Slew inductance,由于 VRM 對電流的相應能力,可以通過公式計算獲得。例如,單擊該參數右面的“Calculate”按鈕,將彈出如圖 5-46 所示的對該參數進行計算的對話框。在該 VRM 例子中供電電源為 2.5V,允許紋波為 4%,對電流的相應能力為 2A/1.5μs,這樣,可以得出 Slew inductance 為 75nH。

? Flat resistance,VRM 中電容的等效電阻。

? Output inductance,VRM 在安裝到 PCB 上后,和 PCB 連接的等效引線電感。

? Output resistance,VRM 在安裝到 PCB 上后,和負載之間連接的等效電阻。

這是 Cadence 的 PI 工具提供的簡單四元素 VRM 模型,讀者也可以根據自己的需求來建立 VRM 模型,并把模型加入到仿真庫中,從而在 PI 中使用用戶自定義的 VRM 模型。這個過程和在高速信號仿真中添加器件模型的過程是一樣的。

?以上是在電源仿真分析中加入 VRM 的介紹,對于噪聲源的使用方法和操作過程和 VRM 的相同,這里不再贅述。希望讀者參照 VRM 的使用,通過自己的練習,學習并掌握如何在仿真分析中加入和修改噪聲源。在完成這些參數和設計元素的設置以后,就可以使用多節點仿真進行電源系統的仿真分析了。

通過以上內容的學習,相信讀者應該已經很清楚,在疊層設計已經確定的情況下,進行電源完整性設計實際上就是電容的合理使用。而這個合理使用不僅僅是從電容的種類和數量上進行合理使用,電容在實際的 PCB 中的安裝和布線方式同樣對電源性能有很大的影響。因此在下面的章節中,我們將討論電容在 PCB 設計中關于布局和布線的問題。

5.10.4 電容的布局和布線

對于電容的布局,首先要提到的就是安裝距離。容值最小的電容,有最高的諧振頻率,去耦半徑最小,因此盡量放在最靠近芯片的位置;容值稍大些的可以距離稍遠,最外層放置容值最大的。但是,所有對該芯片去耦的電容都應盡量靠近芯片。在放置時,最好均勻分布在芯片的四周,對每一個容值等級都要這樣,必須對整個芯片所在區域均勻去耦。

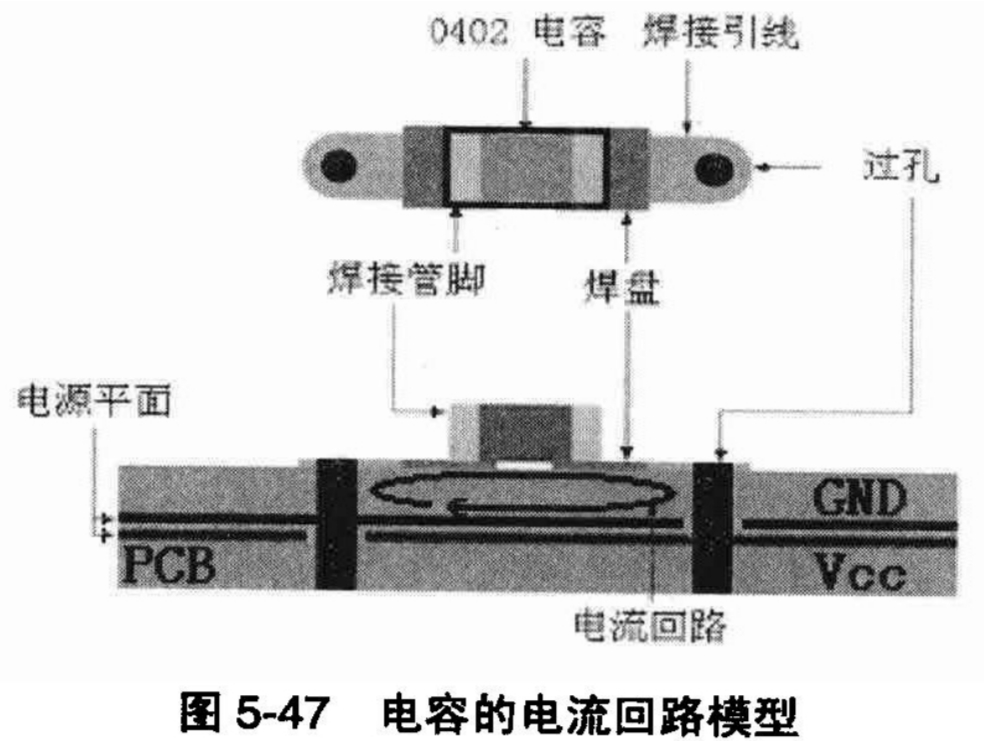

在安裝電容時,要從焊盤拉出一小段引出線,然后通過過孔和電源平面連接,接地端也是同樣。這樣流經電容的電流回路為:電源平面→過孔→焊接引出線→焊盤→電容→焊盤→引出線→過孔→地平面,圖 5-47 顯示了電流的回流路徑。

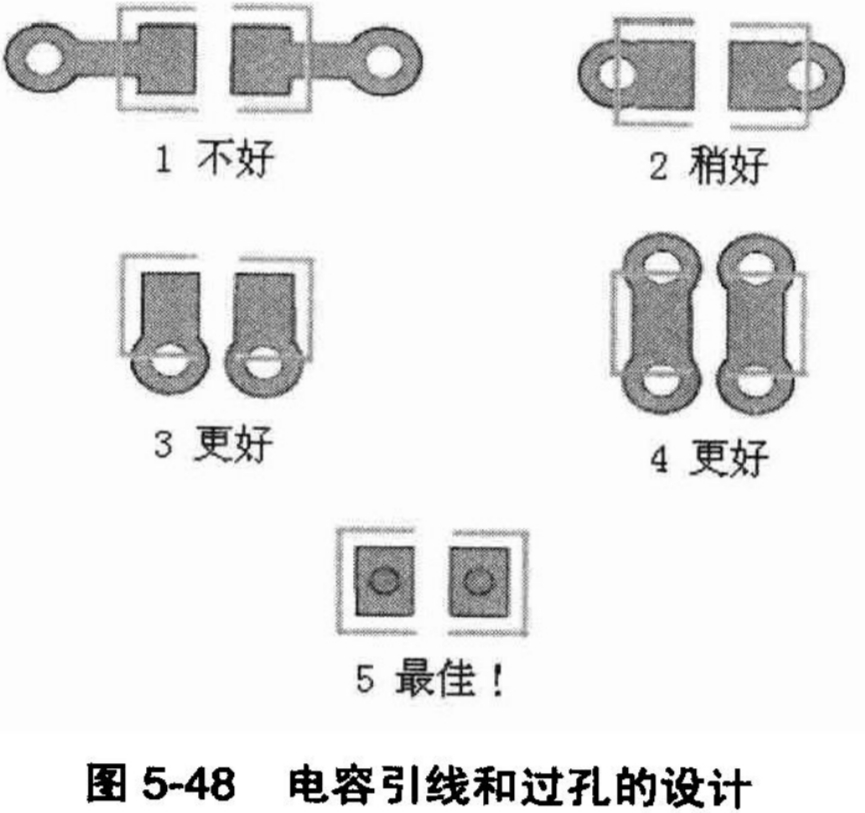

?在 PCB 的設計中,電容引線方式和過孔放置的基本原則就是讓這一環路面積最小,進而使總的寄生電感最小。圖 5-48 中顯示了幾種電容引線方式和過孔的放置方法。

?? 第一種方法從焊盤引出很長的引出線,然后連接過孔,這會引入很大的寄生電感,一定要避免這樣做,這是最差的電容安裝方式;

? 第二種方法在焊盤的兩個端點緊鄰焊盤打孔,比第一種方法的回流路徑面積小得多,寄生電感也較小,可以接受;

? 第三種方法在焊盤側面打孔,進一步減小了回路面積,寄生電感比第二種方法的更小,是比較好的方法;

? 第四種方法在焊盤兩側都打孔,和第三種方法相比,相當于電容每一端都是通過過孔的并聯接入電源平面和地平面,比第三種方法的寄生電感更小,只要空間允許,盡量用這種方法;

? 最后一種方法在焊盤上直接打孔,寄生電感最小,但是通常在焊接過程中可能會出現問題,是否使用這種方式要看加工和生產能力。

在實際設計中通常使用的是第三種和第四種布線和過孔設置方法。需要強調的是,有些工程師為了節省布線空間,有時讓多個電容使用公共的過孔。但任何情況下都不要這樣做,這樣做不僅會減弱電容的去耦能力,還可能由于過孔和引線的共用將不同的噪聲源耦合在一起,破壞電源完整性。

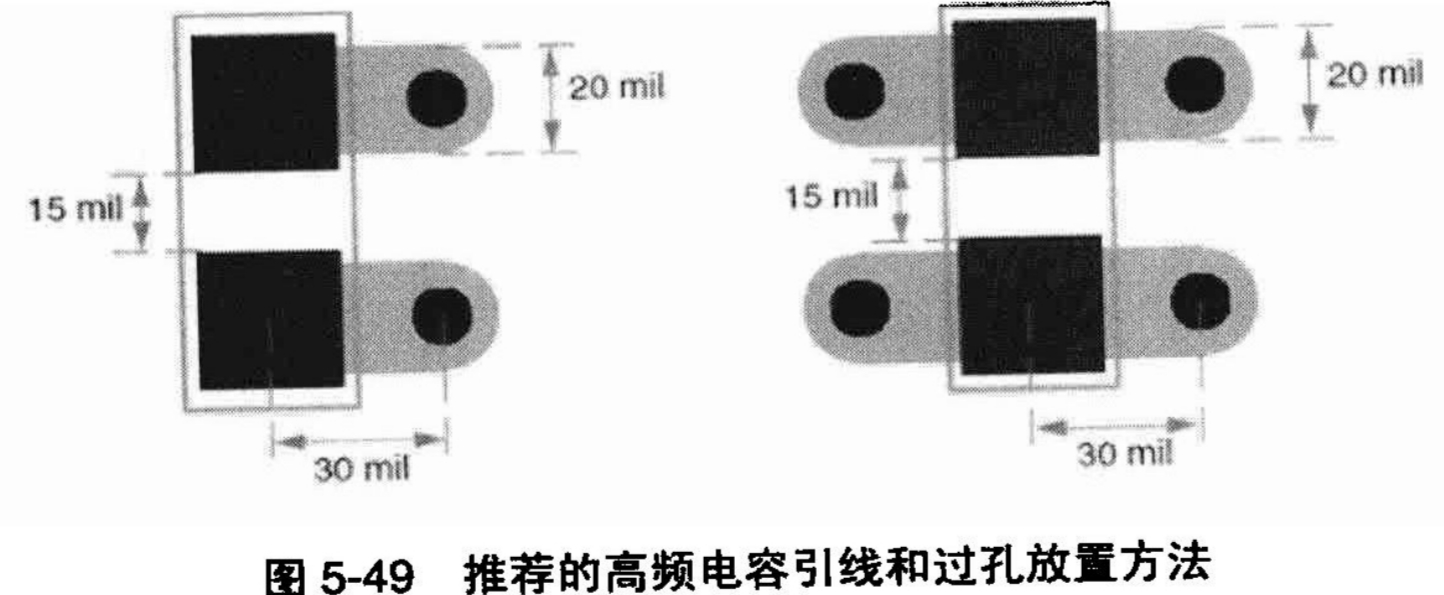

由于印制線越寬,電感越小,所以從焊盤到過孔的引出線要盡量加寬,如果可能,盡量和焊盤寬度相同。這樣即使是0402封裝的電容,也可以使用20mil 寬的引出線,過孔可以使用 20mil 或 12mil,16mil 或 8mil。0402 封裝的電容引出線和過孔安裝如圖 5-49 所示。

?5.10.5 合理認識電容的有效去耦半徑

對于電容的放置位置,幾乎所有的設計要求中都會提到電容布局要盡量靠近芯片,這已經成為所有人的共識。但是為什么要這樣做,有些資料從減小回路電感的角度來分析了這個問題。確實,減小回路電感是最直觀,也是最直接原因,這樣做是必需的。還有一些資料進一步從電容有效去耦半徑去分析,如果電容擺放離芯片過遠,超出了它的有效去耦半徑,電容將失去它的去耦作用,但是這些分析都不夠全面。在本節中,作者來談談如何從減小回路電感、電容去耦半徑、電容響應時間及補償電流強度幾個方面來綜合認識這個問題。

理解有效去耦半徑最好的辦法就是考察噪聲源和電容補償電流之間的相位關系。當芯片對電流的需求發生變化時,會在電源平面的一個很小的局部區域內產生電壓擾動,也即噪聲源,電容要補償這一電流(或電壓),就必須先感知到這個電壓擾動。信號在介質中傳播需要一定的時間,因此從噪聲源的電壓波動到電容感知到這一波動之前有一個時間延遲。同樣,電容所提供的補償電流到達擾動區域也需要一個延遲,因此必然造成噪聲源和電容補償電流之間的相位上的不一致。

特定的電容,對與它自身諧振頻率相同的噪聲補償效果最好,我們以這個頻率來衡量這種相位關系。設電容諧振頻率為f,對應波長為λ,有效補償電流表達式可寫為:

I=A·e^-j2πf2R/C

其中,A是電容能夠及時反應的電流幅度,R為需要補償的區域到電容的距離,C為信號傳播速度,I為到達噪聲源的補償電流強度。

當噪聲源到電容的距離達到四分之一波長時,補償電流的相位為π,和噪聲源相位剛好差 180°,即完全反相。此時補償電流不再起作用,去耦作用失效,補償的能量無法及時送達。為了能有效傳遞補償能量,應使噪聲源和補償電流的相位差盡可能得小,最好是同相位的。距離越近,相位差越小,補償能量傳遞越多,如果距離為 0,則補償能量百分之百傳遞到擾動區域。這就要求電容距離噪聲源盡可能得近,要遠小于λ/4。在實際應用中,按照經驗數據,這一距離最好控制在λ/50之內。

舉例說明,一個 0.01μF,0402 封裝的陶瓷電容,假設布線和安裝到電路板上后總的寄生電感(包括本體等效電感 ESL,引線電感,以及引線等效電感)為 1.5nH,那么其布線并安裝后的諧振頻率為:

f=1/2π√(1/L·C)=1/2π√(1/1.5x10^-9x0.01x10^-6)=41.1MHz

諧振頻率所對應的周期約為 24ns。假設信號在電路板上的傳播速度為 200ps/inch,則諧振頻率所對應的波長為 120inch。選取電容去耦半徑為 1/20050=2.4inch,大約等于 6cm。所以,本例中的電容只能對它周圍大約 6cm 范圍內的電源噪聲進行補償,即它的去耦半徑為 6cm。但是,對于 0.01μF 的電容,我們真的會按照 6cm 的去耦半徑來布局么?

稍有 Layout 工作經驗的工程師都知道,6cm 的有效去耦半徑是個比較大的范圍,如果按照這個距離去放置電容,那么設計非常容易,這樣的約束也失去了指導設計的意義。這是因為有效去耦半徑是從電容本身的性質出發而得出的結論,而我們研究電容有效去耦半徑的出發點是為了給噪聲源提供及時而充足的電流。

請讀者注意這里的兩個關鍵詞:及時和充足。如果真的按照 6cm 的距離來放置這個電容,那么對于噪聲源的反應延遲就是 0.48ns+0.48ns=0.96ns,即噪聲信號到達電容及電容送出補償電流的延遲疊加。這個補償延遲對于高速信號而言是不允許的,并且從公式(5.1)來看,隨著噪聲源和電容之間距離的加大,能夠達到噪聲源的有效電流強度按指數迅速衰減,而且隨著補償電流的釋放,電容本身的補償能力也會下降,實際能夠到達噪聲源的補償電流強度也會很低,這不是我們希望得到的結果。因此,綜合考慮有效去耦半徑、補償延遲和補償電流強度幾個方面,才有業界公認的結論:去耦電容離噪聲源越近越好!

不同類型的容值的電容,諧振頻率不同,去耦半徑也不同。對于大容量電容,因為其諧振頻率很低,對應的波長非常長,因而去耦半徑很大,這也是為什么通常不太關注大電容在電路板上的放置位置的原因。而對于小容量電容,因去耦半徑很小,應盡可能地靠近噪聲源,也就是需要去耦的芯片。

至此,我們完成了對電源完整性仿真分析工具使用的介紹。正如在本節開始時,作者曾經指出的,電源完整性仿真分析的任務是在有限的時間內,在一定的設計和生產成本控制范圍內,使用工程近似的方法,完成工程師所關心的設計目標。因此相對于科學性研究而言,電源完整性設計是一種定性分析,在一定條件下的“精確”仿真,引導工程師按照正確的設計方向來完成電源系統設計。基于這種理念,在 Cadence 的 PI 工具的使用過程中,不可避免地要使用很多“近似”參數及加入人為控制因素,例如,對于電源/地平面的建模,對 VRM 參數的設置,以及噪聲源的參數設置和布局等,都包含了很多“近似”和人為控制的因素,它不存在絕對的對與錯,只有合理和不合理之分。而且,讀者在閱讀 Cadence 軟件中的使用手冊和幫助文檔時,會常常遇到類似下面的語句:

Note:This value does not necessarily represent the actual switching current profile.It is used to help you validate the effectiveness of decoupling,not intended to obtain the actual voltage variation of the power supply.

這從軟件本身也說明了一些參數的設置并不需要非常精確的值,這些值僅僅是為了驗證或者得出一個大致的結論,所以只要這些值在一個合理的范圍內就能滿足要求。但是讀者也必須要清醒地認識到,在能力所及的范圍內,盡量獲得準確的參數值,能夠盡快使電源完整性仿真設計收斂,縮短設計周期,提高設計效率。而如何從大量的數據中獲得相對精確的參數估計,需要讀者從實踐中不斷總結,通過對比仿真分析和實驗測量的數據,對模型和參數進行校正和求精,加深對工具的理解,這樣才能逐步提高對工具的掌控能力。

5.11 SSN 的設計分析

讀者會注意到,盡管在 Cadence 的后仿真分析功能界面中,有 SSN 分析這一項,如圖 5-35 所示,但是作者并沒有提及如何去做此項功能的分析和驗證。其原因我們在第 3 章中已經講過,SSN 更多的是芯片內部的電源完整性問題,對于板級系統設計人員來說,我們基本上沒有任何機會或者能力來做所謂的優化設計。事實上,做好板級電源系統的優化,也就是在改善系統的 SSN 性能。

對于一個常用的、具有固定功能的芯片而言,比如我們這個設計中所使用的 DDR 存儲芯片,SSN 主要是依靠芯片廠商在芯片制造過程中所能提供的性能保證。在板級應用系統中,我們只能盡量提供良好的外部工作環境,以期望能夠實現該芯片應有的性能。然而,也有一個例外,那就是如果芯片的功能能夠依據用戶的功能而動態改變,這個時候用戶就應該關注由于功能的動態改變而帶來的芯片內部 SSN 性能的變化。比如我們設計中所使用的 FPGA 芯片,它的功能是可以被用戶重新定義的,隨著功能的改變,其芯片的內部電路結構也會發生改變,因此在不同的功能和電路結構下,芯片的 SSN 性能也會不同。但這種對 SSN 性能的關注,并不應該在系統設計后期由仿真分析功能實現,而在系統需求和功能定義的早期,就應該仔細考慮此類芯片的 SSN 性能設計需求。

在 FPGA 的設計廠商也充分認識到了這一點,因此在系統設計初期,FPGA 的廠商都會提供關于某款 FPGA 芯片的 SSN 性能設計指導。比如,我們這個設計中所使用的 XC2VP30-6FF1152C 芯片,Xilinx 提供了相應的指導文件“XAPP669,Managing Ground Bounce in Large FPGAs.pdf”,這個文件可以從 Xilinx 的網站上獲得,也可以從網上下載的資料中找到。在這個文件中,Xilinx 要求 FPGA 的用戶按照自己的系統性能需求,對 I/O 的管腳分配和使用模式進行統計分析,并依據 Xilinx 所提供的算法進行驗證。如果能夠通過驗證,那么 FPGA 的 SSN 性能就可以得到保證,否則就需要用戶去調整管腳分配使用模式。該讀者自行去學習這個應用文件,以及如何保證 Xilinx FPGA 的 SSN 性能的方法。

因此,盡管 SSN 在高速設計領域是個“炒”得很熱的話題,但是,一般來講,對于系統設計工程師而言,SSN 設計的方法學可以總結如下:如果系統設計中使用的全都是固定功能的芯片,那么基本上沒有必要去考慮某個芯片的 SSN 問題。與其花時間研究某個芯片的 SSN 性能,還不如做好整個電源系統的優化。但是,如果系統設計中使用了類似 FPGA 這樣的可變功能的芯片,那么就需要特別注意芯片廠商所提供的設計指導,甚至一些輔助分析工具,以驗證該芯片的 SSN 性能是否能夠適應本系統的設計需求。

5.12 小結

在本章中,我們詳細介紹了 Cadence 的高速設計流程,以及相應工具的使用方法。希望讀者注意的是,作者多次提到,由于 Cadence 的工具功能非常豐富,工具中所涉及的參數種類繁多,功能選項也非常多,在本文中沒有對軟件功能、參數和選項一一翻譯介紹(事實上,在沒有 Cadence 公司授權的情況下,對 Cadence 公司所屬的軟件產品進行翻譯并作為商品出版是侵犯版權的行為)。作者盡可能地從實用角度出發,介紹高速系統的設計理念和功能流程,使讀者在使用軟件進行實際設計操作之前,從方法學的角度理解和掌握 Cadence 高速電路設計系統和使用方法。對具體的軟件操作,功能使用及參數的設置,需要讀者結合自己的實際工作在實踐中進行學習和掌握。

為鞏固學習成果,讓讀者真正掌握如何用 Cadence 進行高速系統分析和設計,在下一章中,我們用一個實際的項目作為例子,一步一步帶領讀者完成 Cadence 高速設計的所有步驟,解決在設計中所遇到的各種問題,直至設計出一個實用的產品。

)

)

尋路)