做電路設計,需要提前用理想模型如VerilogA模型做驗證。這里分享一個由ahdlib庫里單端opamp改造而來的差分opamp。參考何樂年的《模擬集成電路設計與仿真》10.4節423頁;

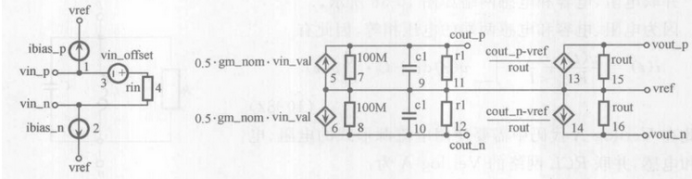

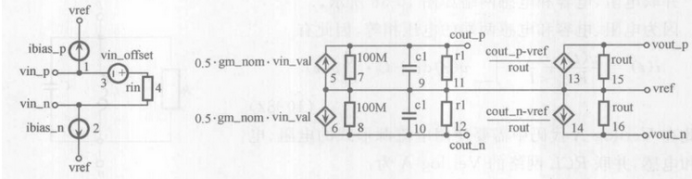

描述的小信號模型如上。

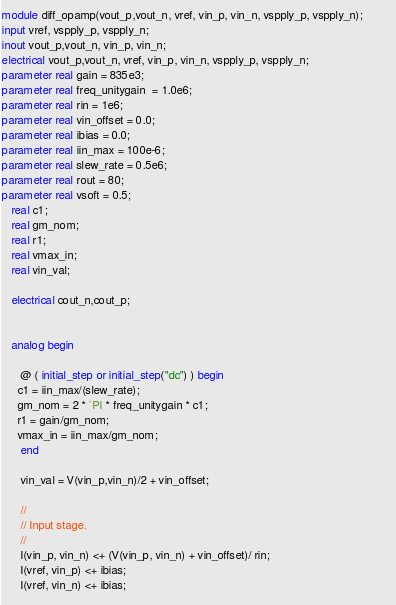

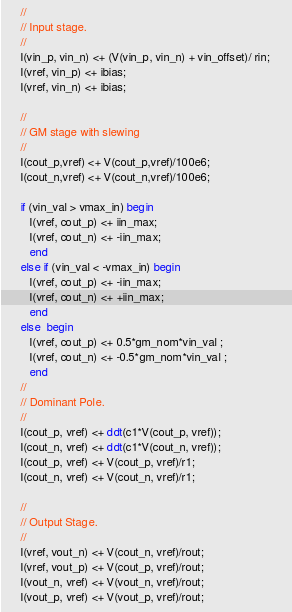

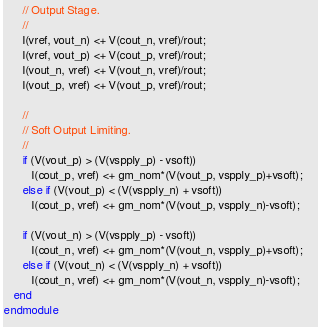

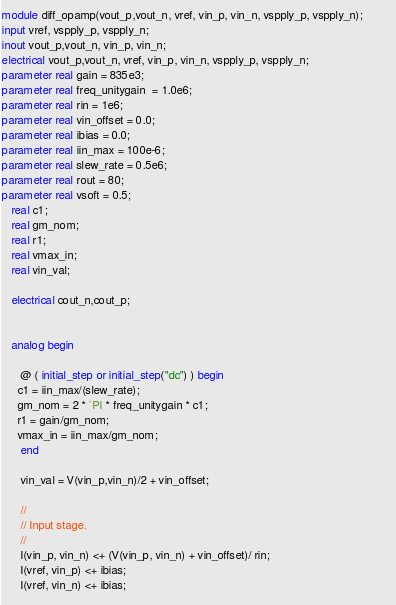

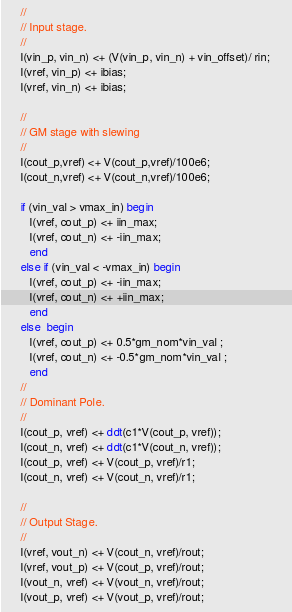

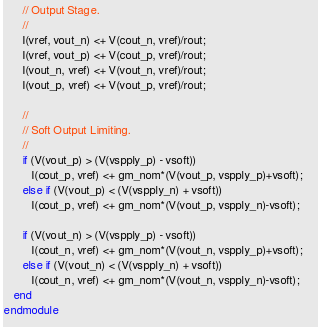

VerilogA 用到了SR=I/C,GBW=gm/C,gain=gm*r1等概念。加了內部節點cout_p,coutn作為描述對象,很巧妙。

做電路設計,需要提前用理想模型如VerilogA模型做驗證。這里分享一個由ahdlib庫里單端opamp改造而來的差分opamp。參考何樂年的《模擬集成電路設計與仿真》10.4節423頁;

描述的小信號模型如上。

VerilogA 用到了SR=I/C,GBW=gm/C,gain=gm*r1等概念。加了內部節點cout_p,coutn作為描述對象,很巧妙。

本文來自互聯網用戶投稿,該文觀點僅代表作者本人,不代表本站立場。本站僅提供信息存儲空間服務,不擁有所有權,不承擔相關法律責任。 如若轉載,請注明出處:http://www.pswp.cn/pingmian/79938.shtml 繁體地址,請注明出處:http://hk.pswp.cn/pingmian/79938.shtml 英文地址,請注明出處:http://en.pswp.cn/pingmian/79938.shtml

如若內容造成侵權/違法違規/事實不符,請聯系多彩編程網進行投訴反饋email:809451989@qq.com,一經查實,立即刪除!