- 對應于原文 Multichannel Buffered Serial Port (McBSP)的 2.5.3 Data Clock Generation。

CLKG

-

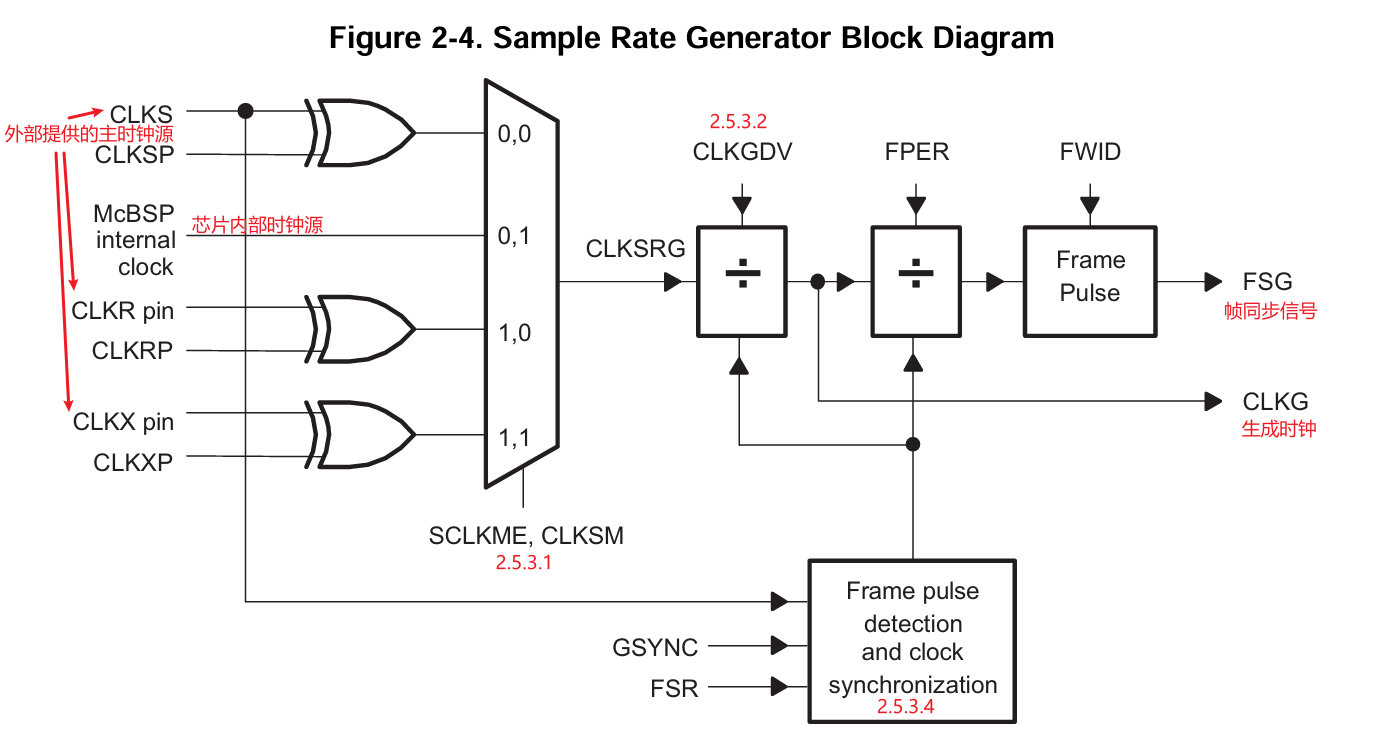

Figure 2-4. Sample Rate Generator Block Diagram

-

CLKG 是采樣率發生器輸出的數據位時鐘(Data Bit Clock),它被用來控制:

- 數據發送/接收的時鐘節奏(即每個數據位在哪個時鐘邊沿傳輸)

- 幀同步信號 FSG 的生成時機

- CLKG 是通過對 CLKS 進行分頻得到的,具體分頻系數由寄存器 CLKGDV 控制。

2.5.3 Data Clock Generation

-

當接收/發送時鐘模式設置為 1(即在引腳控制寄存器(PCR)中設置

CLK(R/X)M = 1)時,數據時鐘(CLK(R/X))將由內部采樣率發生器輸出的時鐘 CLKG 驅動。你可以為接收器和發送器選擇多種數據位時鐘源,包括: -

采樣率發生器的輸入時鐘可以是內部時鐘源,也可以是通過 CLKX、CLKR 或 CLKS 引腳 輸入的專用外部時鐘源。

在芯片內部,McBSP 的時鐘源可通過配置系統配置模塊中的 CFGCHIP3 寄存器 中的 ASYNC3_CLKSRC 位 來選擇為 PLL0_SYSCLK2 或 PLL1_SYSCLK2。有關 McBSP 內部時鐘源的詳細信息,請參見 第 2.5.3.1 節。 -

上段提到的采樣率發生器的輸入時鐘源(無論是內部時鐘源還是專用外部時鐘源),都可以通過一個可編程分頻值(采樣率發生器寄存器(SRGR)中的

CLKGDV位)進行分頻,以驅動 CLKG。 -

無論采樣率發生器使用哪種時鐘源,CLKSRG 的上升沿(見圖 2-4)都會用于生成 CLKG 和 FSG。

2.5.3.1 Input Clock Source Mode: CLKSM and SCLKME 時鐘源的選擇

-

采樣率發生器的輸入時鐘信號可以從四種可選的時鐘源中選擇,這些時鐘源由 引腳控制寄存器(PCR)中的 SCLKME 位 和 采樣率發生器寄存器(SRGR)中的 CLKSM 位 共同決定,詳見 表 2-2。

-

表 2-2:使用

SCLKME和CLKSM位選擇采樣率發生器的輸入時鐘

| PCR 寄存器中的 SCLKME 位 | SRGR 寄存器中的 CLKSM 位 | 采樣率發生器的輸入時鐘源 |

|---|---|---|

| 0 | 0 | CLKS 引腳上的外部輸入時鐘McBSP |

| 0 | 1 | 內部輸入時鐘(通常為 LSPCLK) |

| 1 | 0 | CLKR 引腳上的外部輸入時鐘 |

| 1 | 1 | CLKX 引腳上的外部輸入時鐘 |

- 各時鐘源解釋:

| 輸入時鐘源 | 描述 |

|---|---|

| McBSP 內部輸入時鐘 | 通常是系統低速外設時鐘(LSPCLK),即 DSP 主頻的四分之一(SYSCLKOUT / 4)。這是最常用的主模式配置。 |

| CLKS 引腳上的外部輸入時鐘 | 來自 CLKS 引腳的外部時鐘信號,可用于同步到其他系統的主時鐘。 |

| CLKX 引腳上的外部輸入時鐘 | 使用發送時鐘引腳 CLKX 上的外部時鐘作為采樣率發生器的輸入。 |

| CLKR 引腳上的外部輸入時鐘 | 使用接收時鐘引腳 CLKR 上的外部時鐘作為采樣率發生器的輸入。 |

2.5.3.2 Sample Rate Generator Data Bit Clock Rate: CLKGDV 頻率

-

第一個分頻階段從輸入時鐘生成串行數據位時鐘。該分頻階段使用一個計數器,該計數器由采樣率發生器寄存器(SRGR)中的 CLKGDV 位預加載,并包含分頻比值。該階段的輸出是數據位時鐘,它通過采樣率發生器的輸出 CLKG 輸出,并作為第二和第三分頻階段的輸入。

-

CLKG 的頻率等于采樣率發生器輸入時鐘頻率的 1/(CLKGDV + 1)。因此,采樣率發生器的輸入時鐘頻率被分頻了 1 到 256 之間的某個值。所選擇的 CLKGDV 值 必須確保生成的時鐘滿足設備數據手冊中規定的時序要求和限制條件。

-

當 CLKGDV 的值為奇數或等于 0 時,生成的 CLKG 時鐘占空比為 50%。請注意:如果 CLKGDV 是奇數,表示對源時鐘進行了偶數分頻;如果 CLKGDV 是偶數(設為 2p),則表示對源時鐘進行了奇數分頻,此時高電平持續時間為 p + 1 個周期,低電平持續時間為 p 個周期。這一點在 示例 2-1、示例 2-2 和 示例 2-3 中有詳細說明。

-

這里省略示例

2.5.3.3 Bit Clock Polarity: CLKSP 觸發邊沿的類型

- 通過在采樣率發生器寄存器(SRGR)中設置 CLKSM = 0,并在引腳控制寄存器(PCR)中設置 SCLKME = 0,可以選擇使用**外部時鐘(CLKS)**來驅動采樣率發生器的時鐘分頻器。在這種情況下,SRGR 寄存器中的 CLKSP 位 用于選擇在 CLKS 的哪一個邊沿 上生成采樣率發生器的數據位時鐘(CLKG)和幀同步信號(FSG)。由于 CLKG 和 FSG 是在 CLKSRG 的上升沿 生成的,因此:

當 CLKSP = 0 時,CLKS 的上升沿 會觸發 CLKG 和 FSG 的跳變;

當 CLKSP = 1 時,CLKS 的下降沿 會觸發 CLKG 和 FSG 的跳變。

2.5.3.4 Bit Clock and Frame Synchronization 決定是否讓 CLKG 和幀同步信號 FSG 與外部幀同步信號(如 FSR)保持相位同步

-

當選擇使用外部時鐘 CLKS 來驅動采樣率發生器(即在 SRGR 寄存器中設置 CLKSM = 0,并在 PCR 寄存器中設置 SCLKME = 0)時,SRGR 寄存器中的 GSYNC 位 可用于配置 CLKG 相對于 CLKS 的時序關系。

- 當 GSYNC = 1:

- 啟用全局同步模式。每次接收到外部幀同步信號(FSR)的上升沿(或下降沿,取決于極性設置)時,會觸發 CLKG 和 FSG 的重新對齊。 確保 McBSP 與外部設備(如音頻編解碼器)之間保持精確的時序同步。

- CLKG 在同步后總是從高電平開始。此時,FPER(幀周期)寄存器的值不再起作用,因為幀周期由外部幀同步脈沖決定。

- 當 GSYNC = 0:

- 關閉全局同步。CLKG 自由運行,不受外部幀同步信號的影響。

- 使用內部設定的 FPER 和 FWID 來生成幀同步信號 FSG。

- 當 GSYNC = 1:

-

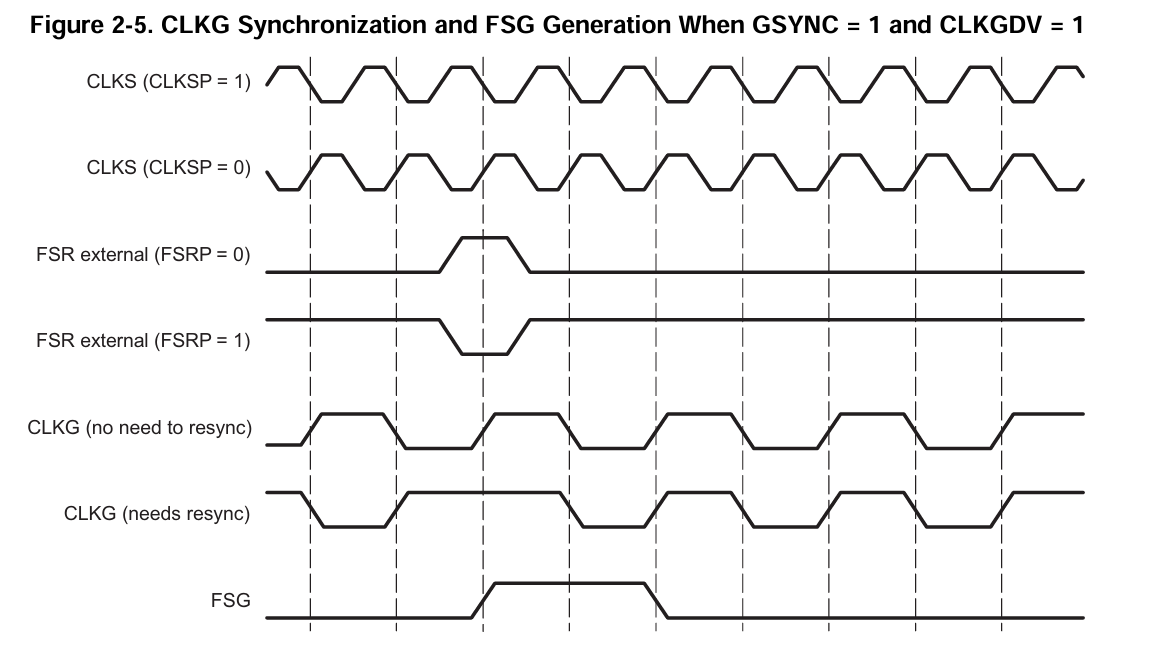

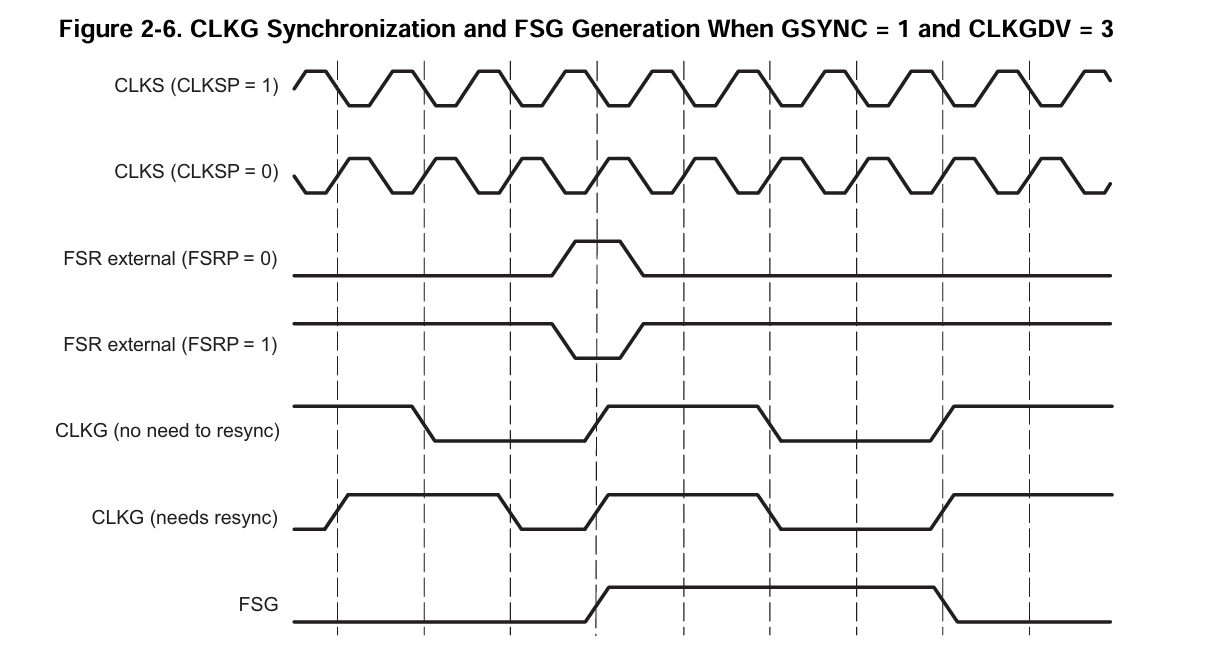

圖 2-5 和 圖 2-6 展示了在不同 CLKS 和 FSR 極性 配置下的這種操作行為。這些圖中假設 FWID = 0,即生成的幀同步信號 FSG 的寬度為 1 個 CLKG 周期。

-

這些圖展示了當 CLKG 初始時與幀同步信號同步且 GSYNC = 1 的情況下,以及當 CLKG 與幀同步信號不同步但 GSYNC = 1 時,CLKG 的變化情況。

-

Figure 2-5. CLKG Synchronization and FSG Generation When GSYNC = 1 and CLKGDV = 1

-

下面的三個小標題是對圖中元素的說明:

FSRP 的作用

-

FSRP(Frame Sync Rising Edge Polarity)

是 McBSP 寄存器中的一個配置位,用于設置外部幀同步信號 FSR(接收幀同步)的觸發邊沿類型。 -

FSR(Frame Sync Receive)

是 McBSP 接收端的幀同步輸入引腳。該引腳接收來自外部設備的幀同步信號,用來標識一幀數據的開始。

| FSRP 值 | 觸發邊沿 | 含義說明 |

|---|---|---|

0 | 上升沿(Rising Edge) | 當 FSR 引腳上出現一個從低到高的跳變時,表示新的一幀開始,并觸發同步機制 |

1 | 下降沿(Falling Edge) | 當 FSR 引腳上出現一個從高到低的跳變時,表示新的一幀開始,并觸發同步機制 |

CLKG 狀態

| 項目 | CLKG (no need to resync) | CLKG (needs resync) |

|---|---|---|

| 中文含義 | 不需要重新同步的 CLKG | 需要重新同步的 CLKG |

| 描述 | CLKG 已與外部幀同步信號(如 FSR)對齊 | CLKG 尚未與幀同步信號對齊 |

| 狀態說明 | 當前處于同步模式下,數據傳輸穩定 | 處于等待同步狀態,尚未完成首次同步或同步丟失 |

| 行為變化 | CLKG 按照當前相位繼續運行 | CLKG 將被重新對齊,從高電平開始一個新的周期 |

FSG 的作用

-

FSG 是 Frame Sync Generator(幀同步發生器)的縮寫,是 McBSP(多通道緩沖串行端口)模塊中的一個內部信號,用于生成幀同步脈沖,標識一幀數據的開始。

-

在串行通信中(如音頻、TDM 等),數據通常以“幀”為單位進行傳輸。每一幀包含多個數據位(如 16bit 或 32bit),幀同步信號用來告訴接收方:“新的一幀開始了”。

-

Figure 2-6. CLKG Synchronization and FSG Generation When GSYNC = 1 and CLKGDV = 3

-

當 GSYNC = 1 時,只要滿足以下條件,發送器就可以與接收器同步工作:

- FSX 被配置為由采樣率發生器的幀同步信號 FSG 驅動(即在 SRGR 寄存器中設置 FSGM = 1,并在 PCR 寄存器中設置 FSXM = 1)。

- 采樣率發生器的時鐘 應該驅動發送和接收的數據位時鐘(即在 SPCR 寄存器中設置 CLK(R/X)M = 1)。因此,CLK(R/X) 引腳不應由其他任何時鐘源驅動。

2.5.3.5 Digital Loopback Mode: DLB

- 略

2.5.3.6 Receive Clock Selection: DLB, CLKRM

-

表 2-3 展示了串口控制寄存器(SPCR)中的數字回環位(DLB)和引腳控制寄存器(PCR)中的 CLKRM 位如何共同決定接收器所使用的時鐘來源。當 數字回環模式(DLB = 1) 啟用時,發射器的時鐘會驅動接收器。CLKRM 位用于決定 CLKR 引腳是作為輸入還是輸出使用。

-

表 2-3. 接收時鐘選擇(Receive Clock Selection)

| SPCR 中的 DLB 位 | PCR 中的 CLKRM 位 | 接收時鐘來源 | CLKR 引腳功能 |

|---|---|---|---|

| 0 | 0 | CLKR 作為外部輸入時鐘,經過 CLKRP 控制反相處理后用于接收 | 輸入。由外部驅動 |

| 0 | 1 | 采樣率發生器時鐘(CLKG)驅動 CLKR | 輸出。由 CLKG 驅動,并根據 CLKRP 設置是否反相后輸出 |

| 1 | 0 | 內部發送時鐘(CLKX_int)驅動內部接收時鐘(CLKR_int),并根據 CLKRP 設置是否反相 | 高阻抗 |

| 1 | 1 | CLKX_int 驅動 CLKR_int,并根據 CLKRP 設置是否反相 | 輸出。CLKR(與 CLKX 相同)在輸出前根據 CLKRP 設置被反相。 |

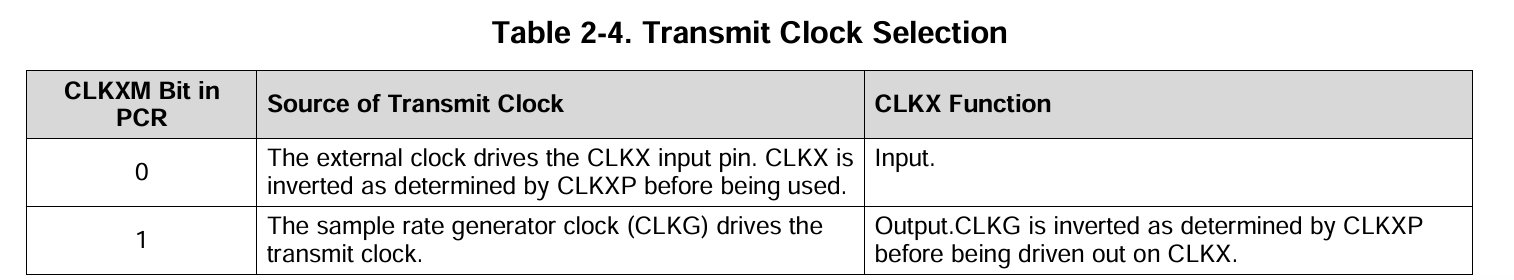

2.5.3.7 Transmit Clock Selection: CLKXM

- 表 2-4 顯示了引腳控制寄存器(PCR)中的 CLKXM 位如何選擇發送時鐘(transmit clock),以及 CLKX 引腳是作為輸入還是輸出使用。

2.5.3.8 Stopping Clocks

- 略

ChatGPT Plus充值教程與實用指南:附國內外使用案例與模型排行)

![[Java惡補day8] 3. 無重復字符的最長子串](http://pic.xiahunao.cn/[Java惡補day8] 3. 無重復字符的最長子串)

)

)

Java/python/JavaScript/C/C++/GO最佳實現)