相關閱讀

Spyglass![]() https://blog.csdn.net/weixin_45791458/category_12828934.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12828934.html?spm=1001.2014.3001.5482

預備知識

? ? ? ? 為了方便檢查,Spyglass向用戶提供Guideware作為檢查參考;Guideware又包含各種方法(Methodology),應用于設計的不同階段,比如initial_rtl、rtl_handoff和netlist_handoff方法;方法又包含各種子方法(Sub-Methodology),應用于不同方面的檢查,比如lint、adv_lint、cdc、rdc、power子方法;子方法又包含各種目標(Goal),應用于不同步驟的檢查,比如lint_rtl、lint_rtl_enhanced、lint_turbo_rtl、lint_functional_rtl、lint_abstract目標,目標是每次run_goal命令的執行對象,檢查結果也按照目標進行分組;目標又包含各種規則(Rule),規則是檢查的最小單位,每個規則代表了一個特定檢查,每個規則擁有自己的嚴重性類別和嚴重性標簽,嚴重性類別有四種(FATAL、ERROR、WARNING、INFO),而嚴重性標簽除了有預設的五種(Fatal、Error、Warning、Info、Data)外還可以使用define_severity目標選項自定義,每個嚴重性標簽屬于一個嚴重性類別。策略(Policy)或產品指的是規則發布時的集合,比如lint、morelint、openmore、starc、starc2002、starc2005、clock-reset策略,有時候一個目標由來自不同策略的規則組成。

目標文件

? ? ? ? 目標的詳細信息保存在一個.spq后綴的文本文件中,它所在的路徑如下所示。

/opt/Synopsys/spyglass/W-2024.09-SP1/SPYGLASS_HOME/GuideWare/2024.09/block/rtl_handoff/lint/lint_rtl.spq? ? ? ? 目標文件可以包含以下內容:

- 注釋

- 描述信息(=template)

- 策略注冊(-policies)

- 規則設置(-rules/-addrules/-ignorerules/-overloadrules)

- 參數默認值覆蓋(-parameter)

- 定義嚴重性標簽(-define_severity)

? ? ? ? 下面展示了lint_rtl目標文件。

// ----------------------------------------------------------------------------

// SpyGlass Methodology2.0 Goal File

//

// Goal Name : lint_rtl

// Version: 5.6.0

//

// Revision History:

// Ver Date SG Ver Comments

// 1.0.0 18-Feb-2013 5.0 Initial version

// 1.1.0 31-May-2013 5.1 Severity of following rules changed to Data:

// PragmaComments-ML

// ReportPortInfo-ML

// RegInputOutput-ML

// 2.0.0 30-May-2014 5.3 Guidware 2.0 Content Consistency

// 2.1.0 30-Sep-2014 5.4 Removed rule ArrayEnumIndex

// 5.4.1 26-Feb-2015 5.4.1 Added enable_fast_traversal switch for better performance of synthesis based rules.

//

// 5.6.0 18-Nov-2015 5.6 Added Following Rules

// Rule Name Policy GW Type

// ===============================================

// STARC05-2.10.1.4a starc2005 MUST

// STARC05-2.10.1.4b starc2005 MUST

// W156 lint MUST

// STARC05-2.3.3.1 starc2005 MUST

// W415a lint OPTIONAL

// W287b lint OPTIONAL

// W224 lint OPTIONAL

// W287a lint OPTIONAL

// W528 lint OPTIONAL

// mixedsenselist lint OPTIONAL

// W339a lint OPTIONAL

// STARC05-2.10.3.2a starc2005 OPTIONAL

// Removed Following Rules

// Rule Name Policy GW Type

// ===============================================

// DuplicateCaseLabel-ML morelint MUST

// STARC05-2.3.4.2 starc2005 OPTIONAL

//

// 2018.09 10-Sep-2018 2018.09 Added Following Rules

// Rule Name Policy GW Type

// ===============================================

// NoFeedThrus-ML morelint MUST

// STARC05-2.8.3.3 starc2005 MUST

// UndrivenOutTermNLoaded-ML morelint MUST

// UndrivenOutPort-ML morelint MUST

// W146 lint MUST

// W188 lint MUST

// W401 lint MUST

// W402b lint MUST

// W468 lint MUST

// W527 lint MUST

// W576 lint MUST

// CheckShiftOperator-ML morelint OPTIONAL

// HangingInstOutput-ML morelint OPTIONAL

// ResetFlop-ML morelint OPTIONAL

// SelfDeterminedExpr-ML morelint OPTIONAL

// UndrivenNet-ML morelint OPTIONAL

// UnrecSynthDir-ML morelint OPTIONAL

//

// 2019.06 10-June-2019 2019.06 Added Following Rules

// Rule Name Policy GW Type

// ===============================================

// STARC05-2.8.1.4 starc2005 MUST

// AlwaysFalseTrueCond-ML morelint OPTIONAL

// ClockEnableRace timing OPTIONAL

// ConstantInput-ML morelint OPTIONAL

// IfWithoutElse-ML morelint OPTIONAL

// NoExprInPort-ML morelint OPTIONAL

// RedundantLogicalOp-ML morelint OPTIONAL

// STARC05-2.10.7.1 starc2005 OPTIONAL

// STARC05-2.2.2.3a starc2005 OPTIONAL

// STARC05-2.7.2.2 starc2005 OPTIONAL

// STARC05-2.1.3.2 starc2005 OPTIONAL

// STARC05-2.1.3.4 starc2005 OPTIONAL

// STARC05-2.4.1.3 starc2005 OPTIONAL

// STARC05-2.8.1.5 starc2005 OPTIONAL

// STARC05-2.9.1.2b starc2005 OPTIONAL

// STARC05-2.9.1.2c starc2005 OPTIONAL

// UnConstrLoop-ML morelint OPTIONAL

// UnpackedStructUsed-ML morelint OPTIONAL

// W143 lint OPTIONAL

// W154 lint OPTIONAL

// W17 lint OPTIONAL

// W171 lint OPTIONAL

// W242 lint OPTIONAL

// Removed Following Rules

// Rule Name Policy GW Type

// ===============================================

// W71 lint MUST

//

// 2019.06-SP1 20-August-2019 2019.06-SP1 Added Following Rules

// DC Compatible Rule List

// =======================

// Rule Name Policy GW Type

// ===============================================

// ComplexModport-ML morelint MUST

// ConcatUnsizedNumbers-ML morelint MUST

// SelfGatingRegister-ML morelint MUST

// UniqueIfMissingCond-ML morelint MUST

// UseParamWidthInOverriding-ML morelint MUST

//

// Rule Name Policy GW Type

// ===============================================

// InterfaceWithoutModport-ML morelint MUST

// TwoStateData-ML morelint MUST

// TypedefNameConflict-ML morelint MUST

// DuplicateCaseLabel-ML morelint MUST

// HangingInstInput-ML morelint MUST

// NoStrengthInput-ML morelint MUST

// SensListRepeat-ML morelint MUST

// W295 lint MUST

// W346 lint MUST

// W479 lint MUST

// ReserveNameSystemVerilog-ML morelint OPTIONAL

// SVConstruct-ML morelint OPTIONAL

// UseSVAlways-ML morelint OPTIONAL

// UseSVCasting-ML morelint OPTIONAL

// DefaultState openmore OPTIONAL

// infiniteloop openmore OPTIONAL

// STARC05-2.9.1.2e starc2005 OPTIONAL

// NoGenLabel-ML morelint OPTIONAL

// UniqueCase-ML morelint OPTIONAL

// W167 lint OPTIONAL

// W187 lint OPTIONAL

// W345 lint OPTIONAL

// W489 lint OPTIONAL

// W504 lint OPTIONAL// Copyright Atrenta Inc, 2015. All rights reserved.

// ----------------------------------------------------------------------------=template+++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++

lint_rtl

*

Checks the design for basic Connectivity issues

Checks the design for basic Simulation issues

Checks the design for recommended design practices and Structural issues

Checks the design for basic Synthesis issues*

This goal checks basic connectivity issues in the design, such as floating

input, width mismatch, etc. These checks should be run after every change in

RTL code prior to code check-in.

This goal checks simulation issues in the design, such as- incomplete sensitivity list- incorrect use of blocking/ non-blocking assignments- potential functional errors- possible simulation hang cases, and- simulation race cases

These checks should be run, and reported messages should be reviewed prior to

all simulation runs.

This goal identifies the structural issues in the design that affect the

post-implementation functionality or performance of the design. Examples include

multiple drivers, high fan-in mux, and synchronous/asynchronous use of resets.

These checks should be run once every week and before handoff to implementation.

This goal reports unsynthesizable constructs in the design and code which can

cause RTL vs. gate simulation mismatch. These checks should be run twice a week,

and before handoff to synthesis team.=cut+++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++//------------------------------------------------

// Policy Registration

//-------------------------------------------------policy=openmore,starc,starc2005,erc,simulation,lint,latch,spyglass,morelint,timing//------------------------------------------------

// General Setup commands

//------------------------------------------------

-enable_fast_traversal//------------------------------------------------

// Policy Specific Parameter Setting

//-------------------------------------------------strict=W342,W343 // Rules will do strict checking

-new_flow_width='yes' // Enable all nex fixes made in width rules

-nocheckoverflow='no' // Width will be calculated as per the natural width of the expression.

-report_inferred_cell="yes" // if parameter set to "yes" then rules will flag for only inferred flops and not for instantiated flops.//------------------------------------------------

// Rule Registration

//------------------------------------------------//-rules AllocExpr // Allocator expression may not be synthesizable-rules badimplicitSM1 // Unsynthesizable modeling style for a sequential logic. Clock and reset cannot be inferred-rules badimplicitSM2 // Unsynthesizable implicit sequential logic: states can only be updated on same clock phase-rules badimplicitSM4 // Unsynthesizable implicit sequential logic: event control expression may not have more than one edge-rules BlockHeader // PORT/GENERIC used in block statement header may be unsynthesizable-rules bothedges // Both edges of the same variable are not allowed in the event control list//-rules DisconnSpec // Disconnect specification is ignored by synthesis tools.//-rules ForLoopWait // WAIT statements used inside a FOR-loop may be unsynthesizable//-rules IncompleteType // Incomplete type declaration may not be synthesizable//-rules Info_Case_Analysis // Highlights case-analysis settings//-rules IntGeneric // Non-integer type used in the declaration of a generic may be unsynthesizable//-rules LinkagePort // Linkage port may not be synthesizable//-rules LoopBound // For loop range bounds should either be locally static or globally static

//-rules NoTimeOut // Timeout expression in wait statement may not be synthesizable//-rules PortType // Port of unconstrained type detected. This may not be synthesizable//-rules PreDefAttr // Use of certain pre-defined attributes may not be synthesizable//-rules ResFunction // Resolution functions may not be synthesizable-rules STARC05-2.1.6.5 // For an array index x and z should not be used

-overloadrules STARC05-2.1.6.5+severity=Warning-rules STARC05-2.3.1.2c // Do not use unsynthesizable User-Defined Primitives (UDPs).

-overloadrules STARC05-2.3.1.2c+severity=Error//-rules UserDefAttr // Use of user-defined attribute may not be synthesizable//-rules W182g // tri0 declarations may not be synthesizable//-rules W182h // tri1 declarations are not synthesizable//-rules W182k // trireg declarations are not synthesizable//-rules W182n // Switches such as cmos, pmos & nmos are not synthesizable-rules W421 // Always block/process does not have event control

-overloadrules W421+severity=Error-rules W442a // Reset sequence may not be synthesizable. First statement in block mustbe an if statement-rules W442b // Reset sequence may not be synthesizable. The reset condition is too complex-rules W442c // Reset sequence may not be synthesizable. Reset can only be modified by! or ~ in the if condition-rules W442f // The specified reset sequence may not be synthesizable. Only binary operators that canbe used in 'if' are '==' and '!='//-rules SignedUnsignedExpr-ML // Do not mix signed & unsigned variables/constants in expressions, assignment statements or in comparisons.//-rules sim_race01 // Assignment and use of signal in same simulation cycle (Read-Write Race)

//-overloadrules sim_race01+severity=Warning-rules sim_race02 // Multiple assignments to a signal

-overloadrules sim_race02+severity=Warning-rules W110a // Use same port index bounds in component instantiation and entity declaration//-rules W239 // Hierarchical references may not be synthesizable-rules W416 // Range of return type and return value of a function should be same

-overloadrules W416+severity=Error//-rules BothPhase // Process has a clock driving it on both edges - may not be synthesizable-rules CheckDelayTimescale-ML // Delay used without timescale compiler directive//-rules ClockStyle // A clocking style is used which may not be synthesizable//-rules DiffTimescaleUsed-ML // Design should not have different timescales for different modules//-rules MultipleWait // Multiple wait statements having same clock expression may not be synthesizableby some synthesis tools//-rules NoSigCaseX-ML // Design should not use signals in casex and casez constructs-rules PragmaComments-ML // Pragma Comments have been detected.

-overloadrules PragmaComments-ML+severity=Data//-rules SetBeforeRead-ML // Variable may not be set before being read

//-overloadrules SetBeforeRead-ML+severity=Error//-rules SigVarInit // Initial values of signals and variables will be ignored by some synthesis tools//-rules STARC05-2.1.2.5v // Do not use attribute enum_encoding//-rules STARC05-2.1.8.6 // Global signals must not be read in a subprogram description-rules STARC05-2.10.2.3 // Do not perform logical negation on vectors

-overloadrules STARC05-2.10.2.3+severity=Warning//-rules STARC05-2.10.3.7 // Match the bit width with the base number part-rules STARC05-2.11.3.1 // Sequential and combinational parts of an FSM description should be in separate always/process blocks

-overloadrules STARC05-2.11.3.1+severity=Warning//-rules STARC05-2.3.1.4 // Paths other than flip-flop data paths must not have delays-rules STARC05-2.3.1.5b // Delay values must be non-negative.

-overloadrules STARC05-2.3.1.5b+severity=Error//-rules STARC05-2.3.2.4 // Variables if used, must be assigned to a signal before the end of the process//-rules SynthIfStmt // IF-statement may not be synthesizable//-rules W127 // Delay values should not contain X(unknown value) or Z(high-impedance state)//-rules W129 // Variable delay values should be avoided//-rules W182c // time declarations are not synthesizable//-rules W189 // Nested Synopsys translate_off comments //-rules W190 // Task or procedure declared but not used//-rules W213 // PLI Task/Functions are not synthesizable-rules W215 // Inappropriate bit select for integer or time variable-rules W216 // Inappropriate range select for integer or time variable//-rules W226 // Case select expression is constant//-rules W245 // Probably intended "or", not "|" or "||" in sensitivity list//-rules W250 // The disable statement may not be synthesizable//-rules W253 // Data event has an edge//-rules W254 // Reference event does not have an edge//-rules W280 // A delay has been specified in a non-blocking assignment-rules W289 // A real operand is being used in a logical comparison

-overloadrules W289+severity=Error-rules W292 // Comparison of Real operands is not recommended-rules W293 // A function returns a real value, which is unsynthesizable

-overloadrules W293+severity=Error//-rules W294 // Real variables are unsynthesizable-rules W317 // Assignment to a supply net-rules W352 // The condition inside a "for" statement is constant

-overloadrules W352+severity=Error-rules W398 // A case choice is covered more than once in a case statement

-overloadrules W398+severity=Error-rules W422 // Unsynthesizable process: event control has more than one clock

-overloadrules W422+severity=Error-rules W424 // Function or subprogram sets a global signal/variable//-rules W425 // Function or sub-program uses a global signal/variable-rules W426 // Task sets a global variable//-rules W427 // Task uses a global variable//-rules W430 // The "initial" statement is not synthesizable//-rules W443 // 'X' value used

//-overloadrules W443+severity=Warning//-rules W444 // 'Z' or '?' value used

//-overloadrules W444+severity=Warning//-rules W464 // Unrecognized synthesis directive used in the design-rules W467 // Use of don't-care except in case labels may lead to simulation/synthesis mismatch-rules W480 // Loop index is not of type integer-rules W481a // Possibly unsynthesizable loop: step variable differs from variable used in condition-rules W481b // Unsynthesizable loop: step variable differs from variable used in initialization-rules W496a // Comparison to a tristate in a condition expression is treated as false in synthesis.-rules W496b // Comparison to a tristate in a case statement is treated as false in synthesis.//-rules WhileInSubProg // While statements used inside subprograms may be unsynthesizable//-rules ArrayIndex // Bus signals are declared with low-order bit first

-checkalldimension="yes" // Rule will check all dimensions of signal packed and unpacked.//-rules DisallowCaseX-ML // Design should not use casex constructs//-rules DisallowCaseZ-ML // Design should not use casez constructs//-rules DisallowXInCaseZ-ML // casez statement should not use "x" -rules NoAssignX-ML // RHS of the assignment contains 'X'-rules NoXInCase-ML // Case expression and case choices should not have 'X' //-rules ParamOverrideMismatch-ML // Mismatch in the number of parameter over-rides and number of parameters in theinstantiated module

//-overloadrules ParamOverrideMismatch-ML+severity=Warning-rules ParamWidthMismatch-ML // Parameter width does not match with the value assigned

-overloadrules ParamWidthMismatch-ML+severity=Warning-rules ReportPortInfo-ML // Generate a report of all ports of top level block and black-box instances.

-overloadrules ReportPortInfo-ML+severity=Data-rules STARC05-2.1.3.1 // Bit-width of function arguments must match bit-width of the correspondingfunction inputs.

-overloadrules STARC05-2.1.3.1+severity=Warning-rules STARC05-2.1.5.3 // Conditional expressions should evaluate to a scalar.

-overloadrules STARC05-2.1.5.3+severity=Warning-rules STARC05-2.2.3.3 // Do not assign over the same signal in an always construct for sequential circuits

-overloadrules STARC05-2.2.3.3+severity=Warning-rules STARC05-2.3.1.6 // Same logic level of reset signal must be checked as specified in the sensitivitylist of the always block.

-overloadrules STARC05-2.3.1.6+severity=Warning//-rules STARC05-2.3.2.2 // Do not use blocking and non-blocking assignments together in same alwaysblock.-rules W110 // An instance port connection has incompatible width compared to the port definition

-overloadrules W110+severity=Error//-rules W111 // Not all elements of an array are read-rules W116 // Unequal length operands in bit wise logical/arithmetic/relational operator-rules W122 // A signal is read inside a combinational process but is not included in the sensitivity list

-overloadrules W122+severity=Error-rules W123 // A signal or variable has been read but is not set

-overloadrules W123+severity=Error

-ignoreModuleInstance="yes" // Ignore signals which are unset but used in port mapping.//-rules W159 // Condition contains a constant expression//-rules W164a // LHS width is less than RHS width of assignment (Truncation)

//-overloadrules W164a+severity=Warning//-rules W164b // LHS width is greater than RHS width of assignment (Extension)-rules W19 // Truncation of extra bits

-overloadrules W19+severity=Error//-rules W210 // Number of connections made to an instance does not match number of ports on master

//-overloadrules W210+severity=Warning-rules W218 // Multi-bit signal used in sensitivity list

-overloadrules W218+severity=Error-rules W240 // An input has been declared but is not read

-checkfullbus="yes"

-checkfullrecord="yes"//-rules W241 // Output is never set-rules W263 // A case expression width does not match case select expression width-rules W337 // Illegal value (e.g. real) being used or X, Z or ? being used inappropriately asa case item//-rules W342 // Constant will be X-extended//-rules W343 // Constant will be Z-extended-rules W362 // Unequal length in arithmetic comparison operator//-rules W423 // A port with a range is redeclared with a different range//-rules W446 // Output port signal is being read (within the module)

//-overloadrules W446+severity=Error//-rules W456a // A signal is included in the sensitivity list of a combinational process blockbut none of its bits is read in that block-rules W486 // Shift overflow - some bits may be lost//-rules W491 // Constant will be ?-extended-rules W499 // Not all bits of a function are set in the function-rules W502 // A variable in sensitivity list is modified inside the always block-rules W505 // Value assigned inconsistently - may not be synthesizable

-overloadrules W505+severity=Error//-rules W551 // A case statement marked full_case or a priority/unique case statement have a default clause.-rules W66 // Unsynthesizable repeat loop because repeat expression is not constant

-overloadrules W66+severity=Error-rules InferLatch // Latch inferred

-overloadrules InferLatch+severity=Error-rules RegInputOutput-ML // Module output and input port should be registered

-overloadrules RegInputOutput-ML+severity=Data

-chkTopModule="yes" // Rule checkign will be done only for top module-rules STARC05-2.3.4.1v // Flip-flop output must not have initial value in signal/variable declaration

-overloadrules STARC05-2.3.4.1v+severity=Warning//-rules STARC05-2.3.6.1 // Do not mix descriptions of flip-flops with asynchronous reset and flip-flopswithout asynchronous reset in the same process/always block-rules STARC05-2.5.1.7 // Tri State output should not be used in the conditional expression of if statement

-overloadrules STARC05-2.5.1.7+severity=Warning-rules STARC05-2.5.1.9 // Tri State output should not be entered in the selection expression of casex and casez statement

-overloadrules STARC05-2.5.1.9+severity=Warning-rules STARC05-2.10.3.2a // Bit-width of operands of a logical operator must match.//-rules UseMuxBusses // Tristate nets detected

//-overloadrules UseMuxBusses+severity=Warning-rules W336 // Blocking assignment should not be used in a sequential block (may lead to shoot through)

-overloadrules W336+severity=Error-rules W414 // Use of non-blocking assignment in a combinational block

-overloadrules W414+severity=Error

-treat_latch_as_combinational="yes" // Always block inferring latch will be treated as combinational block.//-rules W428 // Task called in a combinational block-rules W450L // Multi-bit expression used as latch enable may not be synthesizable

-overloadrules W450L+severity=Warning-rules UndrivenInTerm-ML // Undriven but loaded input terminal of an instance detected

-overloadrules UndrivenInTerm-ML+severity=Error

-checkInHierarchy="yes" // Rule will dive down the hierarchy to look for driver

-checkRTLCInst='yes' // Rule will report violation for RTLC instances//-rules UndrivenNUnloaded-ML // Undriven and Unloaded nets/terminals detected in the design//-rules UnloadedInPort-ML // Unloaded but driven input port of a module detected//-rules LogicDepth // Logic depth exceeds specified number of levels (using parameter delaymax/delaymax_memtoflop/delaymax_floptomem/delaymax_memtomem/delaymax_err/delaymax_inputtoflop/delaymax_floptoflop/delaymax_inputtooutput/delaymax_floptooutput)

//-delaymax=500-rules BufClock // Clock buffer detected

-overloadrules BufClock+severity=Warning-rules checkPinConnectedToSupply // IO-ports or Output ports of cells/modules may not be connected to supply signals.

-overloadrules checkPinConnectedToSupply+severity=Error//-rules ClockEdges // Do not use both levels of the clock to drive latches-rules CombLoop // Combinational loop exists

-overloadrules CombLoop+msgLabel=CombLoop+severity=Error

-enableE2Q="yes" // Report comb loop from Enable to Q pin of flop.//-rules DisabledAnd // And/Nand gate is disabled//-rules DisabledOr // Or/Nor gate is disabled-rules FlopClockConstant // Flip-flop clock pin driven by a constant value

-overloadrules FlopClockConstant+msgLabel=FlopClockConstant+severity=Error//-rules FlopDataConstant // Flip-flop data pin driven by a constant value-rules FlopEConst // Flip-flop enable pin is permanently disabled or enabled-rules FlopSRConst // Flip-flop set or reset pin is permanently enabled//-rules IntReset // Internally generated reset detected

//-overloadrules IntReset+msgLabel=IntReset+severity=Warning//-rules LatchDataConstant // Latch data pin driven by a constant value//-rules LatchEnableConstant // Latch enable pin driven by a constant value-rules LatchFeedback // There should not be a combinational feedback path from a latch output to data or enable of the same latch.

-overloadrules LatchFeedback+severity=Error//-rules LatchGatedClock // Do not use gated/internally generated clock to drive latches

//-overloadrules LatchGatedClock+msgLabel=LatchGatedClock+severity=Warning//-rules LatchReset // Reset pin should not be used both synchronously and asynchronously //-rules LogNMux // LogN mux with large number of inputs detected - potential performance problem

//-logmux_max=5//-rules MuxSelConst // Mux select is constant.//-rules RegOutputs // Some outputs from a top module are not registered

//-overloadrules RegOutputs+severity=Warning

-reportundrivenout='no' // Rule will not report violation for undriven outputs.//-rules SetResetConverge-ML // Fanin cone of Set and Reset pin of a flop/latch converge-rules STARC05-1.2.1.2 // Do not create a RS latch using primitive cells such as AND, OR

-overloadrules STARC05-1.2.1.2+severity=Error-rules STARC05-1.3.1.3 // Asynchronous reset/preset signals must not be used as non-reset/preset orsynchronous reset/preset signals

-overloadrules STARC05-1.3.1.3+severity=Warning//-rules STARC05-1.3.1.7 // A flip-flop must not have both asynchronous set and asynchronous reset-rules STARC05-1.4.3.4 // Flip-flop clock signals must not be used as non-clock signals

-overloadrules STARC05-1.4.3.4+severity=Warning-rules STARC05-2.1.4.5 // Use bit-wise operators instead of logic operators in multi-bit operations

-overloadrules STARC05-2.1.4.5+severity=Warning-rules STARC05-2.4.1.5 // Do not use two level latches in the same phase clock

-overloadrules STARC05-2.4.1.5+severity=Error-rules STARC05-2.5.1.2 // Logic must not exist in tristate enable conditions//-rules STARC05-2.5.1.4 // A tristate bus should not be driven by more than the specified number of drivers

//-overloadrules STARC05-2.5.1.4+severity=Warning//-rules TristateConst // Tristate gate enable is constant//-rules W391 // Design has a clock driving it on both edges-rules W392 // Do not use a reset or set with both positive and negative polarity within the samedesign unit-rules W415 // Variable/signal that does not infer a tristate and has multiple simultaneous drivers

-overloadrules W415+msgLabel=W415+severity=Error

-assume_driver_load="yes" // Rule will report violation for unloaded signals/variables.

-checkconstassign="yes" // Rule will report violation for constant assignments//-rules W422L // Multiple clocks in the event control list of latch is not allowed

//-overloadrules W422L+msgLabel=W422L+severity=Warning-rules STARC05-2.10.1.4a // Signals must not be compared with X or Z.-rules STARC05-2.10.1.4b // Signals must not be compared with values containing X or Z.-rules W156 // Do not connect buses in reverse order-rules STARC05-2.3.3.1 // Do not use multiple clock signals in a single process block-rules W415a // Signal may be multiply assigned (beside initialization) in the same scope.-rules W287b // Output port of an instance is not connected-rules W224 // Multi-bit expression found when one-bit expression expected-rules W287a // Some inputs to instance are not driven or unconnected-rules W528 // A signal or variable is set but never read-rules mixedsenselist // Mixed conditions in sensitivity list may not be synthesizable-rules W339a // Case equal operator (===) and case not equal (!==) operators may not be synthesizable-rules NoFeedThrus-ML // Block should not contain feed-throughs-rules STARC05-2.8.3.3 // Do not use //synopsys full_case pragma when all conditions are not described as case clause or the default clause is missing-rules UndrivenOutTermNLoaded-ML // Undriven output pins connected to instance input-rules UndrivenOutPort-ML // Undriven but loaded output port of a module detected-rules W146 // Use named-association rather than positional association to connect to an instance-rules W188 // Do not write to input ports-rules W401 // Clock signal is not an input to the design unit-rules W402b // Asynchronous set/reset signal is not an input to the module-rules W468 // Index variable is too short-rules W527 // Dangling else in sequence of if conditions. Make sure nesting is correct-rules W576 // Logical operation on a vector// -rules CheckShiftOperator-ML // Logical and arithmetic shift operation detection on signed and unsigned operand(s) or expression(s) respectively// -rules HangingInstOutput-ML // Net connected to output port of instance is unconnected// -rules ResetFlop-ML // All the flip-flops should have either asynchronous set/reset or synchronous set/reset// -rules SelfDeterminedExpr-ML // Self-determined expression present in the design// -rules UndrivenNet-ML // Undriven but loaded net is detected in the design// -rules UnrecSynthDir-ML // Synthesis directive is not recognized-rules STARC05-2.8.1.4 // case constructs must have the default clause

-overloadrules STARC05-2.8.1.4+severity=Error// -rules AlwaysFalseTrueCond-ML // Preferably avoid using always-false and always-true conditions// -rules ClockEnableRace // Reports a race condition between the clock and enable signal of a flop// -rules ConstantInput-ML // Input to a particular module is tied to a constant value// -rules IfWithoutElse-ML // An "if" clause does not have a corresponding "else" clause and is not preceded by assignment of target signal// -rules NoExprInPort-ML // Port connections in instances should not contain expressions// -rules RedundantLogicalOp-ML // Logical operation result is same as one of the operands or is a constant// -rules STARC05-2.10.7.1 // Do not use arithmetic operation in the conditional expression of if statements// -rules STARC05-2.2.2.3a // Multiple event Expressions should not be described with always constructs// -rules STARC05-2.7.2.2 // Avoid describing conditions that will not be executed// -rules STARC05-2.1.3.2 // Bit-width of function return value must match the bit-width of assignment destination signal// -rules STARC05-2.1.3.4 // Return value assignment statement must be the last statement in function description// -rules STARC05-2.4.1.3 // Latches should not have asynchronous set or asynchronous reset// -rules STARC05-2.8.1.5 // Do not use the full_case directive// -rules STARC05-2.9.1.2b // Terminating condition of "for" constructs must be a constant// -rules STARC05-2.9.1.2c // The value of loop variable must not be modified inside the "for" construct// -rules UnConstrLoop-ML // Unconstrained loops should not be used// -rules UnpackedStructUsed-ML // Do not declare unpacked structures outside the package// -rules W143 // Macro has been redefined// -rules W154 // Do not declare nets implicitly// -rules W17 // Prefer full range of a bus/array in sensitivity list. Avoid bits or slices// -rules W171 // Case label is not constant// -rules W242 // A function is calling itself; i.e. it is recursive-rule ComplexModport-ML //Added new rule to detect complex modport declerations which gives error by DC-rule ConcatUnsizedNumbers-ML //Rule will report violations for concatenation of unsized numbers-rule DuplicateCaseLabel-ML //A case choice is covered more than once in a case statement when "parallel_case" pragma is specified-rule HangingInstInput-ML //Hanging Instance Input-rule InterfaceWithoutModport-ML //Interfaces should make use of modport declarations-rule NoStrengthInput-ML //Synthesis tools ignore strength inputs-rule SensListRepeat-ML //A signal is repeated multiple times in the sensitivity list-rule TwoStateData-ML //Avoid using two state data type signals in RTL-rule TypedefNameConflict-ML //Variable name should not be same as that of the system verilog typedefined name-rule UniqueIfMissingCond-ML //The unique keyword tells all software tools that each selection item in a series of decisions is unique from any other selection item in that series-rule UseParamWidthInOverriding-ML //Parameters should not be overridden without specifying the width in instantiations-rule W295 //Event variables may not be synthesizable-rule W346 //Task may be unsynthesizable because it contains multiple event controls-rule W479 //Loop step statement variables are not properly incremented or decremented// -rule DefaultState //State-machine does not have a defined default state// -rule infiniteloop //While/forever loop has no break control// -rule NoGenLabel-ML //Unnamed generate block or duplicate generate block names used in module// -rule ReserveNameSystemVerilog-ML //System Verilog IEEE-1800 reserved word used// -rule SelfGatingRegister-ML //Self-Gating detected for the flop// -rule STARC05-2.9.1.2e //Do not use loop variable outside of the "for" loop// -rule SVConstruct-ML //System Verilog construct used// -rule UniqueCase-ML //Unique or priority case constructs used with full_case or parallel_case or both.// -rule UseSVAlways-ML // Use system verilog always construct// -rule UseSVCasting-ML //Use SV casting when assigning a packed bit vector to a packed structure// -rule W167 //Module has no input or output ports// -rule W187 //The 'default' or 'others' clause should be the last clause in a case statement// -rule W345 //Presence of an event control in a task or procedure body may not be synthesizable// -rule W489 //The last statement in a function does not assign to the function// -rule W504 //Integer is used in port expression注釋

? ? ? ? 在目標文件的開頭,大段注釋說明了該目標的版本信息,其中包括新添加的規則名,規則屬于的策略名等信息。

描述信息

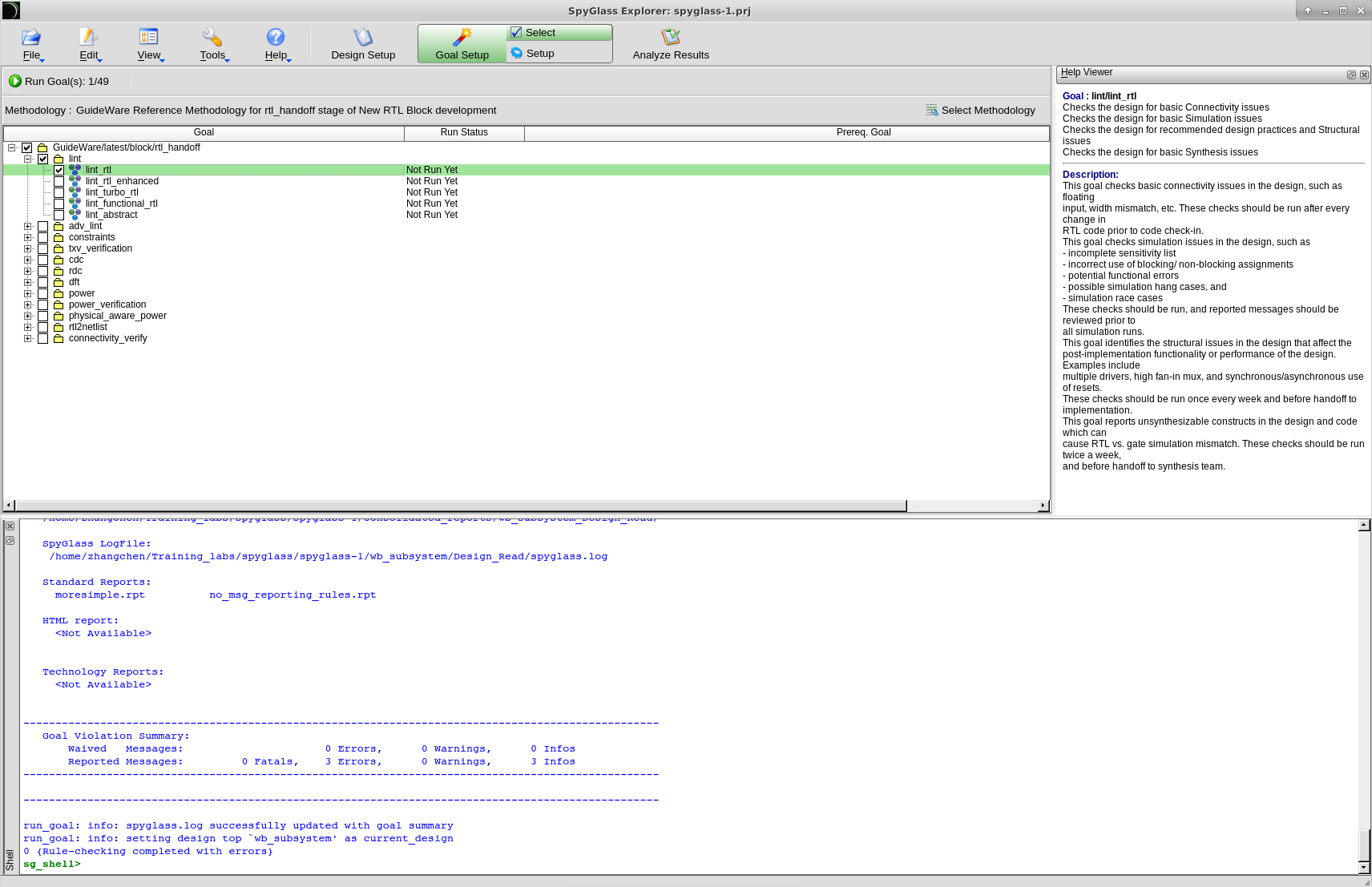

? ? ? ? 隨后的=template和=cut包圍的是目標的描述信息,該信息能出現在GUI界面的Help窗口中,如圖1所示。

圖1 目標的描述信息

策略注冊

? ? ? ? -policies參數指定了目標中會使用到哪些策略中的規則,對于lint_rtl規則,它使用了以下策略。

openmore

starc

starc2005

erc

simulation

lint

latch

spyglass

morelint

timing規則設置

? ? ? ? 對于已在策略中包含的規則:

? ? ? ? 可以使用-rules/-addrules選項指定目標包含的規則,注意到這與在sourcelist添加選項和參數的用法類似,等價于在sg_shell中使用set_goal_option rules/addrules命令。

? ? ? ? 可以使用-ignorerules選項指定要忽略的規則(某些來自spyglass策略的內建規則無法被忽略),注意到這與在sourcelist添加選項和參數的用法類似,等價于在sg_shell中使用set_goal_option ignorerules命令。

? ? ? ? 可以使用-overloadrules選項改變規則的嚴重性標簽、權重以及自定義信息,注意到這與在sourcelist添加選項和參數的用法類似,等價于在sg_shell中使用set_goal_option overloadrules命令。

參數默認值覆蓋

????????對于已在策略中包含的參數:

? ? ? ? 可以使用-parameter進行參數默認值的覆蓋,注意到這與在sourcelist添加選項和參數的用法類似,等價于在sg_shell中使用set_parameter parameter命令。

? ? ? ? 對于參數設置以及默認值覆蓋的更詳細介紹,參考下面的博客。

Spyglass:參數(parameter)及其設置方式![]() https://chenzhang.blog.csdn.net/article/details/148043280?spm=1001.2014.3001.5502

https://chenzhang.blog.csdn.net/article/details/148043280?spm=1001.2014.3001.5502

定義嚴重性標簽

? ? ? ? 可以使用-define_severity選項自定義嚴重性標簽,注意到這與在sourcelist添加選項和參數的用法類似,等價于在sg_shell中使用set_goal_option define_severity命令。

寫在最后

? ? ? ? 其實可以把目標文件看作是一個sourcelist,每當使用current_goal命令切換目標時就會讀取并執行,但里面只能包含特定選項和參數的設置,與使用sg_shell是等價的。

)

)

)