一、FPGA 在線升級

FPGA 在線升級FLASH時,一般是通過邏輯生成SPI接口操作FLASH,當然也可以通過其他SOC經FPGA操作FLASH,那么FPGA就要實現在啟動后對FLASH的控制。

對于7Series FPGA,只有CCLK是專用引腳,SPI接口均為普通IO可直接通過約束解決,CCLK產生需通過STARTUPE2產生。

對于UltraScale 及UltraScale+系列,所有FLASH配置引腳(包含CCLK和SPI)均為專用引腳,在bit運行時需通過STARTUPE3產生。

二、STARTUPE2

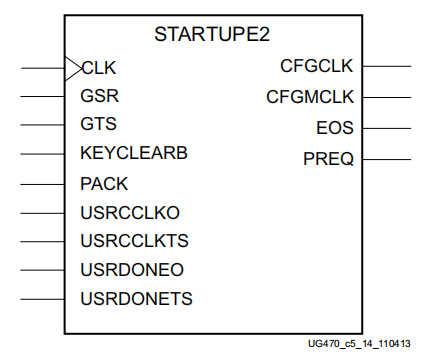

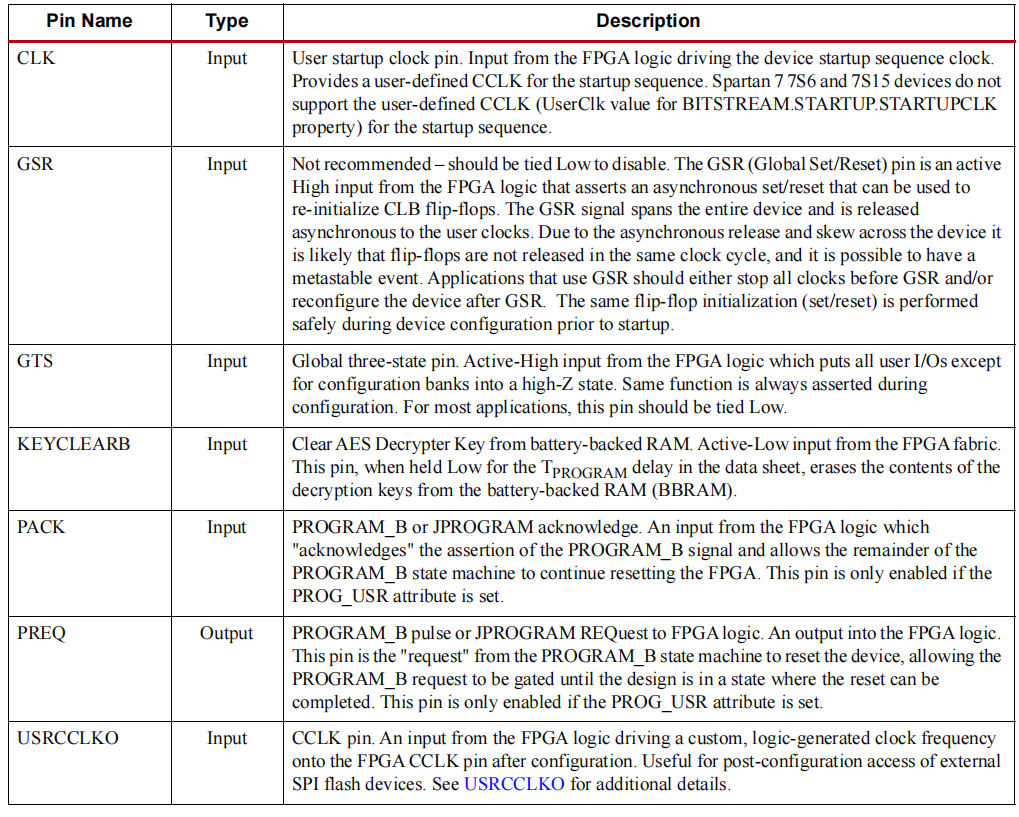

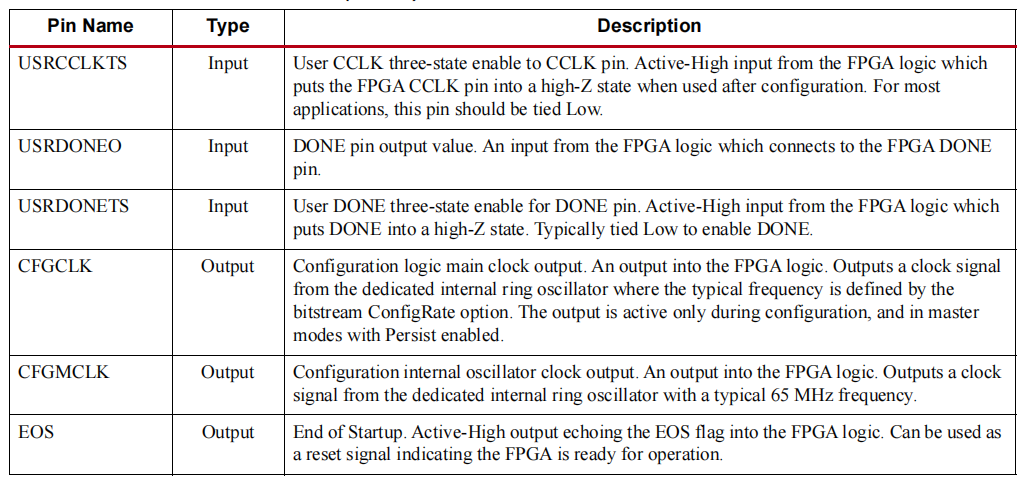

??參考Xilinx ug470,STARTUPE2接口框圖如下:

對SPI設置為X1,STARTUPE2例程如下:

STARTUPE2 #(.PROG_USR("FALSE"), // Activate program event security feature. Requires encrypted bitstreams..SIM_CCLK_FREQ(0.0) // Set the Configuration Clock Frequency(ns) for simulation.)STARTUPE2_spi (.CFGCLK(), // 1-bit output: Configuration main clock output.CFGMCLK( ), // 1-bit output: Configuration internal oscillator clock output.EOS(), // 1-bit output: Active high output signal indicating the End Of Startup..PREQ(), // 1-bit output: PROGRAM request to fabric output.CLK(1'b0), // 1-bit input: User start-up clock input.GSR(1'b0), // 1-bit input: Global Set/Reset input (GSR cannot be used for the port name).GTS(1'b0), // 1-bit input: Global 3-state input (GTS cannot be used for the port name).KEYCLEARB(1'b1), // 1-bit input: Clear AES Decrypter Key input from Battery-Backed RAM (BBRAM).PACK(1'b1), // 1-bit input: PROGRAM acknowledge input.USRCCLKO(i_SPI1_CLK), // 1-bit input: User CCLK input.USRCCLKTS(1'b0), // 1-bit input: User CCLK 3-state enable input.USRDONEO(1'b1), // 1-bit input: User DONE pin output control.USRDONETS(1'b1) // 1-bit input: User DONE 3-state enable output);assign o_QSPI_flash_MOSI = i_SPI1_MOSI;

assign o_QSPI_flash_CSB = i_SPI1_CSB;

assing o_SPI1_MISO = i_QSPI_flash_MISO;

其中:

(1)o_QSPI_flash_MOSI、o_QSPI_flash_CSB、i_QSPI_flash_MISO、o_QSPI_flash_SCLK為連接到FLASH的信號,i_SPI1_MOSI、i_SPI1_CSB、o_SPI1_MISO、i_SPI1_CLK為FPGA內部產生或其他SOC產生的配置FLASH SPI信號,FPGA通過STARTUPE2 和邏輯完成這些信號和FLASH的連接;

(2)STARTUPE2 中USRCCLKO為輸入,USRCCLKTS為三態控制信號,當USRCCLKTS=0,時USRCCLKO輸出到CCLK,用于配置FLASH,因CCLK為專用管腳,故代碼中不需要CCLK的描述;

(3)USRDONETS的控制與USRCCLKTS類似,USRDONETS=0,USRDONEO直接輸出到FPGA的配置DONE引腳

(4)CFGCLK為輸出的配置時鐘,FPGA可用該時鐘產生SPI邏輯,也可用其他時鐘信號

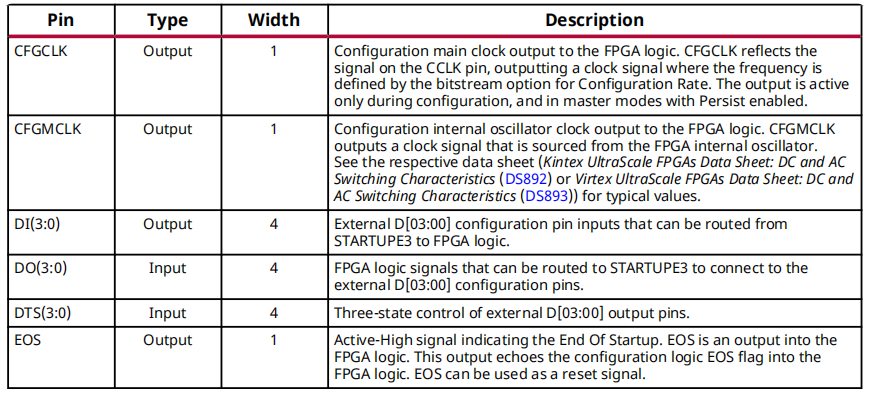

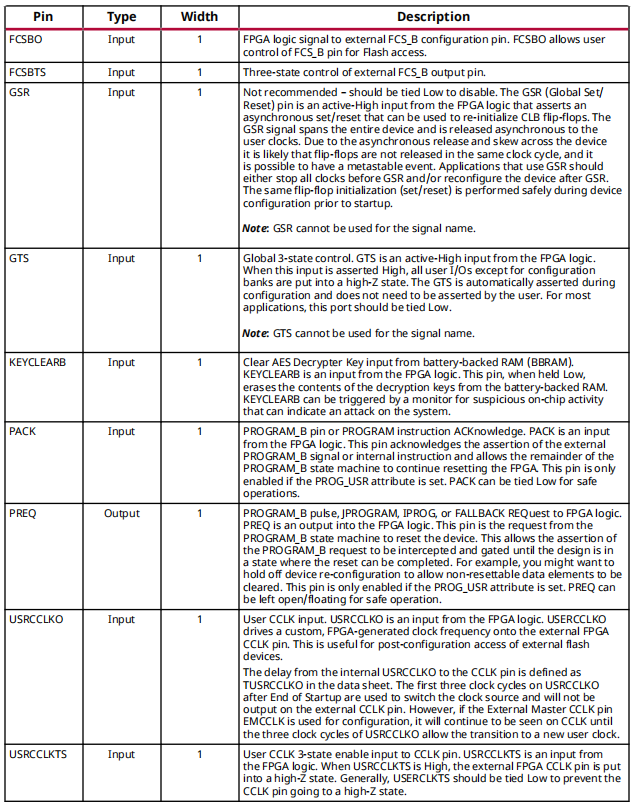

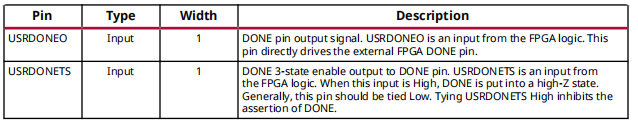

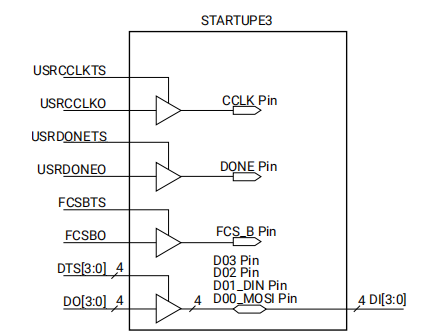

三、STARTUPE3

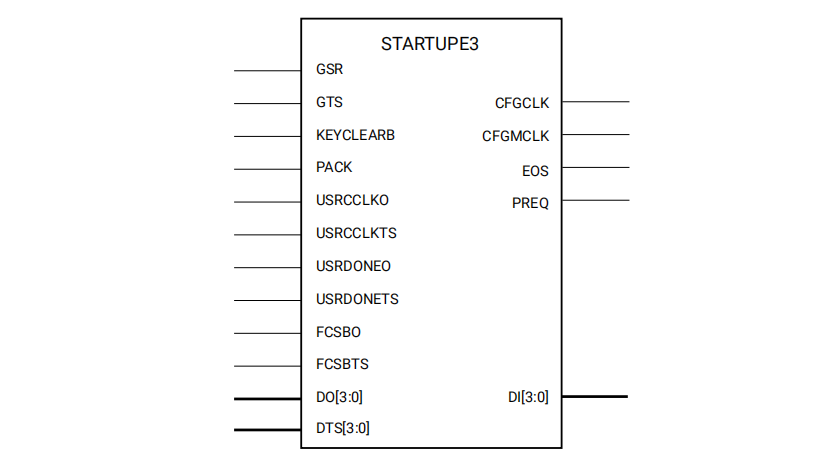

??參考Xilinx ug570,STARTUPE3接口框圖如下:

對SPI設置為X1,STARTUPE3例程如下:

wire [3:0] QSPI_in_null;STARTUPE3 #(.PROG_USR("FALSE"), // Activate program event security feature. Requires encrypted bitstreams..SIM_CCLK_FREQ(0.0) // Set the Configuration Clock Frequency (ns) for simulation.)STARTUPE3_inst (.CFGCLK(), // 1-bit output: Configuration main clock output..CFGMCLK(), // 1-bit output: Configuration internal oscillator clock output..DI({QSPI_in_null[3:2],i_QSPI_flash_MISO,QSPI_in_null[0]}), // 4-bit output: Allow receiving on the D input pin..EOS (), // 1-bit output: Active-High output signal indicating the End Of Startup..PREQ(), // 1-bit output: PROGRAM request to fabric output..DO({3'b111,o_QSPI_flash_MOSI}), // 4-bit input: Allows control of the D pin output..DTS(4'b0010), // 4-bit input: Allows tristate of the D pin..FCSBO(o_QSPI_flash_CSB), // 1-bit input: Controls the FCS_B pin for flash access..FCSBTS(1'b0), // 1-bit input: Tristate the FCS_B pin..GSR(1'b0), // 1-bit input: Global Set/Reset input (GSR cannot be used for the port)..GTS(1'b0), // 1-bit input: Global 3-state input (GTS cannot be used for the port name)..KEYCLEARB(1'b1 ), // 1-bit input: Clear AES Decrypter Key input from Battery-Backed RAM (BBRAM)..PACK(1'b1), // 1-bit input: PROGRAM acknowledge input..USRCCLKO(o_QSPI_flash_SCLK), // 1-bit input: User CCLK input..USRCCLKTS(1'b0), // 1-bit input: User CCLK 3-state enable input..USRDONEO(1'b1), // 1-bit input: User DONE pin output control..USRDONETS(1'b1) // 1-bit input: User DONE 3-state enable output.);

其中:

(1)o_QSPI_flash_MOSI、o_QSPI_flash_CSB、i_QSPI_flash_MISO、o_QSPI_flash_SCLK為FPGA內部產生或其他SOC產生的配置FLASH SPI信號,FPGA通過STARTUPE3 和邏輯完成這些信號和FLASH的連接,應CCLK和SPI均為專用管腳,故代碼中不需要CCLK的描述;

(2)STARTUPE3 中USRCCLKO為輸入,USRCCLKTS為三態控制信號,當USRCCLKTS=0,時USRCCLKO輸出到CCLK,用于配置FLASH

(3)DO為FPGA輸出到FLASH的QSPI 數據信號,例程采用了SPIx1,僅D0 MOSI有效,D3 D2設置為1,falsh WP_B和HOLD_B信號無效;

(4)DI為FLASH輸入到FPGA的QSPI 數據信號,例程采用了SPIx1,僅D1 MISO有效;

(5)DTS為數據信號方向,例程采用了SPIx1,所以D0為MOSI,D1為MISO,其他為WP和HOLD信號,所以DTS設置為4’b0010

(4)FCSBO為FPGA輸出到FLASH的FCSBO信號,FCSBTS=0表示由FPGA邏輯輸出o_QSPI_flash_CSB到FLASH的CSB

(5)DTS為數據信號方向,例程采用了SPIx1,所以D0為MOSI,D1為MISO,其他為WP和HOLD信號,所以DTS設置為4’b0010

(6)USRDONETS的控制與USRCCLKTS類似,USRDONETS=0,USRDONEO直接輸出到FPGA的配置DONE引腳

(7)CFGCLK為輸出的配置時鐘,FPGA可用該時鐘產生SPI邏輯,也可用其他時鐘信號

STARTUPE3有許多三態控制,如下圖所示,當三態控制信號為0時,信號按下圖中反向傳輸,為1是反向。

參考文件

ug570-ultrascale-configuration

ug470-ultrascale-configuration

:從基礎到高頻面試題)

)