英飛凌針對硬件故障的自測,提供了四種機制:PBIST、LBIST、MONBIST和MBIST。

LBIST和MONBIST我們已經聊過了,今天就快速介紹下MBIST。

MBIST,全程Memory Built-in Self Test,用于檢測SRAM數據單元的完整性。

在26262中,SRAM cell出現錯誤被認為是潛伏故障,而潛伏故障要求至少一個上電周期要完成一次檢測,因此MBIST的使用時機就完全取決于使用者,可以是上電檢測、也可以是下電檢測、甚至可以在程序運行時檢測。

雖然時機隨心所欲,但是做MBIST的時候還需要考慮兩個前置條件:(1)測試前SRAM需要完成初始化,有正確的ECC;(2)SRAM在測試時不允許被訪問。

因此,這就引出了今天的話題,如何測試內核相關的memory。

1. 單核和多核

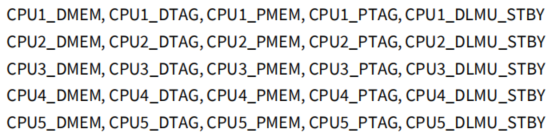

根據芯片手冊,TC3xx CPU有如下幾類SRAM可供使用:

- P\DSPR:Program\Data?Scratch Pad SRAM,類比ARM內核的TCM;

- P\DCACHE:Progaram\Data Cache

- P\DTAG:Cache相關的Tag SRAM

為了提升效率,我們用到的最多肯定就是PSPR、DSPR等,常規用法:PSPR存放性能要求或者是特定場景的函數,DSPR用于堆棧、CSA或者其他自定義等數據存放;但做mbist的時候被測memory又不能被訪問,這就要求相關memory的CPU需要停下來。

因此,我們需要分多核和單核情況。

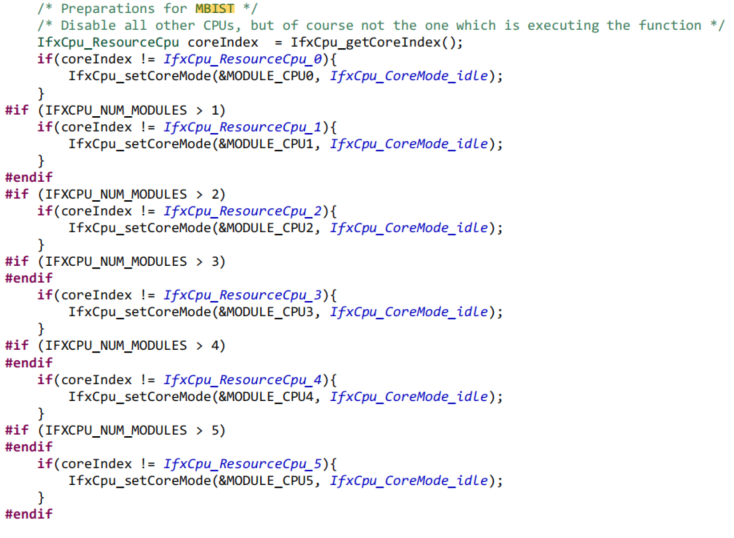

多核相對好解決一點,cpu0最先啟動,在它釋放其他core時讓cpu0去測試其他core的memory,如下:

?其他core去測cpu0時,讓cpu0進入ilde即可。代碼如下:

單核的情況說起來也簡單,就是讓CPU在執行測試期間不訪問DSPR和PSPR,在英飛凌的MTU設計中,當我們使能了SRAM的SSH后該SRAM就不能訪問了,

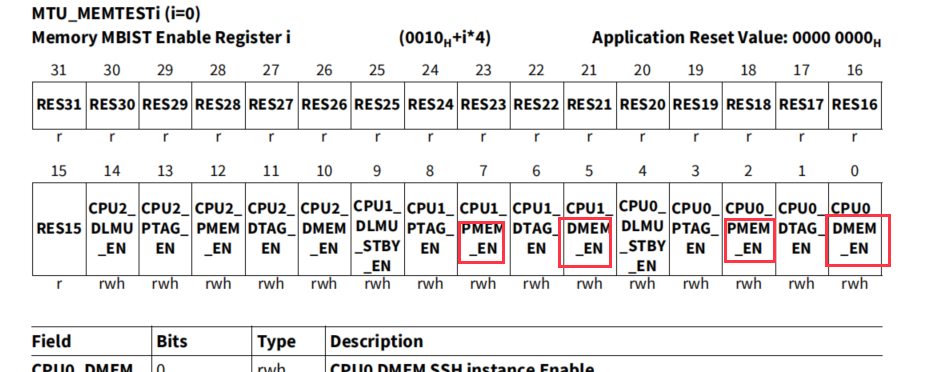

(代碼示例MTU_MEMTEST0.B.CPU0_DMEM_EN = 1;)

這就需要我們在設計鏈接文件的時候要了解DSPR和PSPR具體包含了啥內容,并且在執行上述代碼后就不調用PSPR的函數,也不要使用stack、csa,只用cpu相關寄存器,參考代碼如下:

此外,為防止cache訪問,P\D Cache在被測試的時候都需要關閉,參考CPU寄存器PMAxx。

2.MTU中PMEM的特殊處理

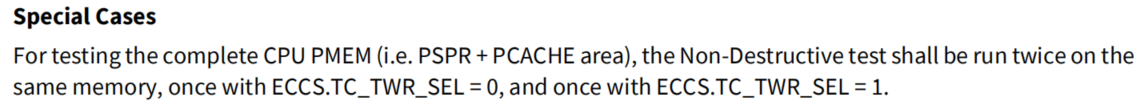

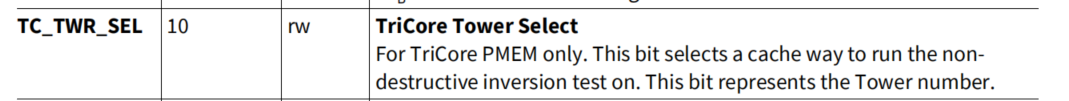

在手冊里,有一點我沒有特別想明白,但也是比較關鍵的地方,就是關于PMEM的特殊處理,原文如下:

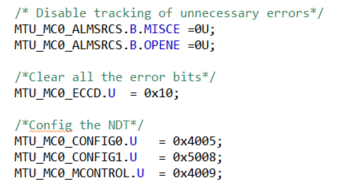

要完整測試PMEM,就需要執行兩次NDT測試,由寄存器TCCS.TC_TWR_SEL進行管理,如下:

?那代碼中處理也比較方便,偽代碼如下:

if(E_OK == CheckPmem(SramInstanceID))

{MTU_MCx.ECCS.TC_TWR_SEL = 0;triggerTest(SramInstanceID);MTU_MCx.ECCS.TC_TWR_SEL = 1;triggerTest(SramInstanceID);

}?但有一點一直沒想明白,PMEM包含了PCache和PSPR,DMEM同樣也包含了DCache和DSPR,為啥PEME要特殊對待,DSPR就不用呢?

從MTUTEST寄存器看沒有什么差別呀:

神奇,屬實神奇。?

差不多就到這,拜拜。

毛子整潔架構(分布式日志/Redis緩存/OutBox Pattern))

![[6-8] 編碼器接口測速 江協科技學習筆記(7個知識點)](http://pic.xiahunao.cn/[6-8] 編碼器接口測速 江協科技學習筆記(7個知識點))