參考:芯來科技發布最新NI系列內核,NI900矢量寬度可達512/1024位 (qq.com)

本土RISC-V CPU IP領軍企業——芯來科技正式發布首款針對人工智能應用的專用處理器產品線Nuclei Intelligence(NI)系列,以及NI系列的第一款AI專用RISC-V處理器CPU IP——NI900系列內核。

隨著Chatgpt的橫空出世,全球掀起一股AI的浪潮,從云端數據中心到邊緣側對AI的需求進一步提升。AI應用主要分布在訓練和推理,需要大量的并行計算和NPU來完成,更離不開高性能CPU的算力加持。CPU有著廣泛的普及性、兼容性、可擴展性和可靠性,并通過多核多節點進行串行計算、混合計算和安全防護等復雜任務;除此之外,CPU的通用矢量(Vector)指令集也可以提供強大且通用的并行計算能力,在AI領域進行高效的并行計算、前處理、后處理、激活函數等工作,更加靈活地處理GPU和NPU相對難以處理的復雜計算任務。

近期OpenAI發布的Sora模型將AI能夠理解和生成的內容模態從文字和圖片拓展到視頻,進一步證明基礎模型能力上限不斷被突破,想象空間被打開,對算力基礎設施的需求也遠沒有停止。芯來科技此次推出的NI900重點布局AI應用場景,助力本土芯片設計公司快速完成AI產品的設計。

NI900基于900系列處理器,針對“AI應用”進行了多項特性優化

Nuclei Intelligence —— NI900系列之于“AI應用”的優勢

NI900基于Nuclei成熟的900系列處理器,針對“AI應用”進行了多項特性優化

NI900主要特性如下:

- 基礎標量處理器:可以配置為900系列的RV32或RV64的任何一款——N900/U900/NX900/UX900

- RVV1.0 VPU:可配置基于RISC-V V Extension(RVV1.0 Vector指令集)的VPU單元,VPU的VLEN可配置為512b或者1024b

- 可配Per-Core-VPU:NI900支持Cluster內的每個Core均可以配置VPU

- 或可配多核共享Shared-VPU:NI900也可支持Cluster內的多個Core共享一份VPU單元

- NPU加速器:可通過NI900的IOCP(IO Coherent Port)與處理器緊耦合,實現對CPU內部Cache的一致性

- 用戶自定義指令擴展接口:用戶可以使用Nuclei的NICE硬件擴展接口,增加自己自定義的指令,包括Scalar或Vector指令

NI900支持RISC-V?Vector1.0標準

- 矢量擴展被稱之為RV指令集標準最重要的一組擴展,2015年發起,2021年正式生成標準。

- RVV 1.0支持的數據類型廣泛,運算類型豐富且可動態擴展,同一套指令可無修改適配各種微架構實現。

- RISC-V GCC從10.2版本已經支持RVV1.0指令,目前GCC13對應的intrinsic API接口已經升級到最新v0.12版本,且已部分支持自動向量化;預計GCC14正式發布,GCC的自動向量化會更加完備。RISC-V CLANG17版本也已支持最新v0.12版本intrinsic APl, 支持自動向量化。

- RISC-V Linux 6.5 版本開始支持RVV,其它各種計算庫及應用中間件都快速支持了RVV1.0。

- 有了RVV1.0標準和軟件生態的完備,為應對AI算力的需求,需要RISC-V CPU 在微架構設計上做更多有針對性的設計。

Nuclei 900系列基礎處理器

900系列處理器包括N900(32位)、U900(32位+MMU)、NX900(64位)和UX900(64位+MMU)四個產品系列,其中U900、UX900帶MMU可以運行重型操作系統,如Linux等。900系列非常適合對標ARM Cortex-M7、A7、R8、A35、A53、A55等內核,可應用于AIoT邊緣計算、數據中心、網絡設備和基帶通信等領域。

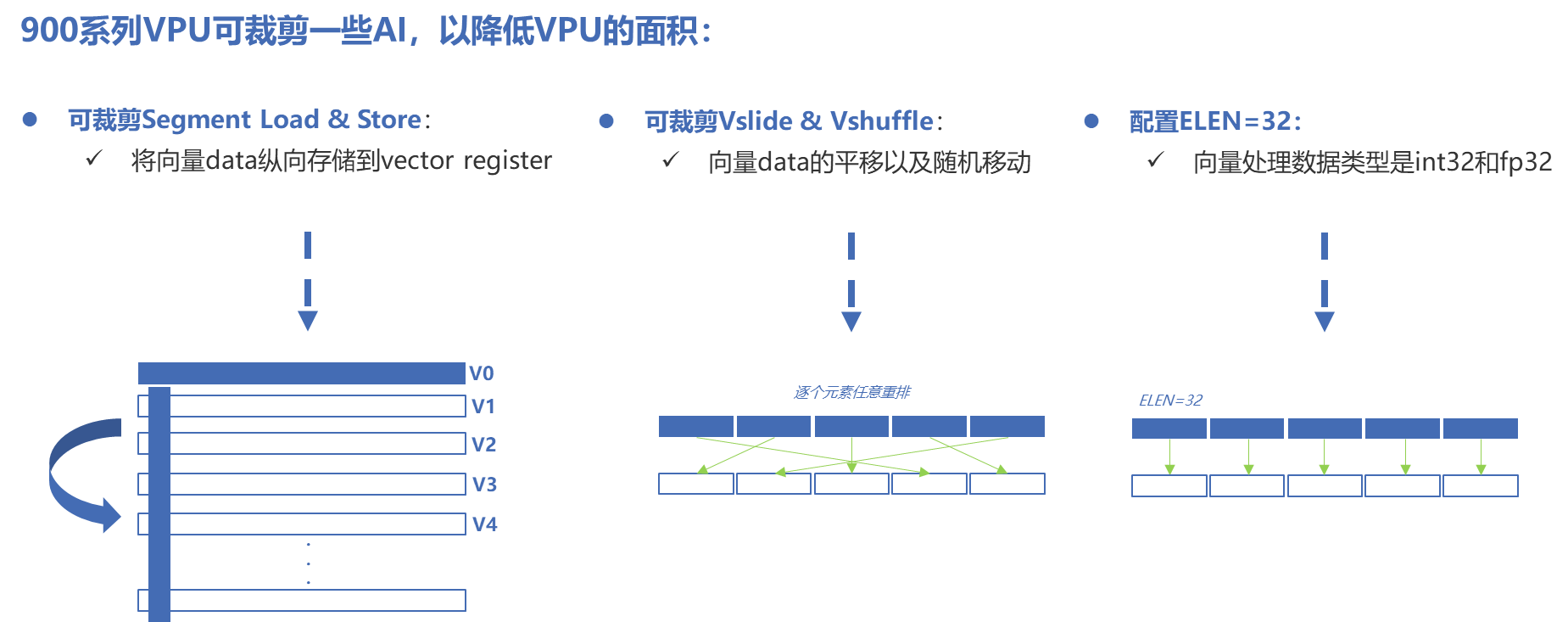

NI900的VPU可進行多種參數配置

參數描述

- VLEN:一個向量寄存器的總bit數(寬度)

- DLEN:內部運算單元能夠并行處理的一個向量元素的最大bit數

- ELEN:并行處理的數據類型的最大寬度,如果ELEN=32,則最大的處理數據類型是INT32和FP32

| 可配選項 | 參數值 |

| VLEN_512 | VLEN = 512, DLEN = 512,ELEN = 32/64 |

| VLEN_1024 | VLEN = 1024, DLEN = 1024,ELEN = 32/64 |

NI900的VPU特性與配置

VPU特性:

- Follow RISC-V V Extension (RVV1.0) instruction set with 32 Vector registers

- Dual vector arithmetic computing pipeline and one Load/Store pipeline

- Vector registers can be combined (LMUL) up to VLEN*8bits vector operations

- Full Vector Load/Store memory operations

- Support Vector Instruction Chaining

VPU支持數據類型:

- Data type: INT8/16/32, BFP16/FP16/FP32

- 如果ELEN等于64的配置則也支持INT64與FP64

900系列雙發射機制:

- Scalar標量部分:

- ALU指令,Ld/St指令,可以任意組合雙發射

- 乘除、浮點以及DSP指令無法進行雙發射,但是他們可以和ALU搭配進行雙發射

- CSR/WFE/WFI等特殊指令只能單發射

- Vector矢量部分:

- Vector Ld/St,Vector A類型和Vector B類型可以兩兩組合雙發射

- A類運算單元包含:

- vmul/vmac

- vfpu for single precesion

- B類運算單元包含:

- 除了上述A類指令和Vector Load Store指令之外的其他運算類型指令

- (可配置的)第二份vfpu vfadd/vfsub/vfmul/vfmac類型

- Example: Vector Ld/St + Vector A, Vector Ld/St + Vector B, Vector A + Vector B

- Scalar指令和Vector指令可以任意雙發射

- Example: Vector Ld/St +ALU

- Scalar流水線和Vector流水線可以亂序執行

- Scalar和Vector共享內存資源(DCache,DLM,External Memory等)

NI900的功耗——Dhrystone與矩陣運算示例

NI900的VPU與主Core的內存空間實現完全的Coherent

- VPU和Core LSU共享MMU資源?

- VPU并非獨立的協處理器,而是與主Core的內存空間實現完全的Coherent?

- Vector指令與普通Scalar一樣,支持虛擬地址訪問,使得NI900的Vector指令可以無縫運行與大型操作系統之上

- VPU和Core LSU共享Memory資源與通道?

- VPU擁有最高512b位寬訪問直接訪問DCache?

- VPU擁有最高1024b位寬訪問直接訪問DLM?

- DLM具備1024b的Slave Port供SoC訪問?

- 可單獨配置VLM port以進一步增加性能?

- VLM port可以直接連接到外部加速器或者內存??

- VLM port位寬=VLEN(目前支持最多1024b)?

- Scalar Core也可以通過Load Store訪問到VLM區間

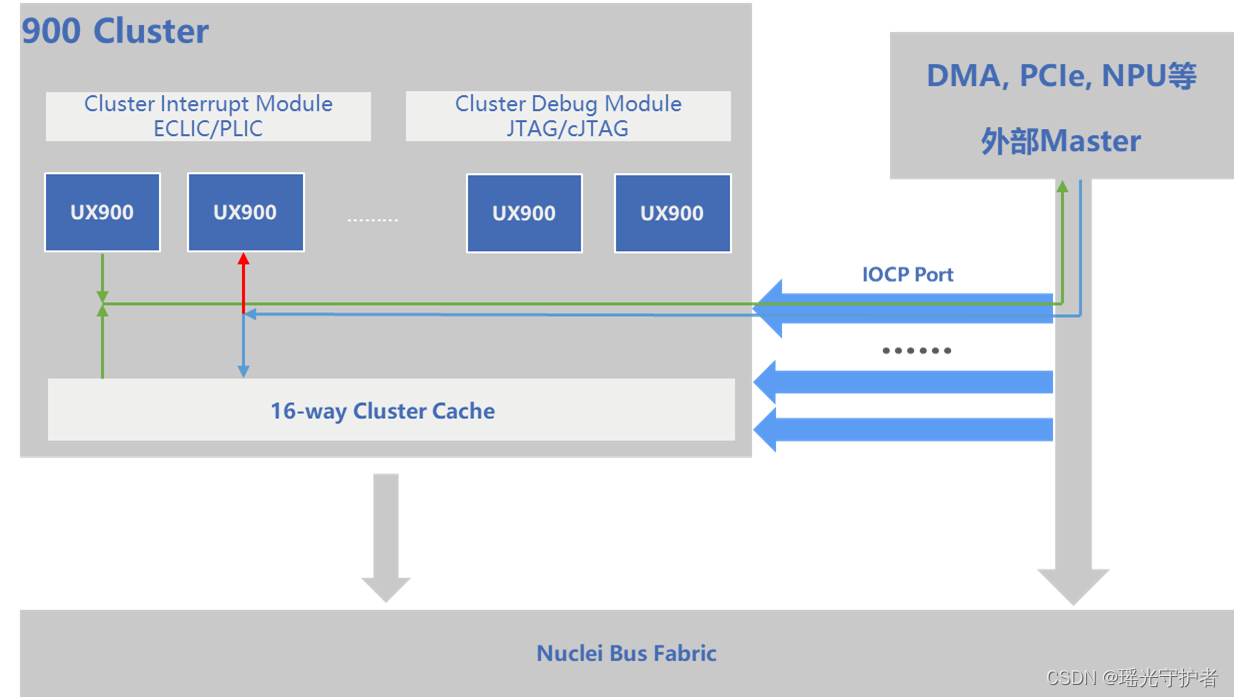

NI900的IOCP接口可用于連接硬件加速器單元

I/O Coherent Port (IOCP):

- 支持外部master和所有層級的緩存保持一致性?

- ????????從IOCP讀取:

- ????????????????從私有cache中獲取數據

- ????????????????如果cache miss則將從系統級緩存獲取數據

- ????????從IOCP寫入:

- ????????????????Invalidate所有私有緩存

- ????????????????寫入系統級緩存

- IOCP接口數量可以進行配置

- IOCP可以被DMA, PCIe, NPU等外部master使用

NI900的Scalar/Vector NICE自定義指令接口

NICE(Nuclei Instruction Co-unit Extension)是芯來CPU IP的一種用戶可擴展指令接口機制,允許用戶基于芯片的標準通用CPU內核定義自己的擴展指令集:

NICE(Nuclei Instruction Co-unit Extension)是芯來CPU IP的一種用戶可擴展指令接口機制,允許用戶基于芯片的標準通用CPU內核定義自己的擴展指令集:

- NI900提供用于Scalar指令擴展的NICE接口?

- 可支持單周期,多周期,流水線等不同指令類型

- NI900提供用于Vector指令擴展的NICE接口?

- 可支持單周期,多周期,流水線等不同指令類型

- NI900的NICE擴展單元不僅可以進行運算型的自定義指令擴展,還可以通過專用總線訪問Core的存儲資源(DCache等)實現與主Core的內存一致性?

- 總線位寬可以達到VLEN(最高1024b)

用戶可以結合自己的應用擴展自定義指令,將NI900處理器內核擴展成為面向AI領域進一步強化的專用處理器

NI900系列NICE示例 – 通過Vector NICE擴展其私有的訪存通路

圖例解釋如下:

- 可以通過Vector NICE機制擴展“用戶自定義的硬件單元”

- 該“硬件單元”可以擁有其私有的訪存通路,圖例中稱為VNP(Vector Nice Port)

- 外部可以有一個多Banks或多Ports的Memory模塊

- 該VNP Port可以直接接到外部的Memory模塊

- Core的VLM Port也可以直接接到外部的Memory模塊

- 來自系統內其他AI加速器的讀寫Port也可以直接接到外部的Memory模塊

- 用戶可以在該“硬件單元”中擴展一條VNP_Load指令

- 該VPN_Load指令可以從VNP Port批量讀出數據寫入標準Vector Regfile

- 可以使用標量寄存器rs1作為基地址, Vector寄存器作為結果寄存器

- 用戶可以在該“硬件單元”中擴展一條VNP_Store指令

- 該VNP_Store指令可以將標準Vector Regfile中的數據批量寫出VNP Port

- 可以使用標量寄存器rs1作為基地址, Vector寄存器作為源操作數寄存器

- 標準的VLoad/Store指令和VNP_Load/Store可以同時并行訪問,如下列偽代碼程序序列所示

- VLoad V7~V0 mem[VLM] #從VLM地址區間讀數據寫入V0到V7八個Vector Registers

- VEXU V15~V8,V7~V0,rs1 #對V0到V7八個Vector Registers的數據進行Vector計算,結果寫入V8到V15八個Vector Registers

- VNP_Store V15~V8 mem[VNP] #將V8到V15八個Vector Registers寫出VNP地址區間

)

)

)

)