**前言:**前面從理論角度出發學習了時序分析的基本原理,本篇從設計的角度學習如何合理添加時鐘約束。

文章目錄

- 一、基準時鐘(base clock)和生成時鐘(generate clock)

- 二、基準時鐘的約束

- 1.完成綜合(run implementation)

- 2.進行基準時鐘約束(edit timing constrains)

- 三、查看時序約束的結果

- 四、生成時鐘約束

- 五、虛擬時鐘約束

- 六、時序約束前后的時序報告:

一、基準時鐘(base clock)和生成時鐘(generate clock)

這里以前面做過的千兆以太網 HDMI 項目時鐘樹為例:

基準時鐘為 sclkin,其余通過 PLL 的生成的時鐘是生成時鐘(generate clk)。

Vivado 約束基準時鐘和生成時鐘規則:

- 如果基準時鐘輸入給 PLL,由于在 PLL 配置界面設置了基準時鐘頻率等信息,所以不需要額外再次約束基準時鐘。在約束信息里會自動添加基準時鐘約束,并且自動會把生成時鐘也會添加約束。

- 如果基準時鐘并沒有送入 PLL 直接通過分頻或者不分頻的方式給內部模塊使用就需要添加基準時鐘約束和生成時鐘約束。

二、基準時鐘的約束

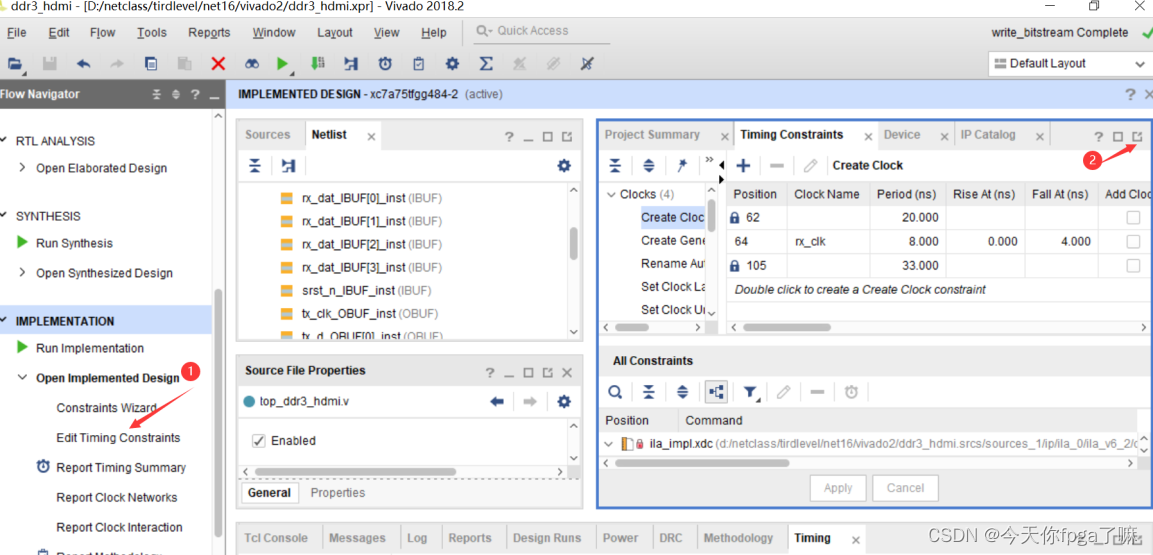

1.完成綜合(run implementation)

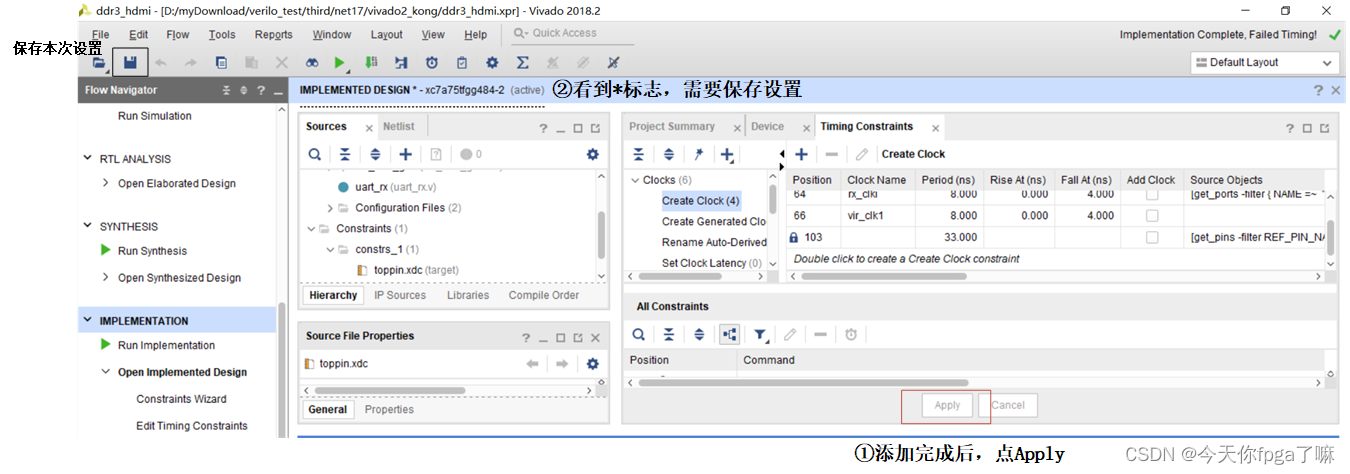

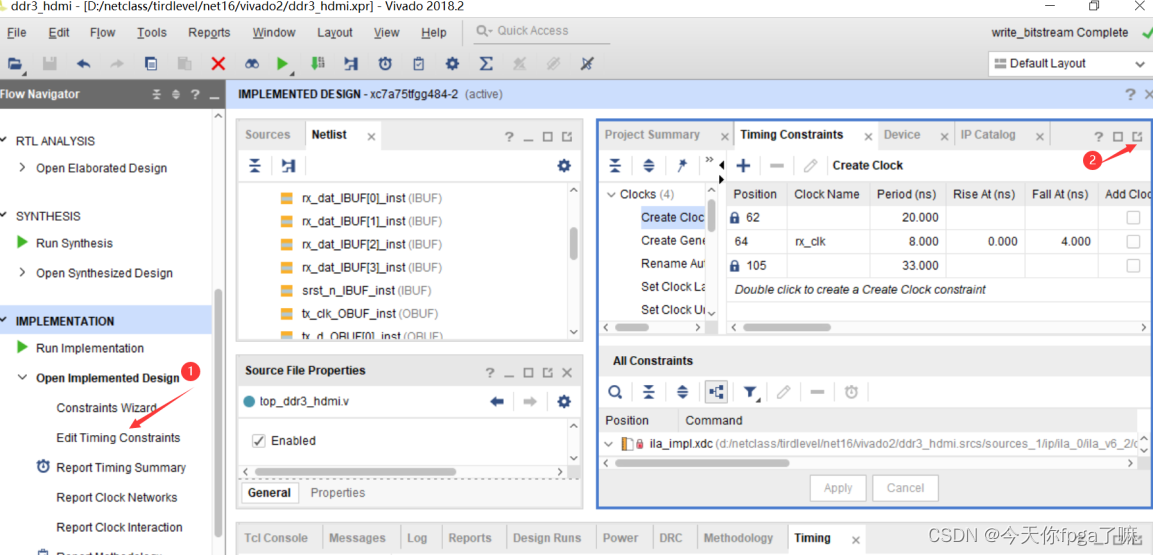

2.進行基準時鐘約束(edit timing constrains)

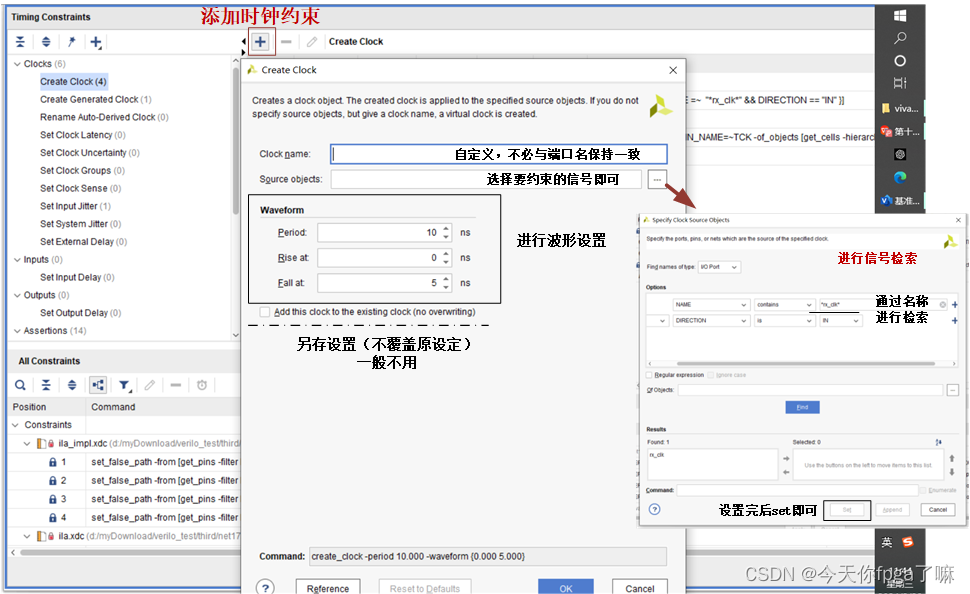

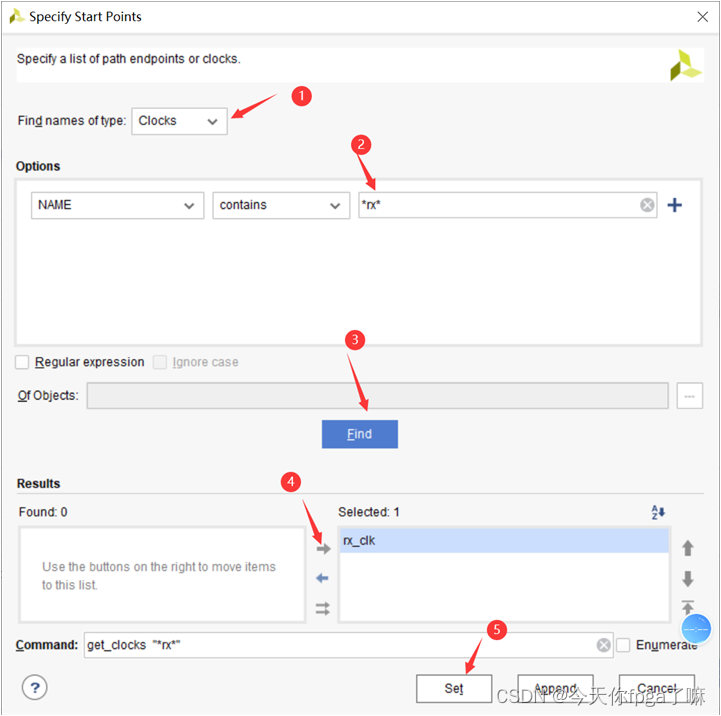

① 在creat clock選項下添加基準時鐘(rx_clki),并進行具體參數設置

② 查看時鐘添加情況

具體信息如下:

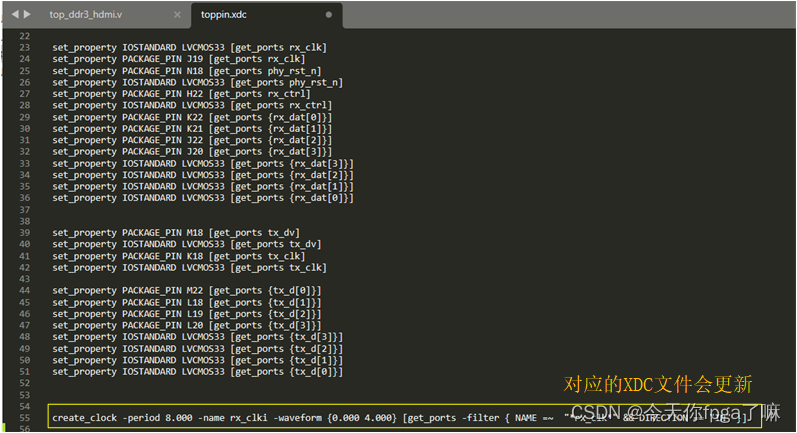

③ 保存本次設置,并自動更新到xdc文件中

約束了基準時鐘之后,關于這個時鐘的時序分析結果就有了。

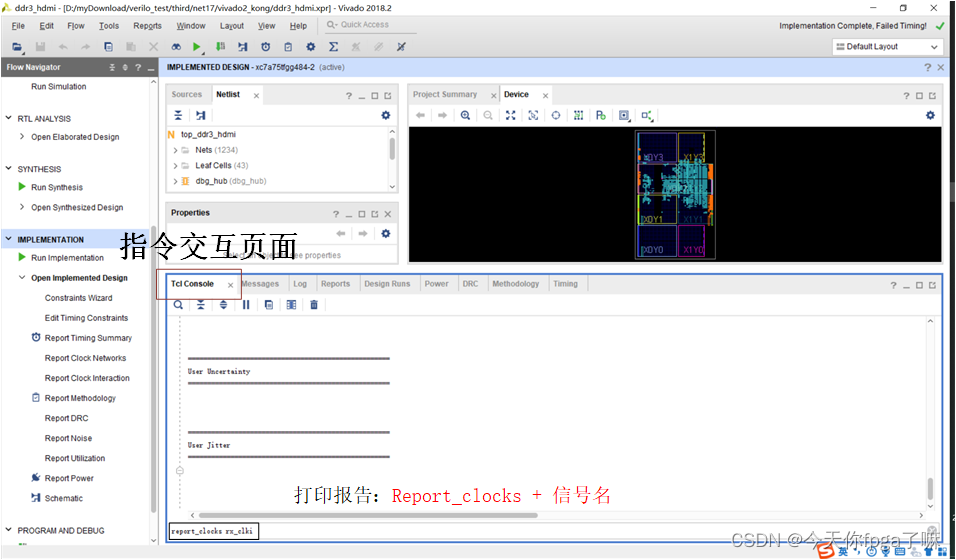

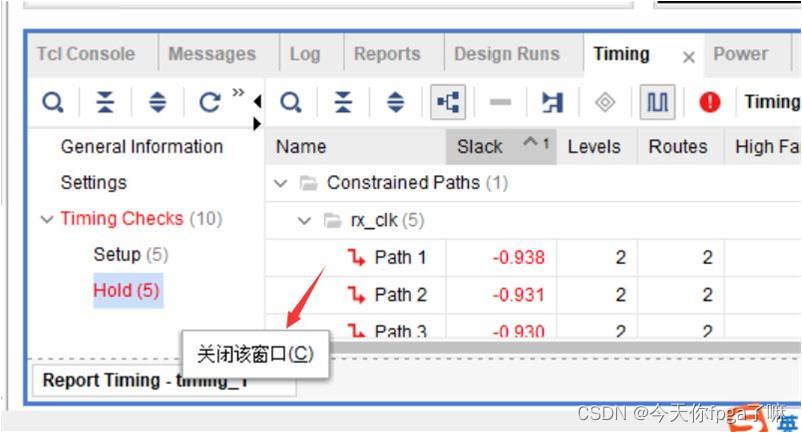

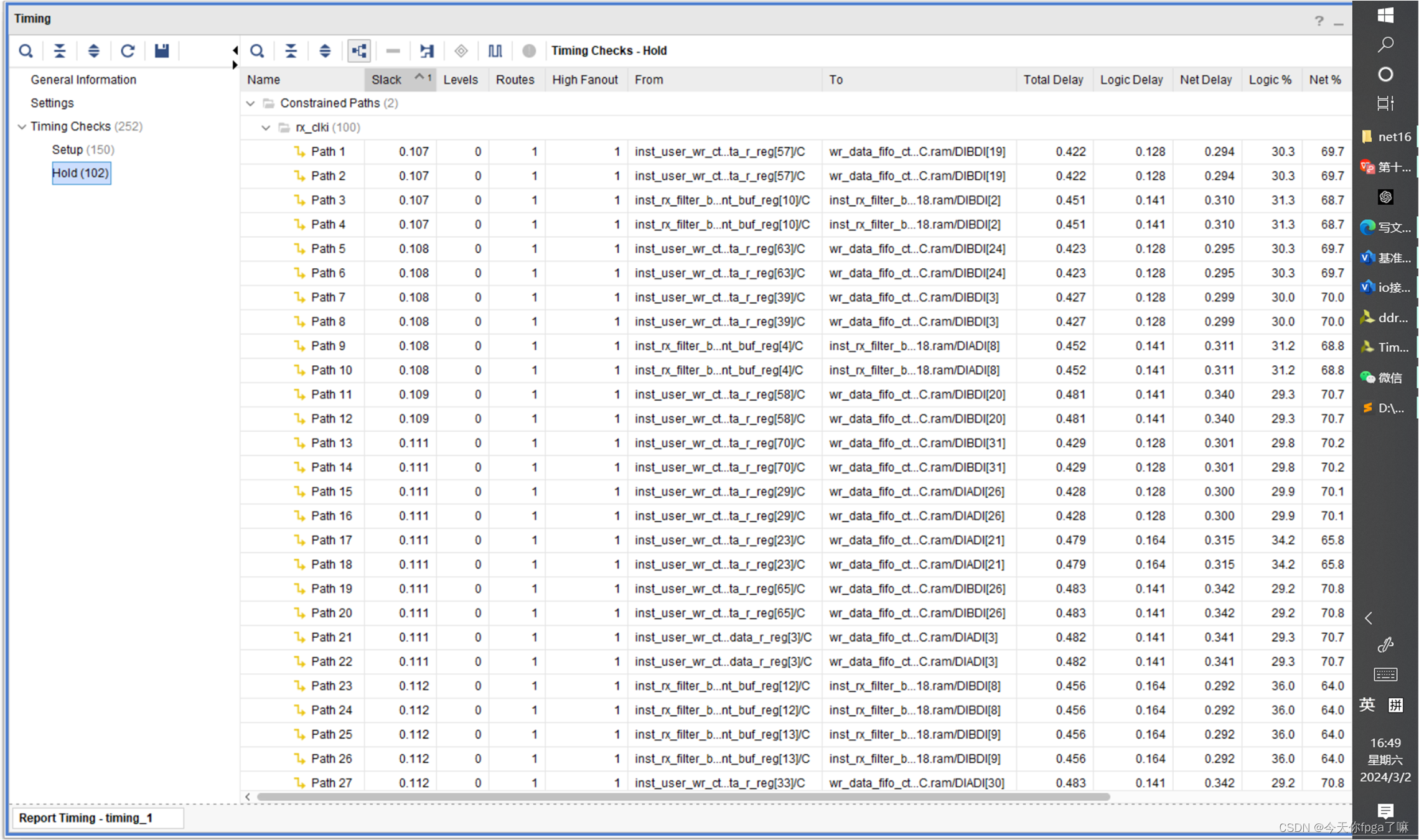

三、查看時序約束的結果

① 關閉當前時序信息

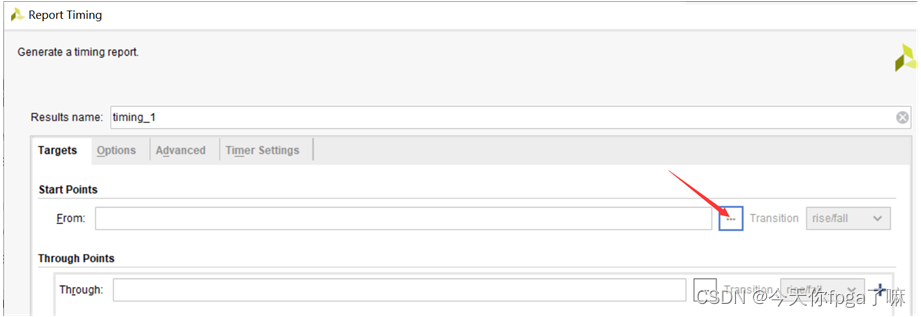

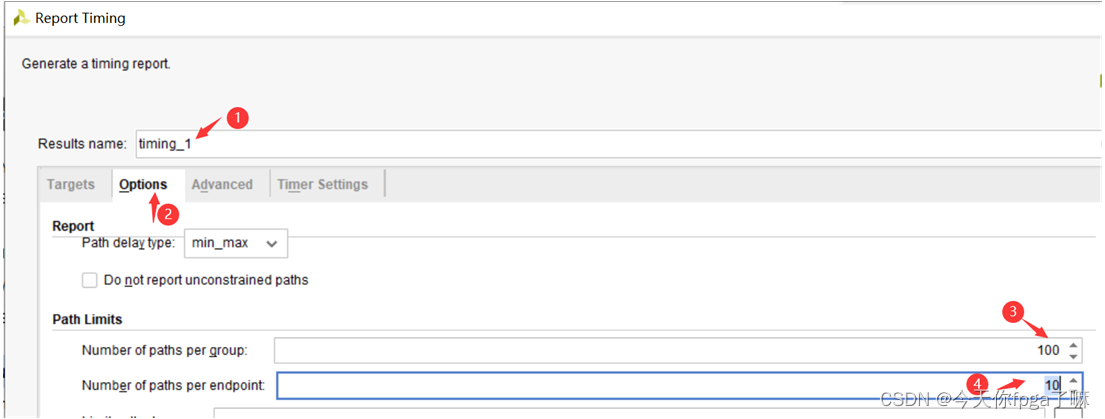

② 點擊report timing,并設置打印時序報告參數

設置 option 中的觀察時序路徑條數和每個路徑打印多少條信息,然后點擊 OK 完成打印

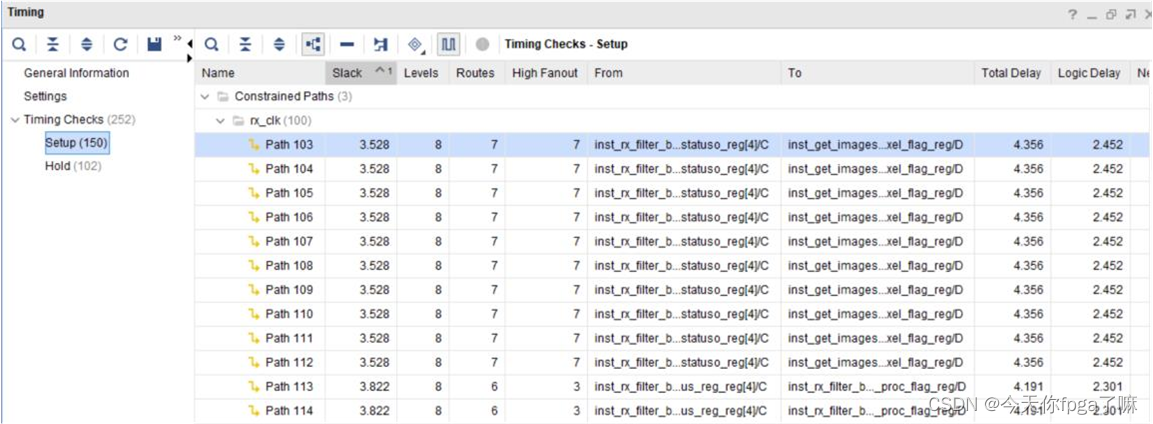

③ 報告信息如下(沒有出現紅色說明都是時序滿足建立時間要求的)

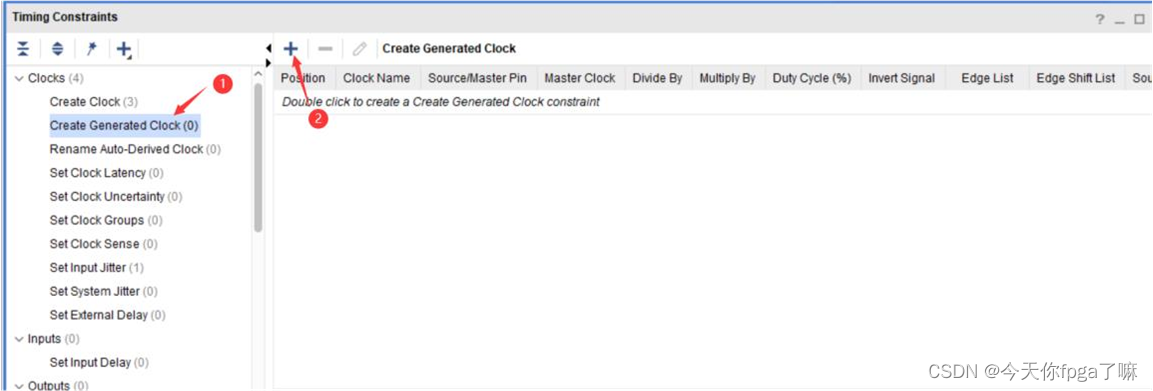

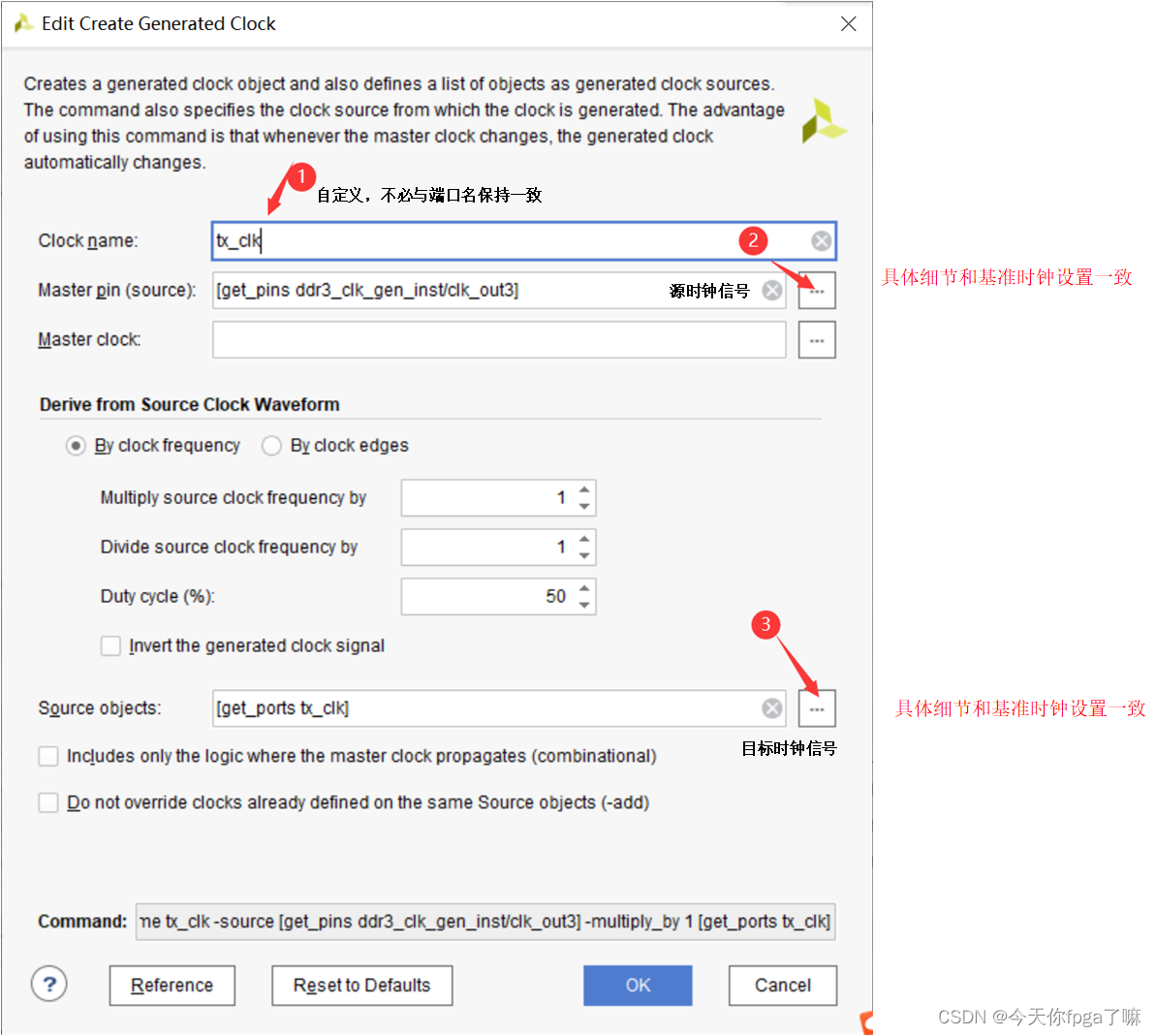

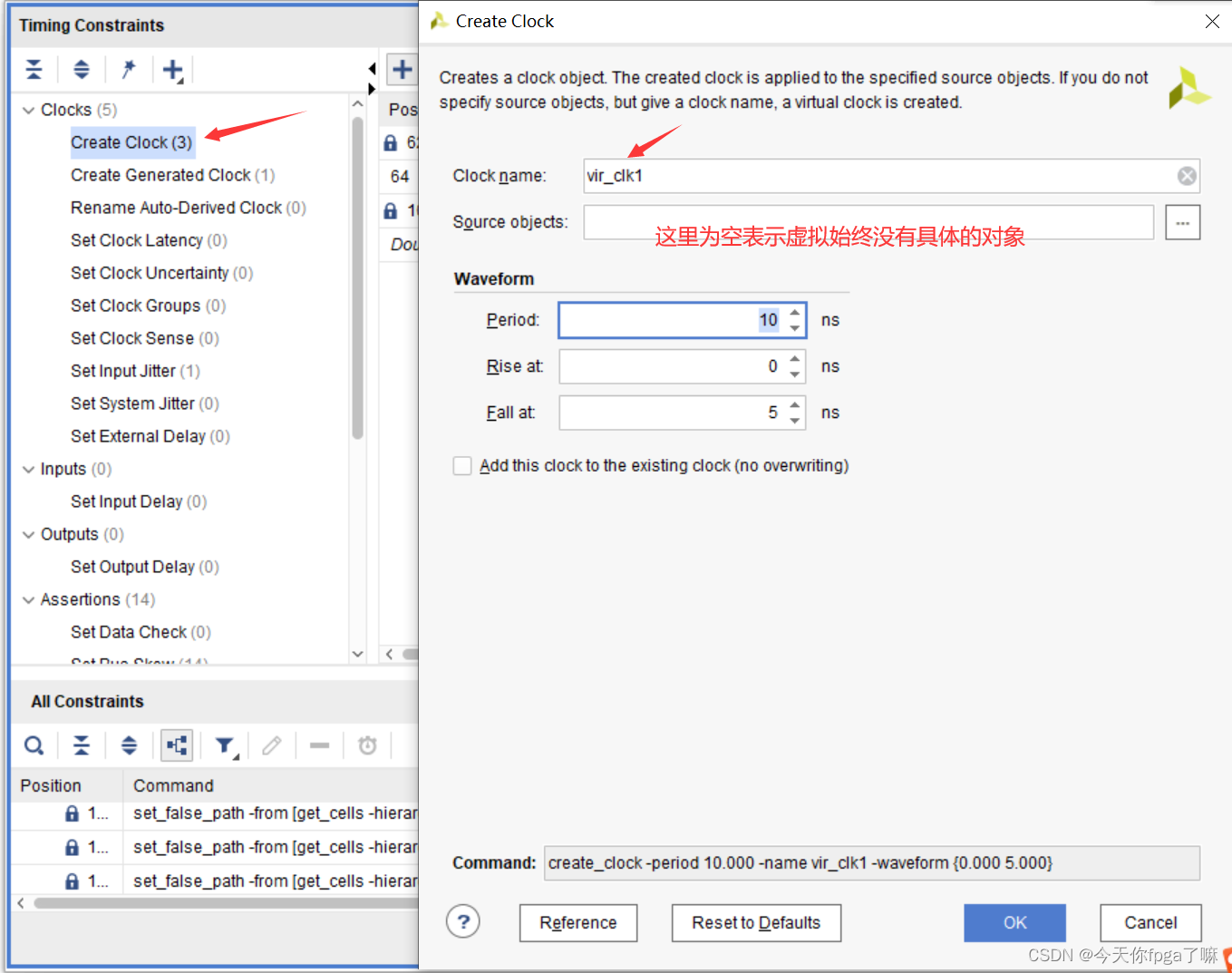

四、生成時鐘約束

① 在create generated clock選項下添加生成時鐘(源時鐘:clk_out3,目標時鐘:tx_clk),并進行具體參數設置

② 查看時鐘添加情況并保存(此步驟和生成時鐘步驟一樣)

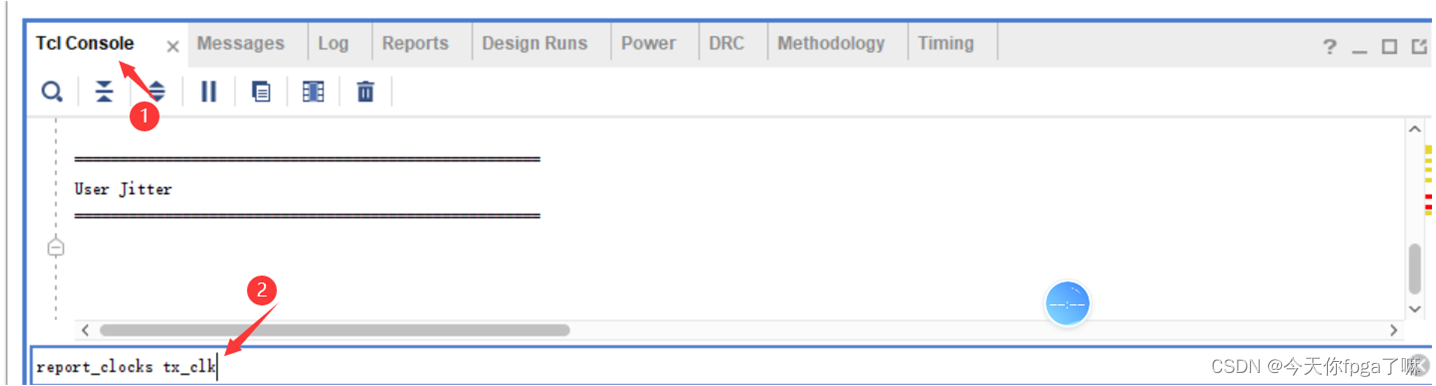

五、虛擬時鐘約束

本次案例并沒有用到,一般會在系統同步中使用(該技術目前被淘汰了,了解即可)

什么是虛擬時鐘?

答:就是在 fpga 內部不存在的時鐘,這個時鐘主要來輔助做一些分析,比如系統同步時晶振這個時鐘給源端的時鐘;

創建虛擬時鐘的方法很簡單,就是創建一個時鐘但是不實際指向一個 fpga 內部或者 IO 上的對象。

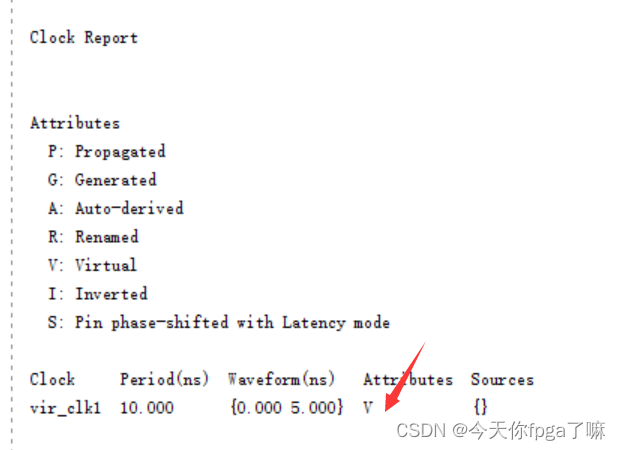

①在 create clock 中添加一個虛擬時鐘(vir_clk1)

② 查看時鐘添加情況并保存(此步驟和生成時鐘步驟一樣)

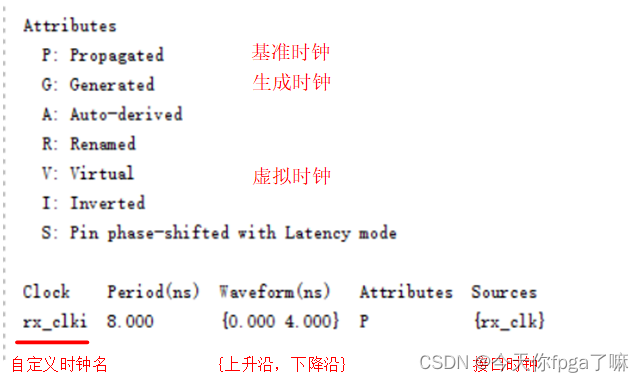

打印信息如下:

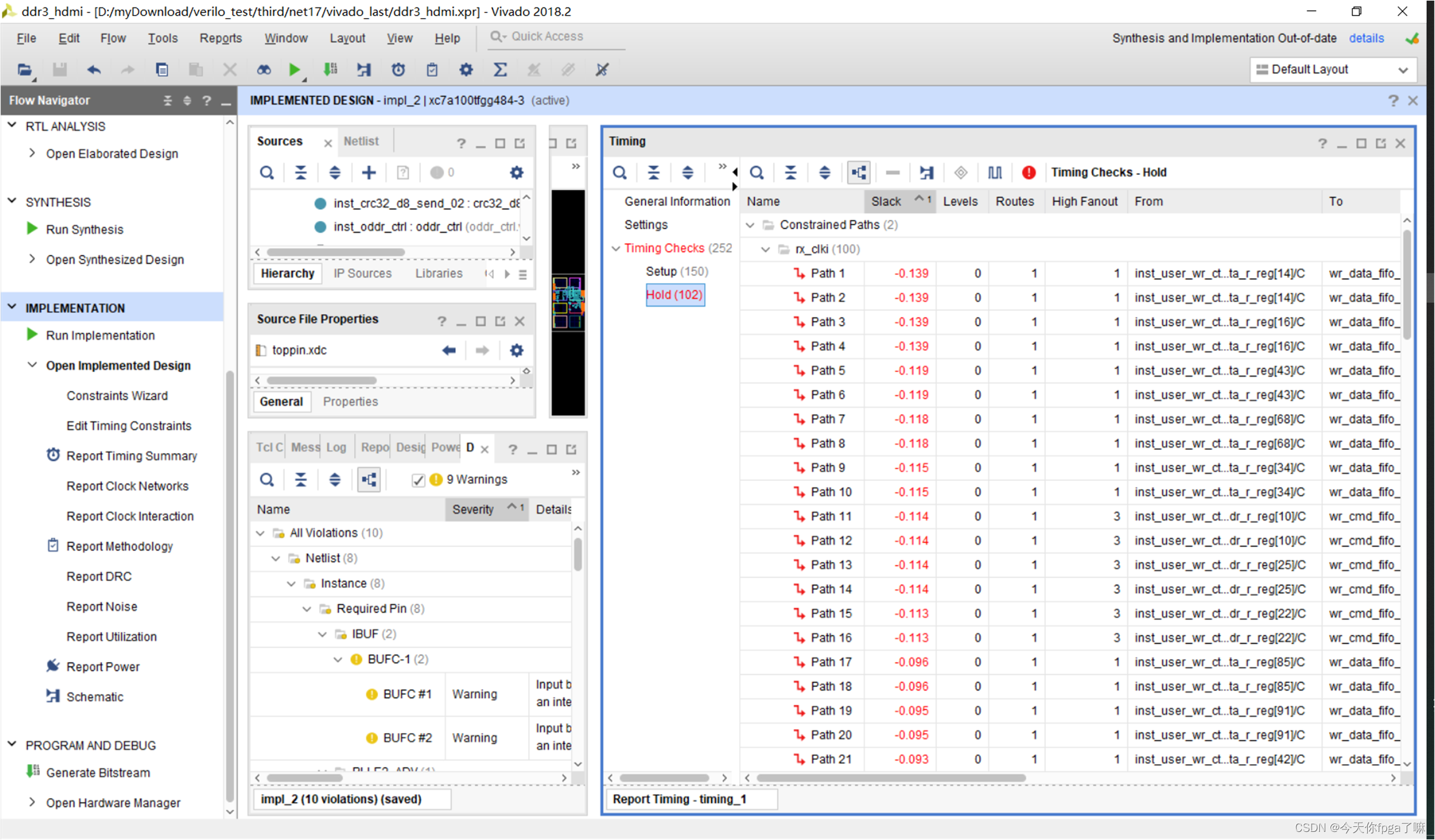

六、時序約束前后的時序報告:

時序約束前:

時序約束后:

)

——堆排序)

)

)

)

)

)

![LeetCode 刷題 [C++] 第347題.前 K 個高頻元素](http://pic.xiahunao.cn/LeetCode 刷題 [C++] 第347題.前 K 個高頻元素)