?往期博文

低密度奇偶校驗碼LDPC(一)——概述_什么是gallager構造-CSDN博客

低密度奇偶校驗碼LDPC(二)——LDPC編碼方法-CSDN博客

低密度奇偶校驗碼LDPC(三)——QC-LDPC碼概述-CSDN博客

低密度奇偶校驗碼LDPC(四)——雙對角線結構的QC-LDPC編碼-CSDN博客

低密度奇偶校驗碼LDPC(五)——譯碼算法概述-CSDN博客

低密度奇偶校驗碼LDPC(六)——SPA和積譯碼算法-CSDN博客

低密度奇偶校驗碼LDPC(七)——SPA和積譯碼算法的簡化-CSDN博客

QC-LDPC的FPGA實現

基于QC-LDPC編碼的循環移位網絡的FPGA實現_5g ldpc編碼 桶形移位寄存器-CSDN博客

?一、譯碼器的FPGA架構設計

?

?

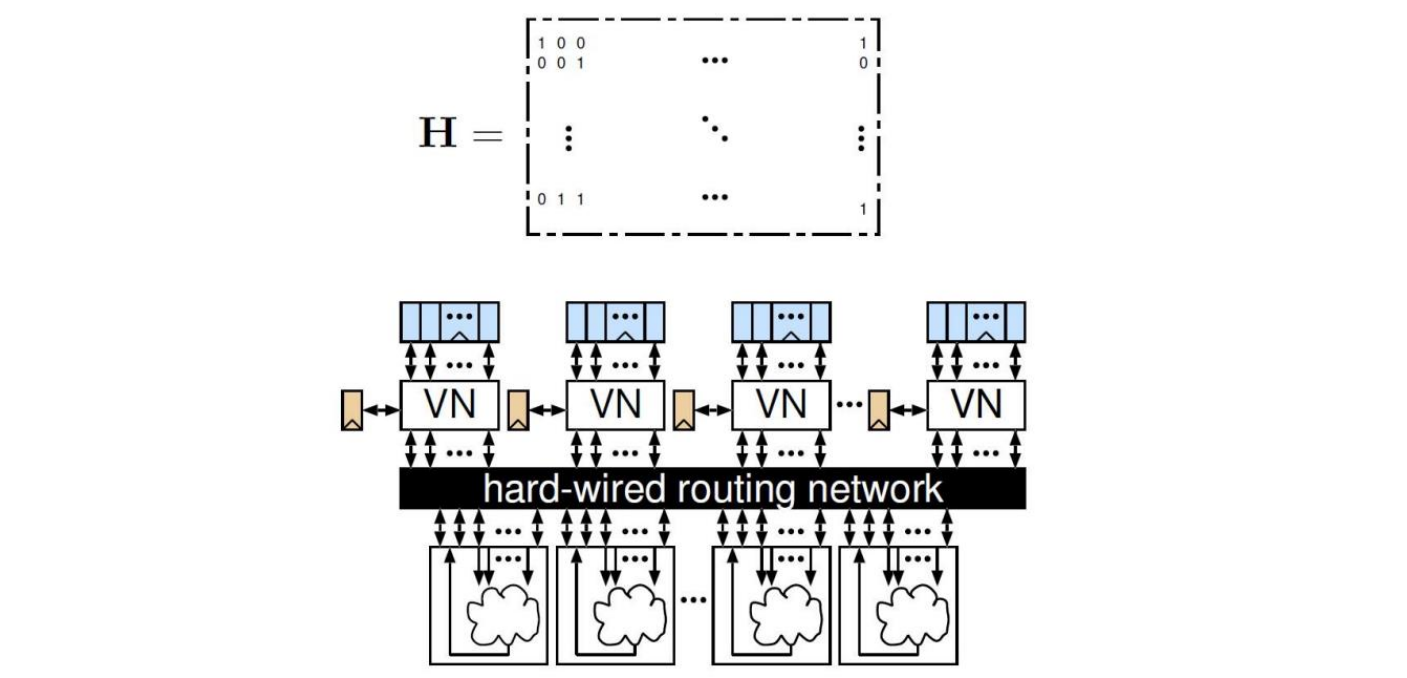

全并行(Full-Parallel Architectures)

?

? ?

?

?

?

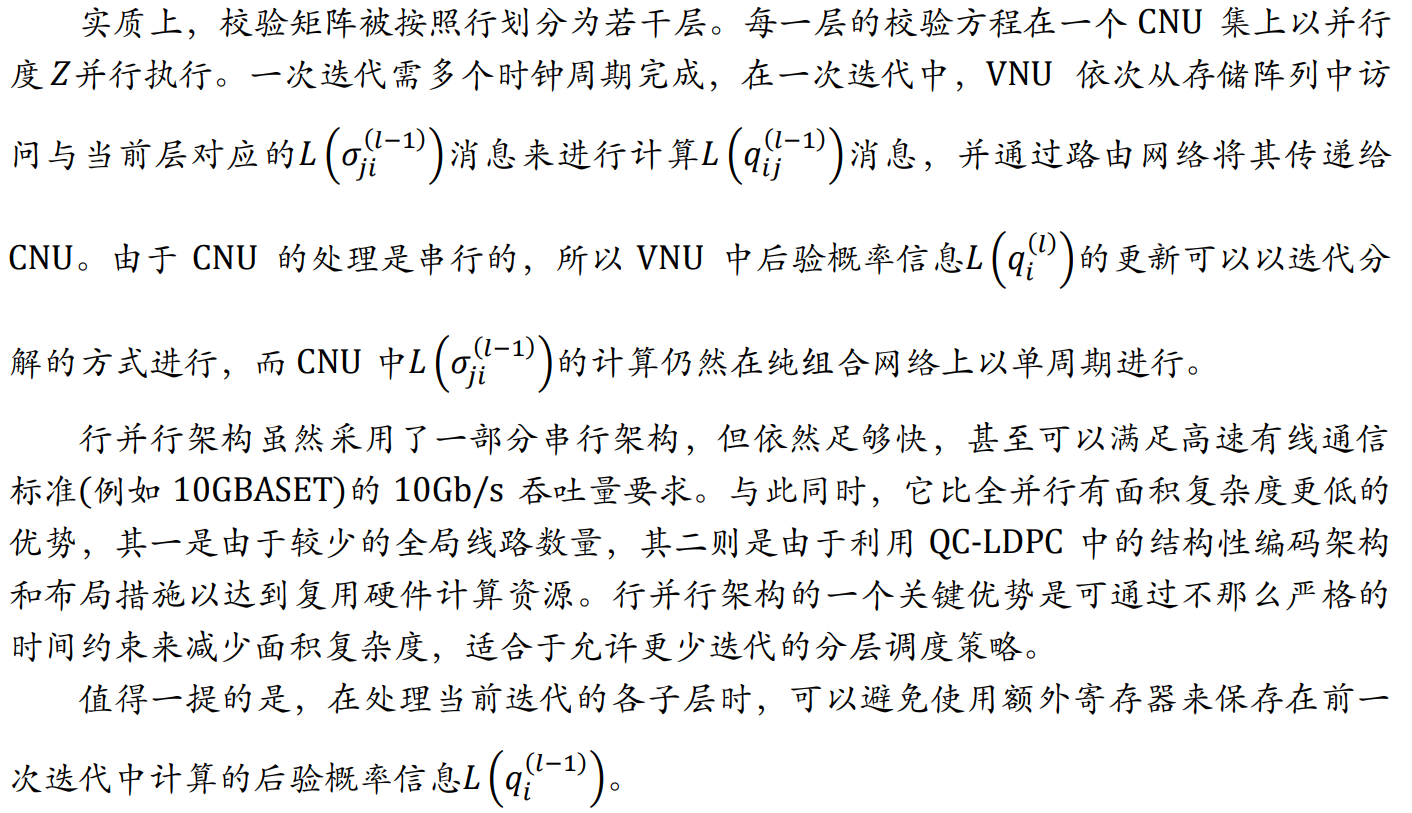

行并行(Row-Parallel Architectures)

?

? ?

? ?

?

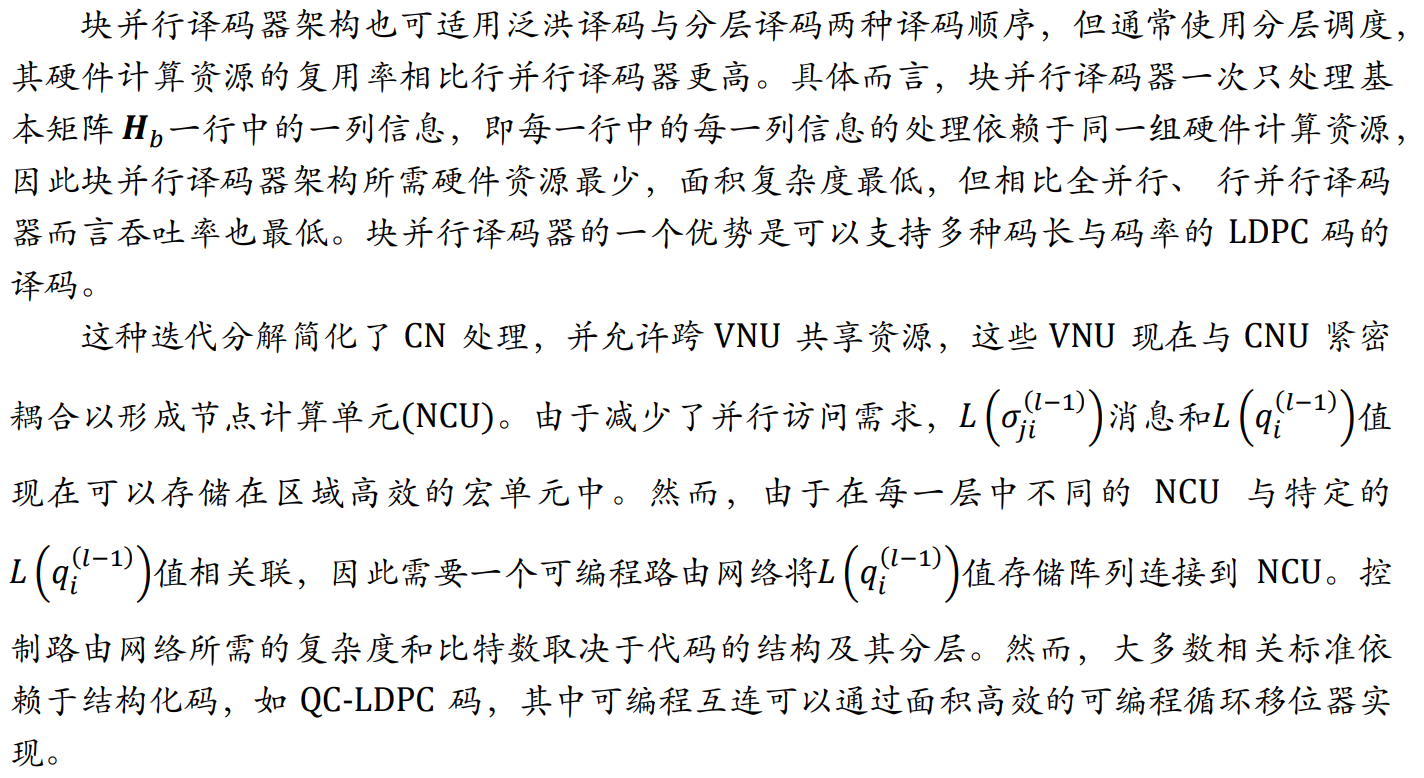

塊并行(Block-Parallel Architectures)

?

? ?

? ?

?

參考文獻

[1] 白寶明 孫韶輝 王加慶. 5G 移動通信中的信道編碼[M]. 北京: 電子工業出版社, 2018.

[2] William E. Ryan, Shu Lin. Channel Codes - Classical and Modern[M]. Cambridge University Press, 2009.

[3] Roth C, Cevrero A, Studer C, et al. Area, throughput, and energy-efficiency trade-offs in the VLSI implementation of LDPC decoders[C]// IEEE International Symposium of Circuits and Systems (ISCAS). 2011: 1772-1775.

[4] 鐘志偉. 面向5G編譯碼的硬件設計研究[C]. 南京: 東南大學, 2020.

)

![LeetCode 刷題 [C++] 第215題.數組中的第K個最大元素](http://pic.xiahunao.cn/LeetCode 刷題 [C++] 第215題.數組中的第K個最大元素)

-4)

——代碼隨想錄算法訓練營Day48)