????????????????????????????????????????????????????????????????????????????整理 :李肖遙

本文目錄

前言

狀態機簡介

狀態機分類

Mealy 型狀態機

Moore 型狀態機狀態機描述

一段式狀態機

二段式狀態機

三段式狀態機狀態機優缺點

總結

擴展-四段式狀態機

01. 前言

狀態機是FPGA設計中一種非常重要、非常根基的設計思想,堪稱FPGA的靈魂,貫穿FPGA設計的始終。

02. 狀態機簡介

什么是狀態機:狀態機通過不同的狀態遷移來完成特定的邏輯操作(時序操作)狀態機是許多數字系統的核心部件, 是一類重要的時序邏輯電路。通常包括三個部分:

下一個狀態的邏輯電路

存儲狀態機當前狀態的時序邏輯電路

輸出組合邏輯電路

03. 狀態機分類

通常, 狀態機的狀態數量有限, 稱為有限狀態機(FSM) 。由于狀態機所有觸發器的時鐘由同一脈沖邊沿觸發, 故也稱之為同步狀態機。

根據狀態機的輸出信號是否與電路的輸入有關分為 Mealy 型狀態機和 Moore 型狀態機

3.1,Mealy 型狀態機

電路的輸出信號不僅與電路當前狀態有關, 還與電路的輸入有關

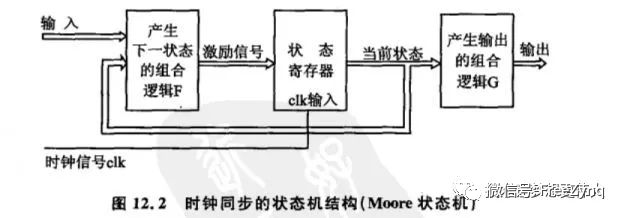

3.2,Moore 型狀態機

電路的輸出僅僅與各觸發器的狀態, 不受電路輸入信號影響或無輸入

狀態機的狀態轉移圖, 通常也可根據輸入和內部條件畫出。一般來說, 狀態機的設計包含下列設計步驟:

根據需求和設計原則, 確定是 Moore 型還是 Mealy 型狀態機;

分析狀態機的所有狀態, 對每一狀態選擇合適的編碼方式, 進行編碼;

根據狀態轉移關系和輸出繪出狀態轉移圖;

構建合適的狀態機結構, 對狀態機進行硬件描述。

04. 狀態機描述

狀態機的描述通常有三種方法, 稱為一段式狀態機, 二段式狀態機和三段式狀態機。

狀態機的描述通常包含以下四部分:

利用參數定義語句 parameter 描述狀態機各個狀態名稱, 即狀態編碼。狀態編碼通常有很多方法包含自然二進制編碼, One-hot 編碼,格雷編碼碼等;

用時序的 always 塊描述狀態觸發器實現狀態存儲;

使用敏感表和 case 語句(也采用 if-else 等價語句) 描述狀態轉換邏輯;

描述狀態機的輸出邏輯。

下面根據狀態機的三種方法來具體說明

4.1,一段式狀態機

1module?detect_1(

2input?clk_i,

3input?rst_n_i,

4output?out_o

5);

6reg?out_r;

7//狀態聲明和狀態編碼

8reg?[1:0]?state;

9parameter?[1:0]?S0=2'b00;10parameter?[1:0]?S1=2'b01;

11parameter?[1:0]?S2=2'b10;12parameter?[1:0]?S3=2'b11;

13always@(posedge?clk_i)

14begin

15??if(!rst_n_i)begin

16????state<=0;

17????out_r<=1'b0;18??end19??else20????case(state)21??????S0?:22??????begin23????????out_r<=1'b0;

24????????state<=?S1;

25??????end

26??????S1?:

27??????begin

28????????out_r<=1'b1;29????????state<=?S2;30??????end31??????S2?:32??????begin33????????out_r<=1'b0;

34????????state<=?S3;

35??????end

36??????S3?:

37????????begin

38????????out_r<=1'b1;39??????end40????endcase41end42assign?out_o=out_r;43endmodul44

一段式狀態機是應該避免使用的, 該寫法僅僅適用于非常簡單的狀態機設計。

4.2,兩段式狀態機

1module?detect_2( 2????input?clk_i, 3????input?rst_n_i, 4????output?out_o 5??); 6??reg?out_r; 7??//狀態聲明和狀態編碼 8??reg?[1:0]?Current_state; 9??reg?[1:0]?Next_state;10??parameter?[1:0]?S0=2'b00;11??parameter?[1:0]?S1=2'b01;12??parameter?[1:0]?S2=2'b10;13??parameter?[1:0]?S3=2'b11;14??//時序邏輯:?描述狀態轉換15??always@(posedge?clk_i)16??begin17????if(!rst_n_i)18??????Current_state<=0;19????else20??????Current_state<=Next_state;21??end22??//組合邏輯:描述下一狀態和輸出23??always@(*)24??begin25????out_r=1'b0;26????case(Current_state)27??????S0?:28????????begin29??????????out_r=1'b0;30??????????Next_state=?S1;31????????end32??????S1?:33????????begin34??????????out_r=1'b1;35??????????Next_state=?S2;36????????end37??????S2?:38????????begin39??????????out_r=1'b0;40??????????Next_state=?S3;41????????end42??????S3?:43????????begin44??????????out_r=1'b1;45??????????Next_state= S0;46????????end47????endcase48??end49??assign?out_o?=?out_r;50endmodule51

兩段式狀態機采用兩個 always 模塊實現狀態機的功能, 其中一個 always 采用同步時序邏輯描述狀態轉移, 另一個 always 采用組合邏輯來判斷狀態條件轉移。

4.3,三段式狀態機

1module?detect_3(

2????input?clk_i,

3????input?rst_n_i,

4????output?out_o

5??);

6??reg?out_r;

7??//狀態聲明和狀態編碼

8??reg?[1:0]?Current_state;

9??reg?[1:0]?Next_state;

10??parameter?[1:0]?S0=2'b00;11??parameter?[1:0]?S1=2'b01;

12??parameter?[1:0]?S2=2'b10;13??parameter?[1:0]?S3=2'b11;

14??//時序邏輯:?描述狀態轉換

15??always@(posedge?clk_i)

16??begin

17????if(!rst_n_i)

18??????Current_state<=0;

19????else

20??????Current_state<=Next_state;

21??end

22??//組合邏輯:?描述下一狀態

23??always@(*)

24??begin

25????case(Current_state)

26??????S0:

27????????Next_state?=?S1;

28??????S1:

29????????Next_state?=?S2;

30??????S2:

31????????Next_state?=?S3;

32??????S3:

33????????begin

34??????????Next_state?=?S0;

35????????end

36??????default?:

37??????Next_state?=?S0;

38????endcase

39??end

40??//輸出邏輯:?讓輸出 out,?經過寄存器 out_r 鎖存后輸出,?消除毛刺

41??always@(posedge?clk_i)

42??begin

43????if(!rst_n_i)

44??????out_r<=1'b0;45????else46??????begin47????????case(Current_state)48??????????S0,S2:49????????????out_r<=1'b0;

50??????????S1,S3:

51????????????out_r<=1'b1;52??????????default?:53????????????out_r<=out_r;54????????endcase55??????end56??end5758??assign?out_o=out_r;59endmodule60

三段式狀態機在第一個 always 模塊采用同步時序邏輯方式描述狀態轉移, 第二個always 模塊采用組合邏輯方式描述狀態轉移規律, 第三個 always 描述電路的輸出。通常讓輸出信號經過寄存器緩存之后再輸出, 消除電路毛刺。

05. 狀態機優缺點

1、一段式狀態機

只涉及時序電路,沒有競爭與冒險,同時消耗邏輯比較少。

但是如果狀態非常多,一段式狀態機顯得比較臃腫,不利于維護。

2、兩段式狀態機

當一個模塊采用時序(狀態轉移),一個模塊采用組合時候(狀態機輸出),組合邏輯電路容易造成競爭與冒險;當兩個模塊都采用時序,可以避免競爭與冒險的存在,但是整個狀態機的時序上會延時一個周期。

兩段式狀態機是推薦的狀態機設計方法。

3、三段式狀態機

狀態機輸出采用了同步寄存器輸出,也可以避免組合邏輯電路的競爭與冒險。并且在狀態機的采用這種組合邏輯電路+次態寄存器輸出,避免了兩段式狀態機的延時一個周期(三段式狀態機在上一狀態中根據輸入條件判斷當前狀態的輸出,從而在不插入額外時鐘節拍的前提下,實現寄存器的輸出)。

三段式狀態機也是比較推崇的,主要是由于維護方便, 組合邏輯與時序邏輯完全獨立。

06. 總結

靈活選擇狀態機,不一定要拘泥理論,怎樣方便怎樣來

07.擴展

四段式不是指三個always代碼,而是四段程序。使用四段式的寫法,可參照明德揚GVIM特色指令Ztj產生的狀態機模板。

明·德·揚四段式狀態機符合一次只考慮一個因素的設計理念。

第一段代碼,照抄格式,完全不用想其他的。

第二段代碼,只考慮狀態之間的跳轉,也就是說各個狀態機之間跳轉關系。

第三段代碼,只考慮跳轉條件。

第四段,每個信號逐個設計。

有興趣的話可以自己去學習一下,或者http://www.mdyedu.com/product/299.html自行看視頻。

??????????????????END??????????????????點擊【閱讀原文】可轉到IC技術圈,獲取更多知識分享

有什么作用?)

安全性)

:java調用tess4j識別圖像文字)

)

--啟蒙篇《MYSQL必知必會》)

)