verilog典型電路設計之流水線結構

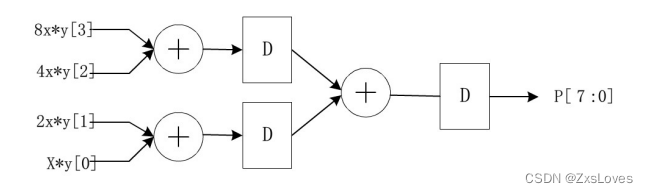

下圖是一個4位的乘法器結構,用verilog HDL 設計一個兩級流水線加法器樹4位乘法器

對于流水線結構 其實需要做的是在每級之間增加一個暫存的數據用來存儲 我們得到的東西 我們一般來說會通過在每一級之間插入D觸發器來保證數據的聯通

通過在第一級和第二級,第二級和第三級加法器之間插入D觸發器組,可以實現兩級流水設計。

reg類型其實是用在always塊中所以我們在其中引入always塊 來保證reg 的使用

下面是兩級 流水線的簡單代碼

module mul_addtree_2_stage(clk,clr,mul_a,mul_b,mul_out);input clk,clr;

input [3:0] mul_a,mul_b;

output [7:0] mul_out;

reg[7:0] add_tmp_1,add_tmp_2,mul_out;

wire [7:0] stored0,stored1,stored2,stored3;

assign

stored3=mul_b[3]?{1'b0,mul_a,3'b0}:8'b0;

assign

stored2=mul_b[2]?{2'b0,mul_a,2'b0}:8'b0;

assign stored1=mul_b[1]?{3'b0,mul_a,1'b0}:8'b0;

assign stored0=mul_b[0]?{4'b0,mul_a}:8'b0;

always@(posedge clk or negedge clr)

if(!clr) begin

add_tmp_1<=8'b0000_0000;

add_tmp_2<=8'b0000_0000;

mul_out<=8'b0000_0000;

end

else begin

add_tmp_1<=stored3+stored2;

add_tmp_2<=stored1+stored0;

mul_out<=add_tmp_1+add_tmp_2;

end

end

endmodule

下面是流水線結構的testbench

module mult addtree_2_stag_tb;

reg clk, clr;

reg [3:0]mult_a, mult b;

wire [7:0]mult_out;

mul_addtree_2_stage

U1(.mul_a(mult_a),..mul_b(mult_b),

.mul_out(mult_out),.clk(clk),.clr(clr));

initial

begin

clk=0; clr=0; mult_a=1; mult_b=1;

#5 clr=1;

end

always #10 clk=~clk;

initial

begin

repeat(5)

begin

#20 mult_a=mult_a+1; mult_b=mult_b+1;

end

end

endmodule

)